通信总线(二)— IIC协议(附工程案例)

1.概述

IIC = Inter Integrated-Circuit 总线是PHLIPS公司推出的一种串行总线,属于半双工通信方式,是具备多主机系统所需的包括总线裁决和高低速器件同步功能的高性能串行总线,它支持多主控(multimastering),其中任何能够进行发送和接收的设备都可以成为主总线。I2C总线只有两根双向信号线。一根是数据线SDA,另一根是时钟线SCL,如下图:

2.内部结构

I2C总线通过上拉电阻(大小由速度和容性负载决定一般在3.3K-10K之间)接正电源。当总线空闲时,两根线均为高电平。连到总线上的任一器件输出的低电平,都将使总线的信号变低,即各器件的SDA及SCL都是线“与”关系。如下图:

每个连接到总线的设备都有唯一的地址,地址为7位,前四位鉴定器件类别,一般是固定的;后三位由器件本身管脚A0、A1、A2可以编程,故同类器件一般最多挂8个。

工作速率如下:

常见的有标准模式100Kbit/s和快速模式400Kbit/s两种,增强快速模式1Mbit/s和高速模式3.4Mbit/s,极速模式单向数据传输速率可达5Mbit/s。

可以实现半双工通信。基于I2C衍生出来的标准有SMBus、PMBus、IPMI、DDC和ATCA等。

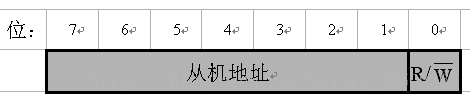

3. 总线寻址

总线明确规定,采用7位寻址字节,D7~D1位组成从机的地址。

D0位是数据传送方向位,为“0”时表示写数据,为“1”时表示读数据。

主机发送地址时,总线上的每个从机都将这7位地址码和自己的地址码比较,如果相同则认为自己被主机寻址,根据读写位确认为发送器或者接收器。

部分规格书中说明地址是8位则分读地址和写地址,即增加了读写位在里面:

极少数情况下有10位寻址的情况;

IIC总线保留地址表如下:

0000 0000 为通用广播地址。

4. 数据传输

(1)数据位有效性规定

I2C总线进行数据传送时,时钟信号为高电平期间,数据线上的数据必须保持稳定,只有时钟信号为低电平时,数据线上的电平才允许变化。如下图:

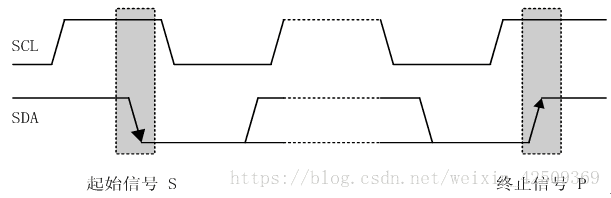

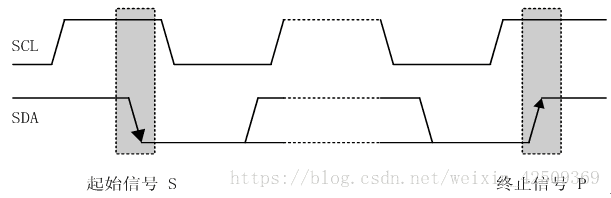

(2)起始信号和终止信号

SCL线为高电平时,SDA线由高变低表示起始信号;

SCL线为高电平时,SDA线由低变高表示终止信号。

起始信号和终止信号均是主机发出;

起始信号产生后,总线处于被占用状态;

终止信号产生后,总线处于空闲状态;

(3)数据传送格式

字节传送与应答

每一个字节必须保证是8位长度。数据传送时,先传送最高位(MSB),每一个被传送的字节后面都必须跟随一位应答位(即一帧共有9位)。如下图:

由于某种原因从机不对主机寻址信号应答时(如从机正在进行实时性的处理工作而无法接收总线上的数据),它必须将数据线置于高电平,而由主机产生一个终止信号以结束总线的数据传送;

如果从机对主机进行了应答,但在数据传送一段时间后无法继续接收更多的数据时,从机可以通过对无法接收的第一个数据字节的“非应答”通知主机,主机则应发出终止信号以结束数据的继续传送;

当主机接收数据时,它收到最后一个数据字节后,必须向从机发出一个结束传送的信号。这个信号是由对从机的“非应答”来实现的。然后,从机释放SDA线,以允许主机产生终止信号。

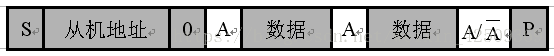

数据帧率格式

IIC总线上的数据包括地址信号和数据信号。在起始信号后必须传送一个从机的地址(7位),第8位是数据的传送方向即读还是写(R=1/W=0),每次数据传送均是主机产生终止信号而结束。

总线的一次数据传输,包括以下几种组合:

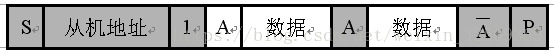

(1)主机向从机发送数据,数据的传送方向在整个传送过程中不变:

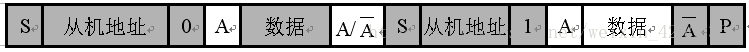

(2)主机在第一个字节后,立即从从机读数据:

(3)在传送过程中,需要改变读写方向时,起始信号和从机地址都得重新一次:

5. 注意事项

加粗样式所有器件的接口均是开漏结构,通过外接上拉电阻实现线与逻辑;

总线上所有设备通过软件寻址(7位或者10位不常见);

每个字节传送均是高位在前面MSB;

如果从机需要延迟下一个数据字节的开始传送时间,可以把SCL电平拉低并保持来强制主机进入等待状态;

总线最大电容值,一般为400pf,高速模式下为100pf;

、

SLC一般情况下不会拥堵在低电平,如果出现这种现象,有硬件复位管脚的话,推荐使用硬件复位;没有的话,推荐使用重新上电方式触发上电复位电路;

SDA拥堵在低电平,主机应发送9个时钟脉冲,那些将SDA拉低的设备在这9个时钟周期内应释放总线。如果没有的话,则需要通过硬件复位或重新上电的方式清除拥堵。

6.手工整理的原理

7.工程代码

这是一个通过IIC传输的数据进而控制电阻大小的硬件实现电路,以下是硬件实现代码,主要是IIC模块

(1)top模块

//AD5243中寄存器的配置程序

module reg_config(

clock_50m,

rst_n,

i2c_sclk,

i2c_sdat

);

input clock_50m ;

input rst_n ;

output i2c_sclk ;

inout i2c_sdat ;

wire sys_rst_n;

reg clock_20k ;

reg [15:0] clock_20k_cnt ;

reg [1:0] config_step ;

reg [3:0] reg_index ;

reg [23:0] i2c_data ;

reg [15:0] reg_data ;

reg start ;

//------------------------------------------

// Delay 100ms for steady state

localparam DELAY_CNT = 23'd100_0000; //50ms 23'd100_0000

reg [22:0] cnt;

always@(posedge clock_50m or negedge rst_n)

begin

if(!rst_n)

cnt <= 0;

else

begin

if(cnt < DELAY_CNT) //1ms

cnt <&

通信总线—IIC协议(附工程案例)1.概述IIC = Inter Integrated-Circuit 总线是PHLIPS公司推出的一种串行总线,属于半双工通信方式,是具备多主机系统所需的包括总线裁决和高低速器件同步功能的高性能串行总线,它支持多主控(multimastering),其中任何能够进行发送和接收的设备都可以成为主总线。I2C总线只有两根双向信号线。一根是数据线SDA,另一根是时钟线SCL,如下图:2.内部结构I2C总线通过上拉电阻(大小由速度和容性负载决定一般在3.3K-10K之间)

通信总线—IIC协议(附工程案例)1.概述IIC = Inter Integrated-Circuit 总线是PHLIPS公司推出的一种串行总线,属于半双工通信方式,是具备多主机系统所需的包括总线裁决和高低速器件同步功能的高性能串行总线,它支持多主控(multimastering),其中任何能够进行发送和接收的设备都可以成为主总线。I2C总线只有两根双向信号线。一根是数据线SDA,另一根是时钟线SCL,如下图:2.内部结构I2C总线通过上拉电阻(大小由速度和容性负载决定一般在3.3K-10K之间)

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

18万+

18万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?