随着技术的发展,IC设计的规模越来越大。系统设计公司为了降低整个系统的成本,提高设计的性能,总是希望把更多的电路集成到单一芯片里,即发展系统芯片(System On Chip,简称SOC)。很多SOC设计,特别是用于便携式系统的IC,不仅要求规模大,性能高,而且要功耗低。

1、层次结构的概念

层次结构在IC设计中广泛使用。现代IC设计中,几乎没有不用层次结构进行设计的。一些大的设计,其逻辑层次可能多达十几层。SOC设计中一般包括设计的再使用和知识产权IP核。SOC设计中包括了多个层次的电路。

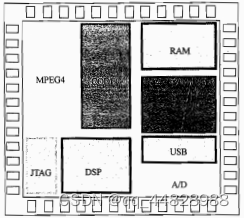

IC设计中,有uP、DSP和内存,有诸如模拟(Analog)电路和射频(RF)电路的积木块(Building Blocks),也有已综合的逻辑电路。已综合的逻辑电路可能包含一些子模块,以此类推。uP、DSP、内存、模拟电路和射频(RF)可称为知识产权IP核。IP核可以以不同的形式集成到IC设计里。一些IP是可以完全地进行综合。我们称可综合的IP核为软知识产权“soft IP核”,软知

识产权核可以很容易地从一种工艺重新映射到另一种工艺。我们也可以根据不同地应用对软知识产权核进行修改。由于软知识产权核地这种灵活性,大部分公司现在在努力做可综合的新IP核。我们称诸如DSP、内存和大部分处理器为硬知识产权核“hard IP”。硬知识产权核通常与某种工艺紧密关联,并做了密度(面积)、速度和功耗的优化。IP核通常已经事先做过验证,我们可以使用IP核加快设计的速度,减少设计错误。

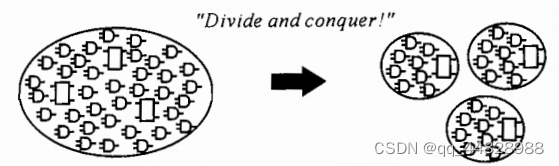

对于设计复杂规模又大的电路,需要对它进行划分(Partitioning),然后对划分后比较简单规模又小的电路作处理(如综合)。这时,由于电路小,处理和分析比较方便简单,容易较快地达到要求。再把已处理好的小电路集成为原来的大电路。

理想情况下,所有的划分应该在写HDL代码前已经计划好。

· 初始的划分由HDL定义好

· 初始的划分可以用Design Compile进行修改

做划分的原因很多,下面是其中的几个原因:

· 不同的功能块(如Memory、uP、ADC、Codec、控制器等等)

· 设计大小和复杂度

· 方便设计的团队管理项目(每个设计工程师负责一个或几个模块)

· 满足物理约束(如用FPGA先做工程样品——Engineer Sample;大的设计可能需要放入多个FPGA芯片才能实现)

1009

1009

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?