//rtl

module fsm(

input clk,

input rst_n,

input start,

input [7:0]data,

output reg[3:0]count_out

);

reg [3:0]cnt;

reg en;

reg [7:0]data_r;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

en <= 1'b0;

else if(start)

en <= 1'b1;

else if(data_r[0] || (cnt == 'd8))

en <= 1'b0;

else

en <= en;

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

cnt <= 'd0;

else if(en)

cnt <= cnt + 1'b1;

else

cnt <= 'd0;

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

data_r <= 'd0;

else if(start)

data_r <= data;

else if(en)

data_r <= {data_r[0],data_r[6:1]};

else

data_r <= data_r;

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

count_out <= 'd0;

else if((data_r[0] || (cnt == 'd8)) && en)

count_out <= cnt;

else

count_out <= count_out;

end

endmodule

//tb

`timescale 1ns/1ns

module fsm_tb;

reg clk;

reg rst_n;

reg start;

reg [7:0]data;

wire[3:0]count_out;

fsm fsm_inst(

.clk (clk ),

.rst_n (rst_n ),

.start (start ),

.data (data ),

.count_out (count_out )

);

initial clk = 0;

always#10 clk = ~clk;

initial begin

rst_n = 0;

data = 8'b1111_1111;

start = 1'b0;

#100;

rst_n = 1;

#1000;

data = 8'b1101_1100;

start = 1'b1;

#20;

start = 1'b0;

#2000;

data = 8'b1101_0000;

start = 1'b1;

#20;

start = 1'b0;

#2000;

data = 8'b0000_0000;

start = 1'b1;

#20;

start = 1'b0;

#2000;

$stop;

end

endmodule

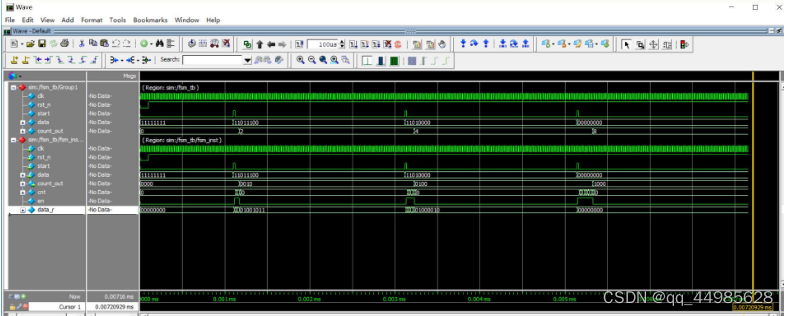

仿真波形图

这篇文章详细介绍了如何使用Verilog HDL设计一个模块fsm,它包含输入时钟、复位信号、启动信号、数据输入以及输出计数器。通过状态机逻辑,模块能够根据输入数据和计数状态进行计数。仿真波形图展示了关键步骤的执行过程。

这篇文章详细介绍了如何使用Verilog HDL设计一个模块fsm,它包含输入时钟、复位信号、启动信号、数据输入以及输出计数器。通过状态机逻辑,模块能够根据输入数据和计数状态进行计数。仿真波形图展示了关键步骤的执行过程。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?