ROM IP核调用实验

1. ROM IP核简介

ROM是只读存储器(read only memory)的简称,是一种只能读出事先所存数据的固态半导体存储器。其特性是一旦存储资料就无法再将其改变或删除,且资料不会因为电源关闭而消失。

2. ROM IP核的配置

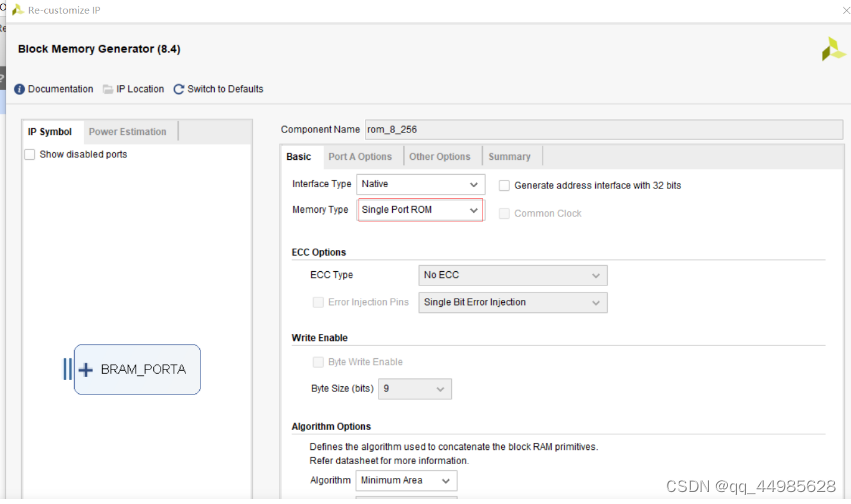

首先点开vivado创建新的工程,点击左侧的IP catalog 搜索block双击打开,basic选项卡的配置如下:

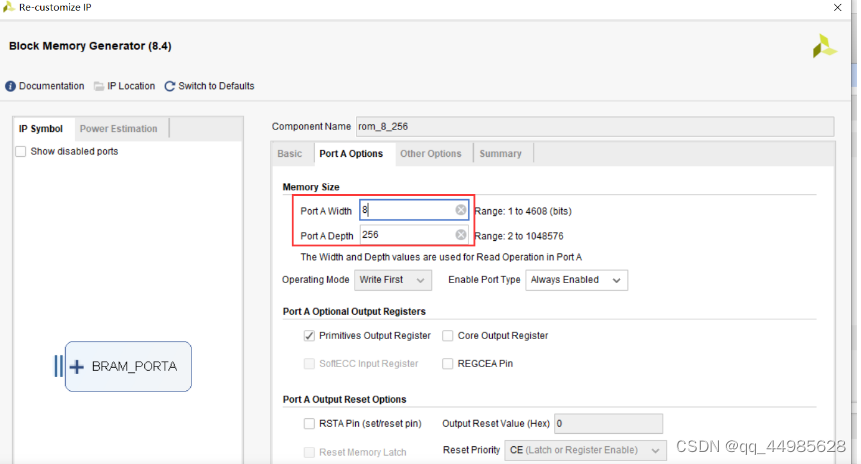

配置成单端口的ROM

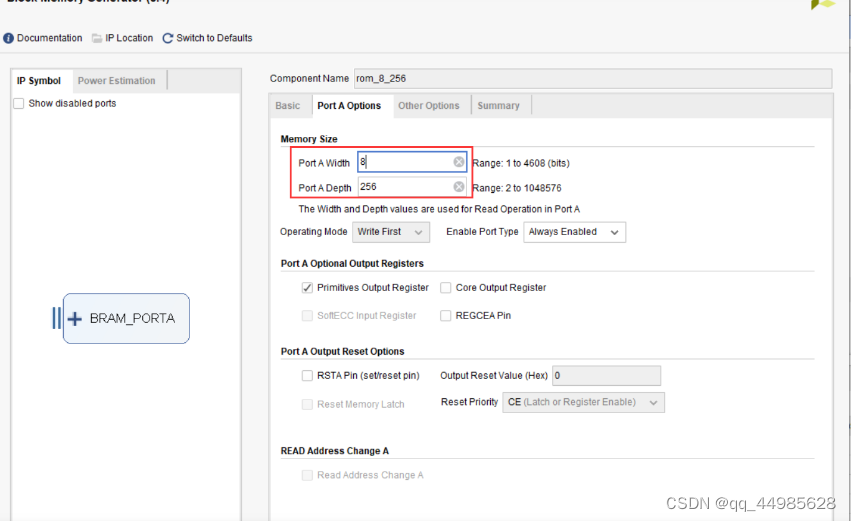

在第二个选项卡中配置端口,设置端口为位宽8、深度256,设置为读优先,时钟使能,其余默认。

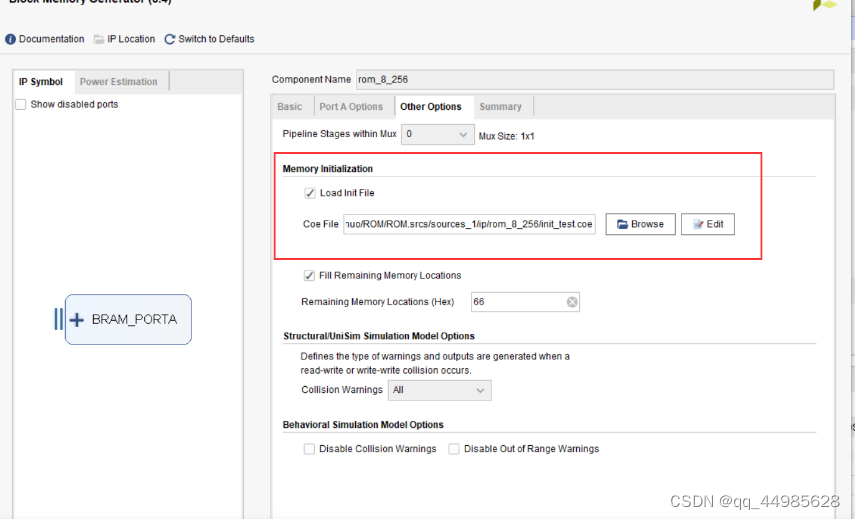

第三个选项卡other options,设置加载初始化文件(.coe),因为ROM是只读存储器,是不能在里面写入数据的,所以在初始化的时候将数据放置进去,再通过读操作读取出来,在源文件中添加自己写的初始化数据,(这个文件可以通过python或者matlab生成,这里由于数据量比较少,所以就手动输入)这里设置为数据的进制(radix)为10,填入的数据为从0到63共64个数据,之前设置的深度为256,所以是足够容纳的,将这个文件放置在对应的IP SRC文件中,在配置IP的界面中将此文件浏览进去即可。

初始化代码:

memory_initialization_radix = 10;

memory_initialization_vector =

0,

1,

2,

3,

4,

5,

6,

7,

8,

9,

10,

11,

12,

13,

14,

15,

16,

17,

18,

19,

20,

21,

22,

23,

24,

25,

26,

27,

28,

29,

30,

31,

32,

33,

34,

35,

36,

37,

38,

39,

40,

41,

42,

43,

44,

45,

46,

47,

48,

49,

50,

51,

52,

53,

54,

55,

56,

57,

58,

59,

60,

61,

62,

63;

其余设置保持默认即可,点击OK即可。

3. ROM IP核的调用

点击+号,添加设计文件,代码如下:

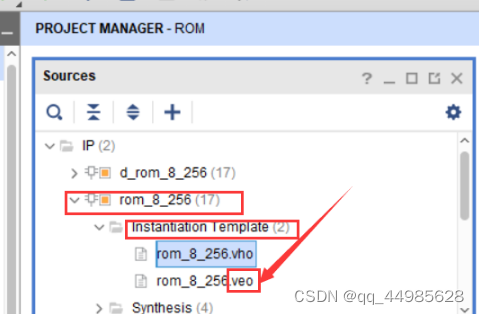

解释:可以在IP Sources中找到veo文件,可以复制ROM IP例化模板,点击复制到刚刚建立的设计文件,可以发现有三个端口需要声明,分别为输入的时钟和地址,以及输出的数据,并定义好地址和数据的位宽为8。

module rom(

input wire sys_clk,

input wire [7 : 0] addra,

output wire [7 : 0] douta

);

//例化单端rom

rom_8_256 rom_inst (

.clka(sys_clk), // input wire clka

.addra(addra), // input wire [7 : 0] addra

.douta(douta) // output wire [7 : 0] douta

);

endmodule

- 仿真文件的设计

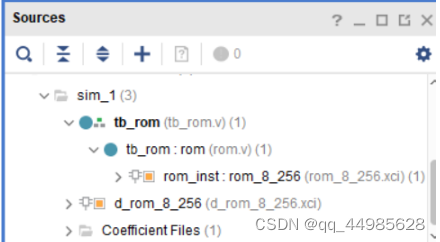

接下来进行最后一步:写仿真文件,点击+号添加仿真文件,将刚刚的设计文件中的端口进行例化,并写上测试的方式,仿真文件的代码如下,保存即可看见IP已经在仿真的层级中。

`timescale 1ns / 1ps

//

// Create Date: 2022/01/31 11:49:47

// Designer Name: linest

// Module Name: tb_rom

// Revision 0.01 - File Created

//

//

module tb_rom( );

reg sys_clk;

reg sys_rst_n;

reg [7 : 0] addra;

wire [7 : 0] douta;

//init sys_clk

initial

begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

#20

sys_rst_n <= 1'b1;

end

//change sys_clk

always #10 sys_clk = ~sys_clk;

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n == 1'b0) begin

addra <= 8'b0;

end

else if (addra == 8'd255) begin

addra <= 8'b0;

end

else begin

addra <= addra + 1'b1;

end

end

//例化

rom tb_rom(

.addra(addra),

.douta(douta),

.sys_clk(sys_clk)

);

endmodule

5. 进行仿真

点击左侧菜单栏中的simulation即可看到仿真结果与设计的想法一致,可以看到输出是相对于地址延时两拍的,这是因为在之前配置IP核的时候添加了输出寄存器(primitive output register),导致延时多了一拍,如果将这个输出寄存器去掉,则输出的数据就会只延时一拍。

本实验基于zedboard、vivado 2018.2实现。

本文详细介绍了如何在Vivado环境下配置和使用ROMIP核,包括设置单端口ROM的参数、配置初始化文件、编写代码实例化及调用ROM,以及创建仿真文件验证功能。重点涉及ROM的配置、地址寻址和数据输出的控制。

本文详细介绍了如何在Vivado环境下配置和使用ROMIP核,包括设置单端口ROM的参数、配置初始化文件、编写代码实例化及调用ROM,以及创建仿真文件验证功能。重点涉及ROM的配置、地址寻址和数据输出的控制。

1451

1451

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?