写在最前,再次感谢北京的亮老师(身份证ID:XXXXXXX)。。。

一、项目概况

项目时钟架构如下:

二、JESD204B模式选取

结合手册,以及所选取FPGA型号的gt线速限制,同时考虑到AD/DA同步性要求,本方案选取L=8、M=2、F=1、S=2模式,因此:

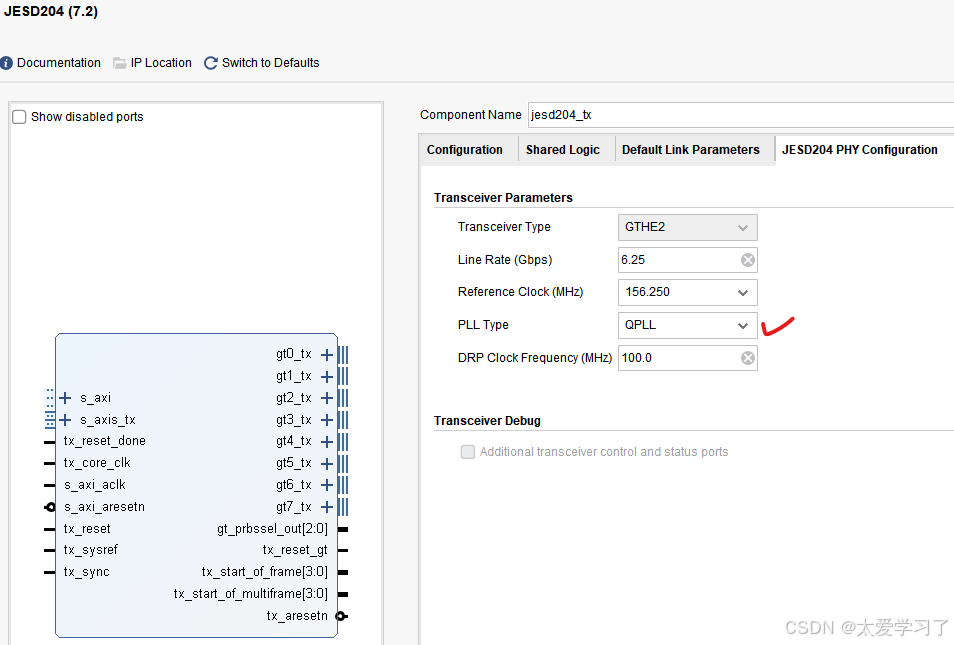

核时钟=fs/div=5000/32=156.25MHz;(也可以用:线速/40)

LMFC=fs/div=5000/256=19.53125MHz。

上图中,线速计算方式见手册如下:

因此,线速=(20*(DACRate)/(InterpolationFactor)*M)/L=20*5/4*2/8=6.25G。注意:所有的线速和时钟都是按照采样率来的。

下两个图,输出给DAC的数据是复数,1路I,1路Q,因此M=2。

三、时钟生成

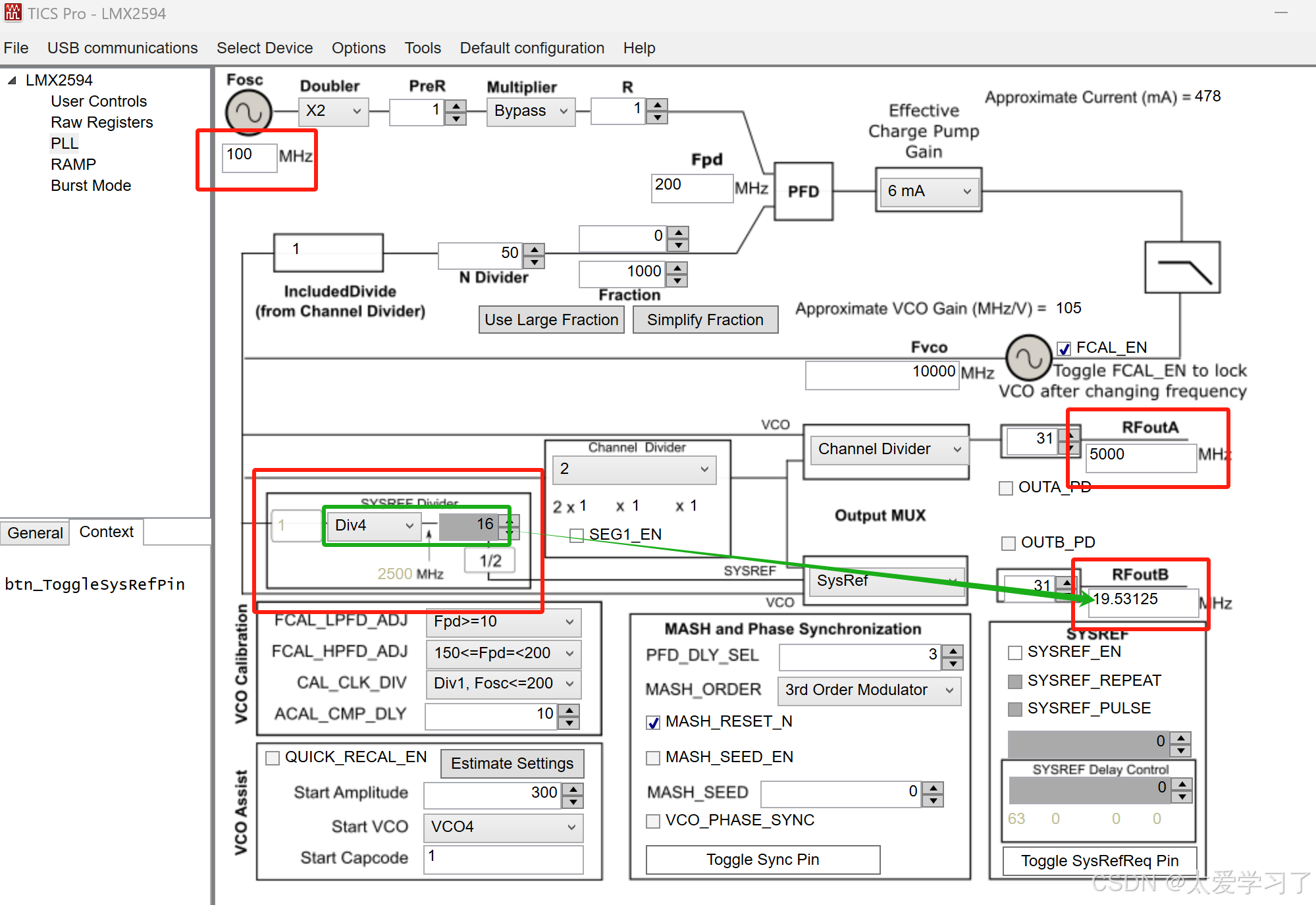

其中,5GHz与19.53125MHz信号由时钟芯片LMX2594产生,打开TICS Pro软件配置如下图所示, 然后到导寄存器表即可。(注意:只要能正常输出想要的频率,且lock是锁定的,里面配成什么样都可以。)

156.25MHz信号由时钟芯片HMC7044产生,参考:LMX2594调试软件TICS PRO的使用

四、工程开发

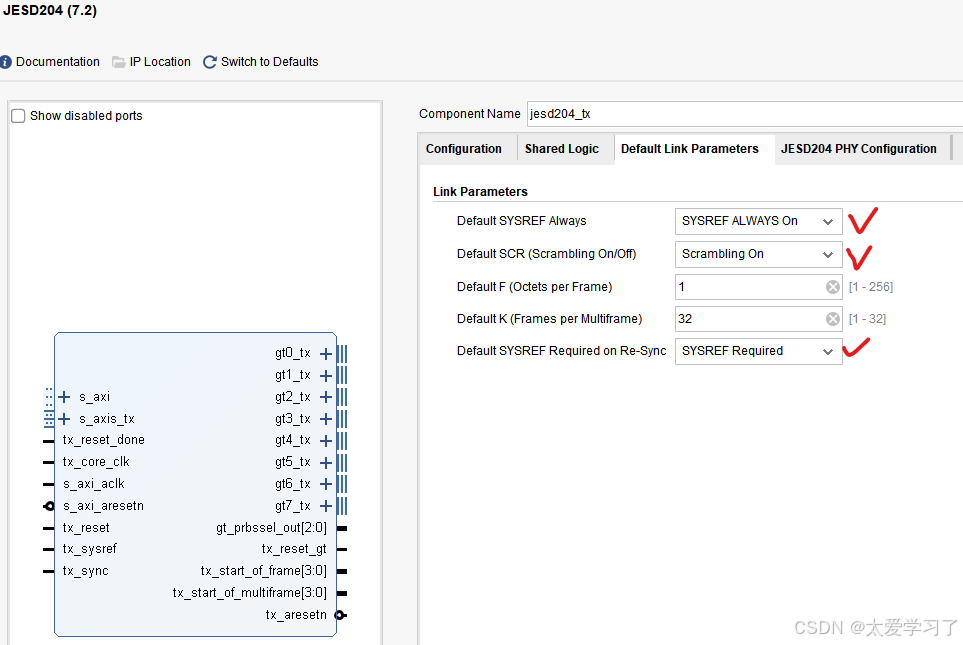

(1)IP设置

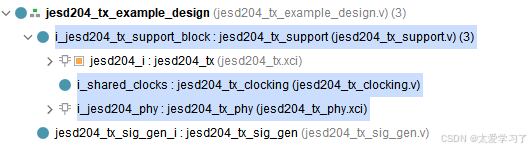

(2)生成案例

右键ip—>open ip example design,并将如下3个文件加入工程。并结合实际应用看看是否需要对文件进行修改(参见:FPGA接口开发之:JESD204B与AD9689通信)。

(3)数据合成

结合手册给出的每条lane采样点,以及上文中配置的JESD204B工作模式,重点注意,在L=8的前提下,M才可以为1或2,为2时必须是IQ数据(M为1时超了fpga型号gt线速)。

结合VIVADO提供的jesd的ip规则,每路gt串转并为32bit,画出逻辑解析图如下:

| lane | 每个采样点数据所在位置(8×32=256bit) | |||

| 1 | data6高8bit | data4高8bit | data2高8bit | data0高8bit |

| 2 | data6低8bit | data4低8bit | data2低8bit | data0低8bit |

| 3 | data7高8bit | data5高8bit | data3高8bit | data1高8bit |

| 4 | data7低8bit | data5低8bit | data3低8bit | data1低8bit |

| 5 | 这里为第二个DAC(Q路数据),在上面第一个ADC(I路数据)基础上整体偏移128bit即可 | |||

| 6 | ||||

| 7 | ||||

| 8 | ||||

(4)实测

配置输出5GHz偏移30MHz的信号,频谱仪观测如下所示,测试通过。

2295

2295

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?