2-1】基本双稳态电路

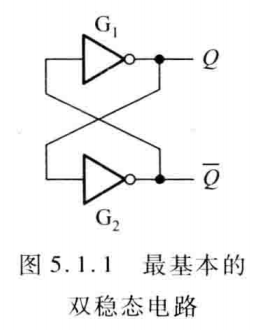

将两个非门G1和G2接成如图5.1.1所示的交叉耦合形式,则构成最基本的双稳态电路。

从图5.1.1所示电路的逻辑关系可知,若 Q=0 ,经非门G2反相,则 Q¯ =1。Q¯反馈到G1输入端,又保证了 Q=0 。

由于两个非门首尾相接的逻辑锁定,因而电路能自行保持在 Q=0 、Q¯=1的状态,形成第一种稳定状态。反之,若 Q=1 ,Q¯=0,则形成第二种稳定状态。在两种稳定状态中,输出端 Q 和Q¯总是逻辑互补的。可以定义 Q=0 为整个电路的0状态, Q=1 则是1状态。

电路进入其中任意一种逻辑状态都能长期保持下去,并可以通过 Q 端电平检测出来,因此,它具有存储1位二进制数据的功能。

像图5.1.1所示电路这样,具有0、1两种逻辑状态,一旦进入其中一种状态,就能长期保持不变的单元电路,称为双稳态存储电路,简称【双稳态】电路。本节所讨论的锁存器即属于双稳态电路。

可以看出,图5.1.1 所示双稳态电路的功能极不完备。在接通电源后,它可能【随机进入】0状态或1状态,因为没有控制机构,所以也无法在运行中改变和控制它的状态,从而【不能作为】存储电路使用。

但是,该电路是各种锁存器、触发器等存储单元的【基础】。

【2-2】SR锁存器

锁存器( Latch )是一种对【脉冲电平敏感】的双稳态电路,它具有0和1两个稳定状态,一旦状态被确定,就能自行保持,直到有外部特定输入脉冲电平作用在电路一定位置时,才有可能改变状态。这种特性可以用于置入和存储1位二进制数据。

常见的SR锁存器可分为以下几种

| 1、基本SR锁存器(或非门) | 2、基本SR锁存器(与非门) |

| 3、门控SR锁存器(普通门) | 4、门控SR锁存器(CMOS门) |

——1)基本SR锁存器(或非门)

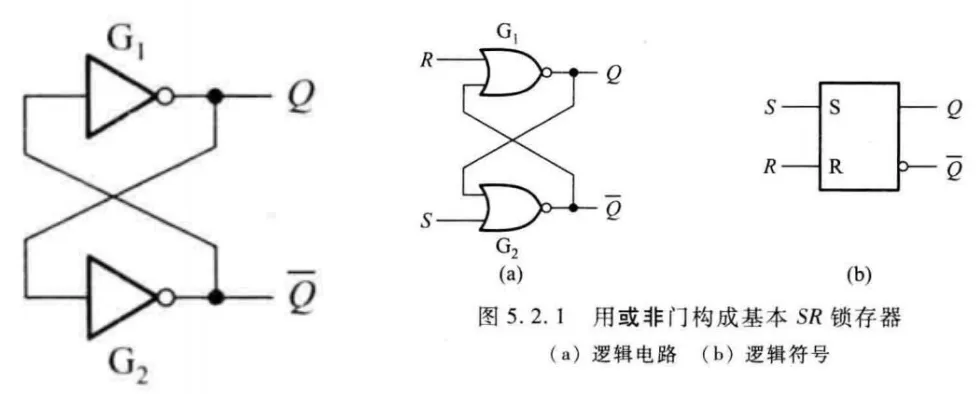

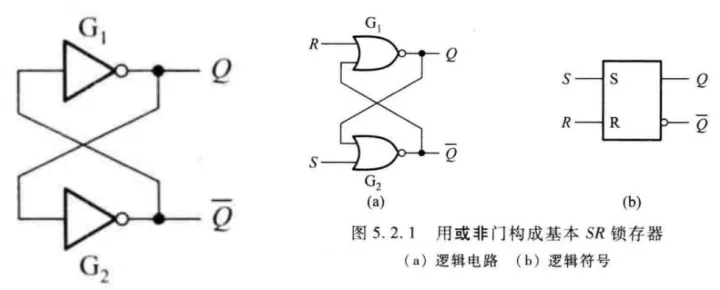

将图5.1.1中双稳态电路的非门换成或非门,则构成图5.2.1(a)所示的基本 SR 锁存器。

它是一种具有最简单控制功能的双稳态电路。图中, S 和 R是两个输入端, Q 和 Q¯是两个输出端。

定义 Q=0 且 Q¯ =1为整个锁存器的 0 状态, Q=1 且Q¯=0则是锁存器的 1 状态。

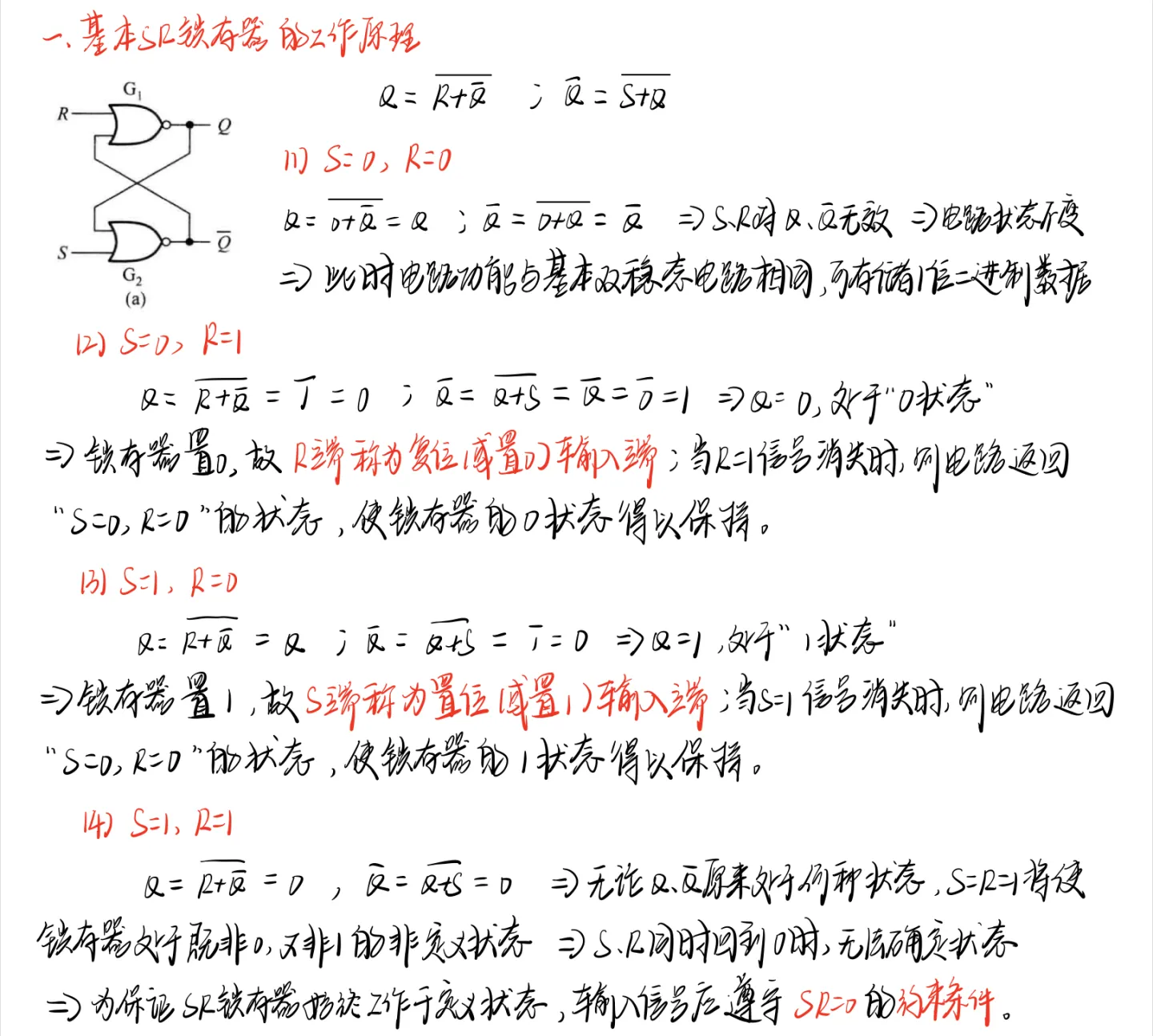

下面根据 、S、R 的4种输入状态组合来分析它的工作原理。

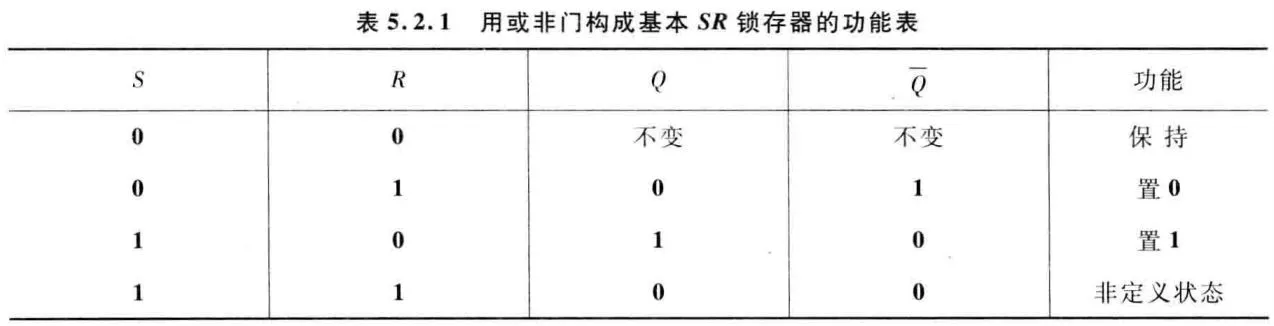

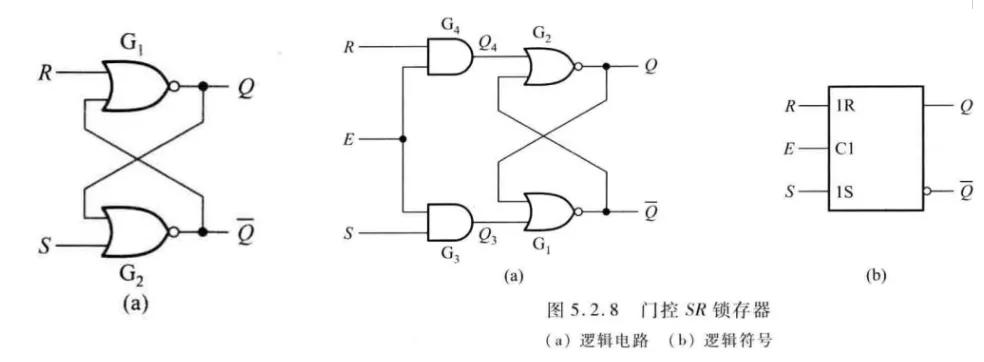

由上述分析可得基本 SR 锁存器的功能表,如表5.2.1所示。表中的4行内容分别对应于上面四种输入输出状态。

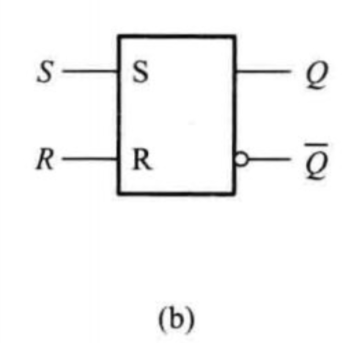

图5.2.1(b)所示为基本 SR 锁存器的逻辑符号,S 和 R 分别为置位端和复位端, Q 和 Q¯ 为互补的两个输出端,其中Q¯输出锁存器的非状态,所以用小圆圈示之。

这样,不通过图5.2.1(a)的逻辑门电路,仅从抽象的逻辑符号也可以理解基本 SR 锁存器各输入、输出信号之间的逻辑关系。

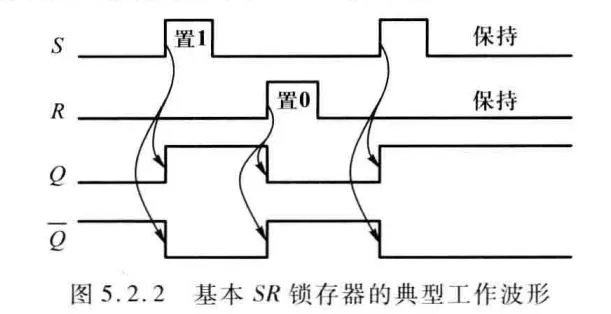

基本 SR 锁存器的数据保持、置0和置1功能,是一个可实际应用的存储单元最基本的逻辑功能。基本 SR锁存器的典型工作波形如图5.2.2所示。

——2)基本SR锁存器(与非门)

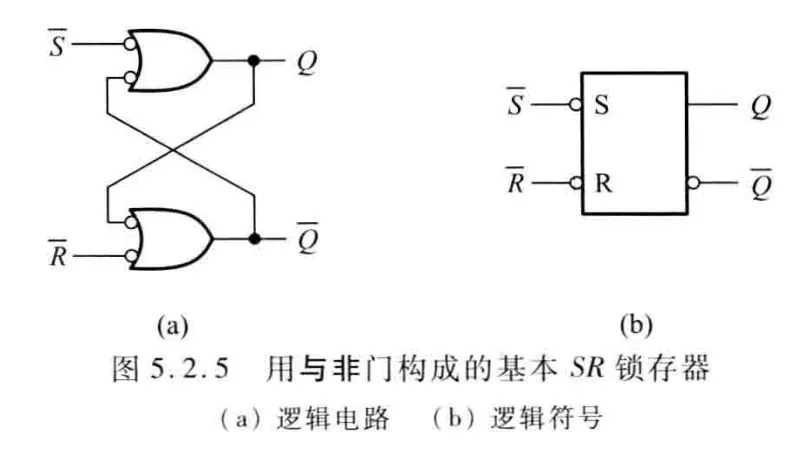

基本 SR 锁存器也可以用与非门构成,其逻辑原理图和逻辑符号如图5.2.5所示。

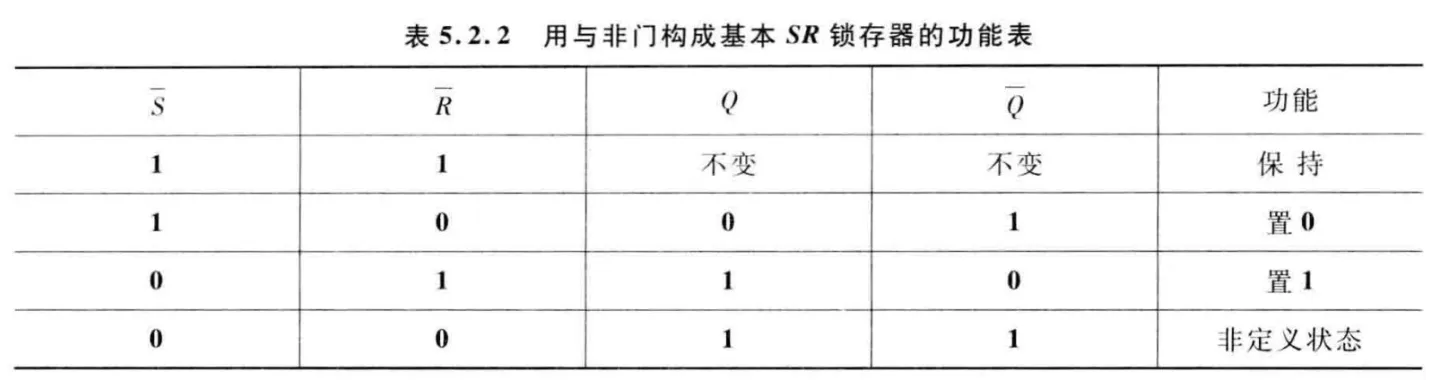

图5.2.5 (a)中的两个与非门是用其等效符号表示的( a¯+b¯=ab¯ ),由图可分析出当 、S、R 为不同输入状态组合时锁存器的状态,如表5.2.2所示。

注意:此处S与R均为“低有效”

当输入为 S¯=R¯=0 时, Q=1 、 Q¯=1 ,该锁存器处于非定义状态,因此工作时应当受到 S¯ + R¯ = SR¯=1 的条件约束,即同样应遵守 SR=0 的约束条件。

与前述或非门构成的基本 SR 锁存器不同,这种锁存器的输入信号S¯和 R¯以逻辑0作为有效作用信号,因而在图5.2.5(b)所示逻辑符号中,在输入端用小圆圈表示。

为了区别,这种锁存器有时也称为基本SR锁存器。

——3)门控SR锁存器(普通门)

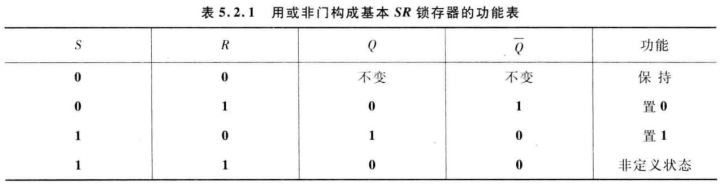

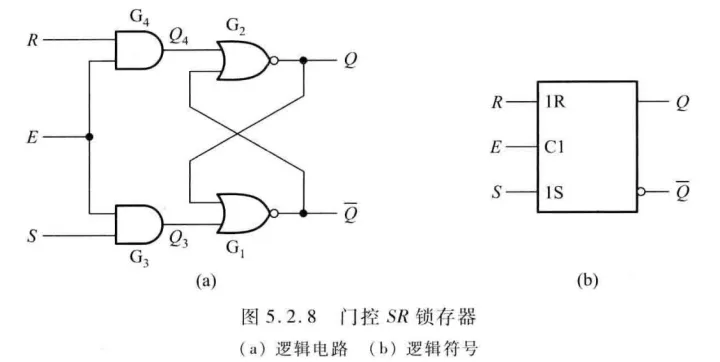

前面所讨论的基本 SR 锁存器的输出状态是由输入信号 S 或 R 直接控制的,而图5.2.8(a)所示电路在基本 SR 锁存器输入端增加了一对逻辑门G3、G4,用使能信号 E 控制锁存器在某一指定时刻,根据 、S、R 输入信号确定输出状态。

这种锁存器称为门控 SR 锁存器。通过控制 E 端电平,可以实现多个锁存器【同步】的数据锁存。

从图5.2.8(a)可以看出,当 E=0 时, Q3=Q4=0 , 、S、R 端的逻辑状态不会影响到锁存器的状态;当 E=1 时, 、S、R 端的信号被传送到基本 SR 锁存器的输入端,从而可确定 Q 和 Q¯ 端的状态,其功能与表5.2.1一致。

若 E=1 时输入信号 S=R=1 ,则Q=Q¯=0,锁存器将处于非定义的逻辑状态。当 E 恢复为0时,由于Q3、Q4同时回到0,将不能确定锁存器的状态。

因此,应用这种锁存器必须更严格地遵守 SR=0 的约束条件。由于约束条件造成的应用限制,因而很少有独立的门控 SR 锁存器产品。但是,在许多中、大规模集成电路中时常应用这种锁存器,或用它构成触发器或存储器。所以, SR 锁存器仍是重要的基本逻辑单元。

图5.2.8(b)所示是门控 SR 锁存器的逻辑符号。其方框内用 C1 和 1R 、 1S 表达内部逻辑之间的关联关系。

C 表示这种关联属于控制类型,其后缀用标识序号"1"表示该输入的逻辑状态对所有以"1"作为前缀的输入起控制作用。这里因置位和复位输入均受 C1 的控制,故 S 和 R 之前分别以标识序号"1"作为前缀。图5.2.8(b)中所示的两个输出端 Q 和 Q¯ 其意义与图5.2.1(b)所示基本 SR 锁存器相同。

——4)门控SR锁存器(CMOS门)

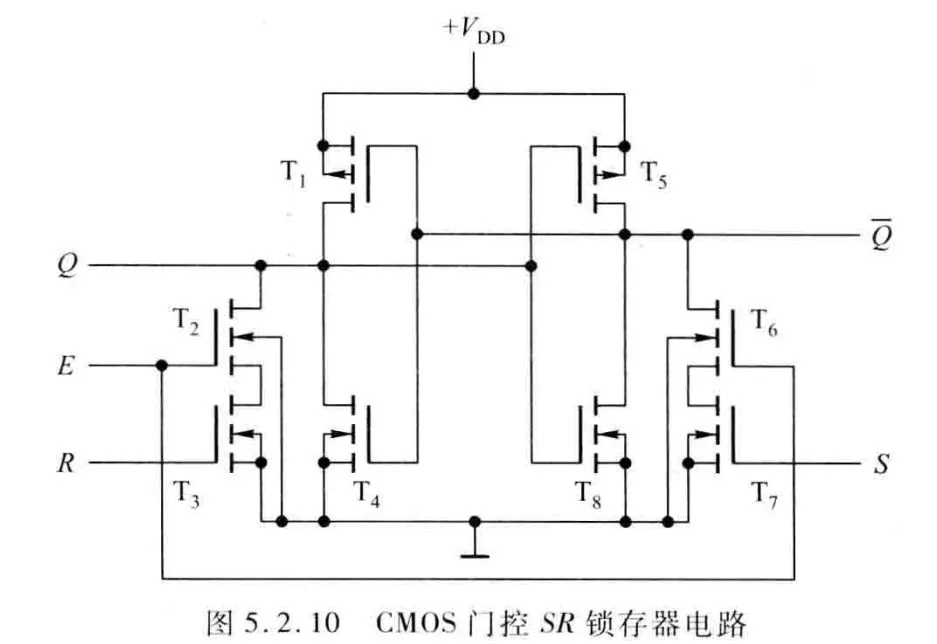

图5.2.10 所示是一种 CMOS 集成电路中常用的门控 SR 锁存器晶体管级电路。

它仅用6个 NMOS 管和两个 PMOS 管便实现了图5.2.8(a)所示的两个与门和两个或非门的逻辑功能,而没有使用标准 CMOS 门电路,从而省却了一些 PMOS 晶体管。

由于一般 CMOS 与或非门中的 PMOS 管占据芯片的面积远大于相应的 NMOS 管,所以图5.2.10所示电路的简化有效缩小了锁存器在集成电路芯片中所占的空间。

在正常逻辑状态下,该电路只在状态转换瞬间存在一定的工作电流,静态功耗极微。但需要注意,如果在 E=1 的同时 S=R=1 ,则 T1∼T3 和 T5∼T7 均处于导通状态,将使电路功耗剧增。因此,在集成电路结构设计时就必须考虑到严格遵守 SR=0 的约束条件,保证在任何时候都不出现 S=R=1 的情况。

【2-3】D锁存器

与 SR 锁存器不同, D 锁存器在工作中不存在非定义状态,因而得到广泛应用。

目前, CMOS 集成电路主要采用传输门控 D锁存器和逻辑门控 D 锁存器两种电路结构形式,特别是前者电路结构简单、在芯片中占用面积小而更受青睐。

——1)传输门控 D锁存器

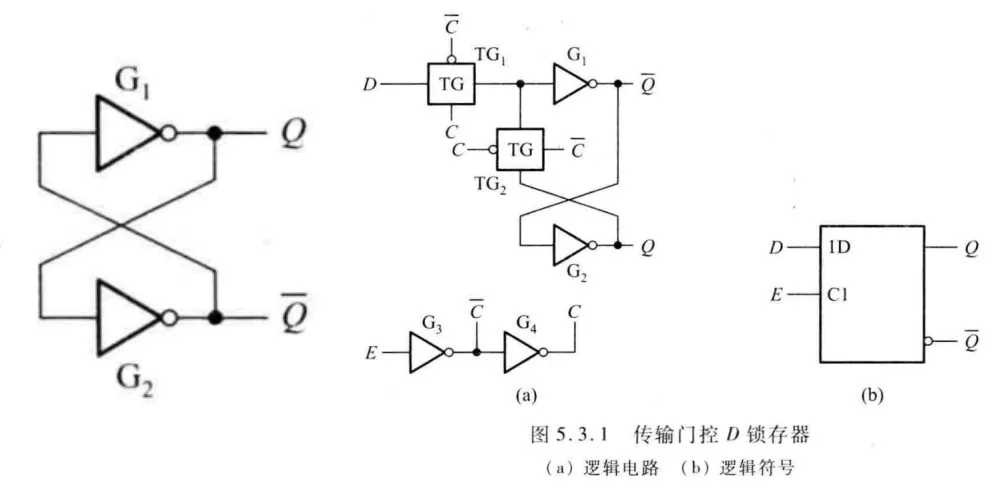

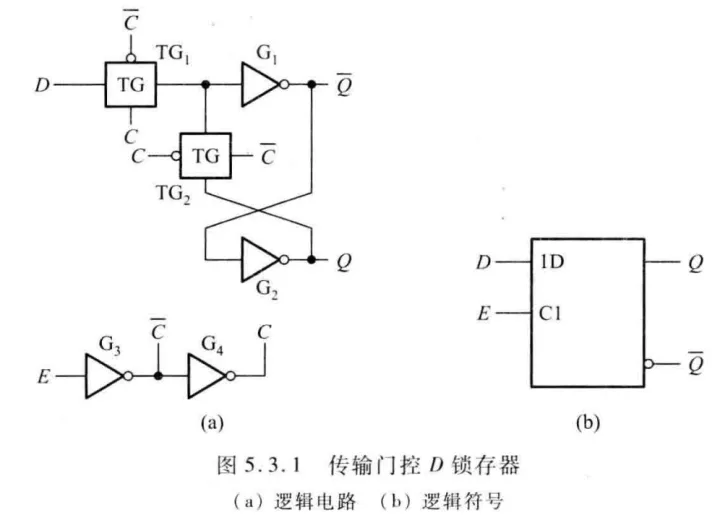

在图5.1.1的双稳态电路中插入两个传输门TG1和TG2,则可构成如图5.3.1(a)所示的传输门控 D锁存器,图5.3.1(b)所示是它的逻辑符号。

锁存器有两个输入端∶使能端 E 和数据输入端 D 。

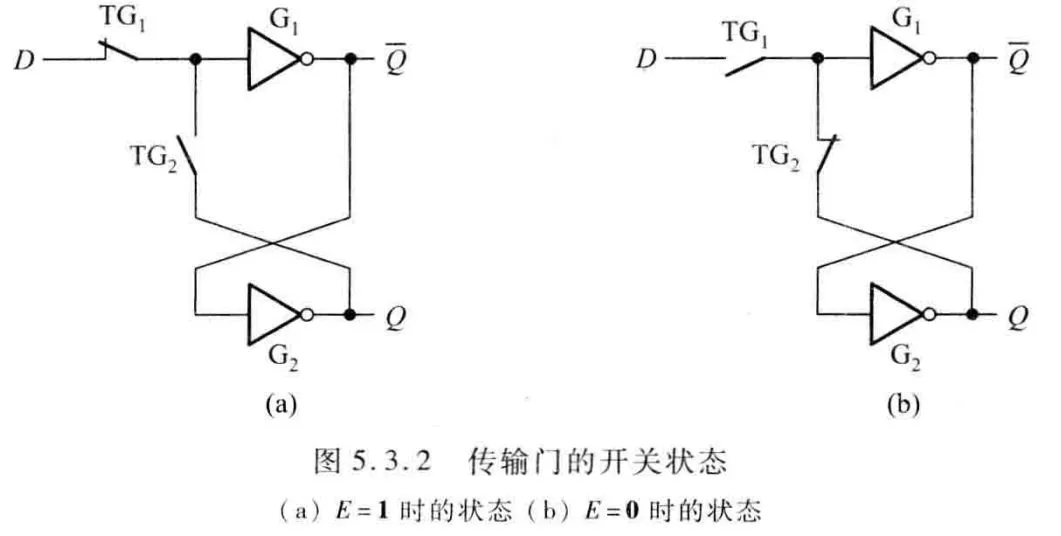

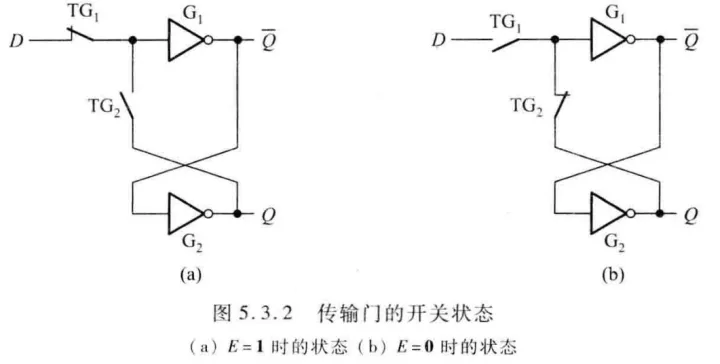

当 E=1 时, C¯=0 , C=1 ,TG1导通,TG2断开,如图5.3.2(a)所示。

输入数据 D 经 G1 、 G2 两个非门,使 Q=D , Q¯=D¯ 。显然,这时 Q 端跟随输入信号 D 的变化。

当 E=0 时,C¯=1 , C=0 ,TG1断开,TG2导通,如图5.3.2(b)所示,其原理与图5.1.1所示双稳态电路相同。

由于G1 、 G2输入端存在的分布电容对逻辑电平有暂短的保持作用、在两个传输门状态转换瞬间并不影响电路的输出状态。之后,电路将被锁定在 E 信号由1变0前瞬间 D 信号所确定的状态,在 E=0 的条件下可保持锁存器状态不变,使1位二进制数据得以存储。

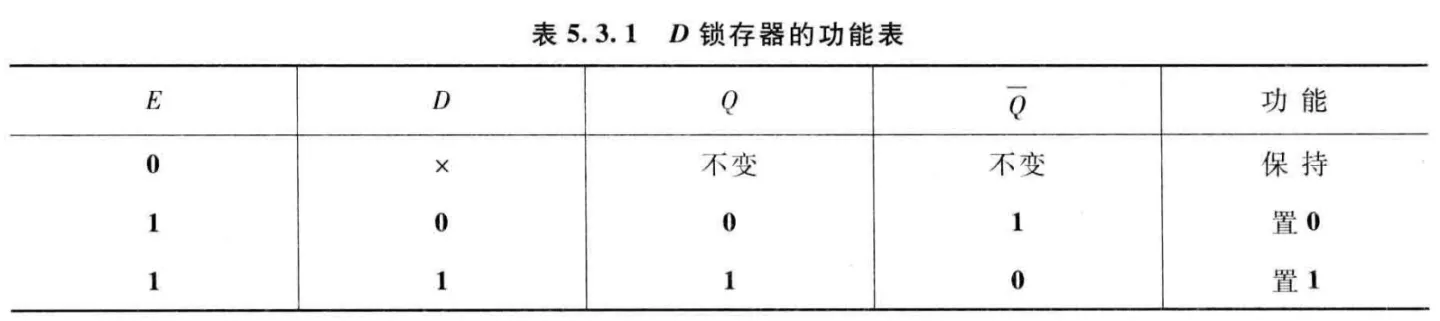

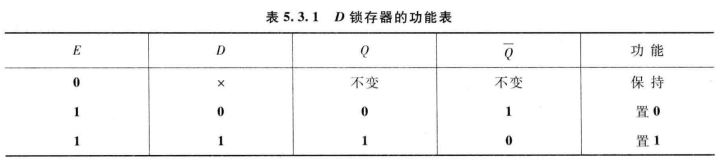

表5.3.1概括了 D 锁存器的功能。由于这种锁存器在 E=1 时 Q 端可跟随 D 端的逻辑状态变化,故又称为透明锁存器。

——2)逻辑门控D锁存器

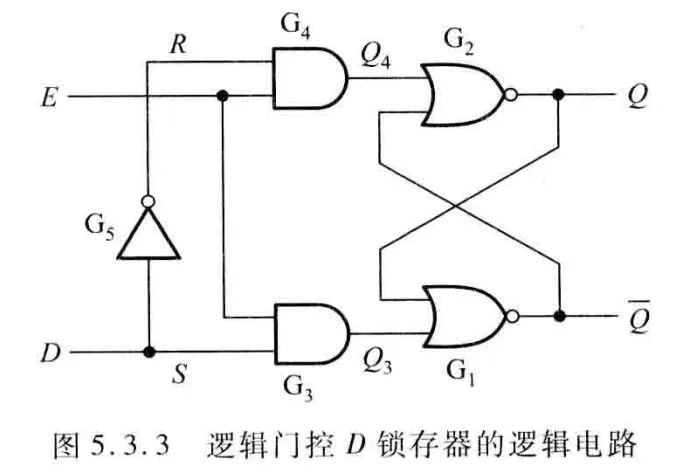

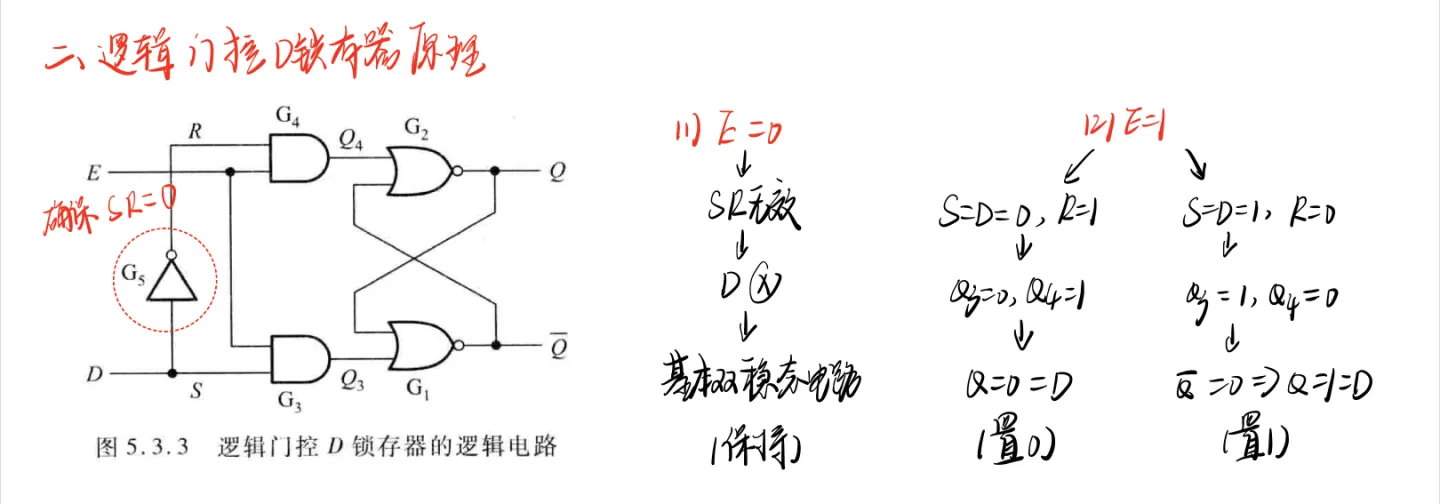

图5.3.3所示为逻辑门控 D 锁存器的逻辑电路,它在门控 SR 锁存器的 S 和 R 输入端之间连接了一个非门G5,从而保证了 SR=0 的约束条件,消除了可能出现的非定义状态。

逻辑门控 D 锁存器的原理分析如下:

由上述分析可知,图 5.3.3 所示电路的逻辑功能与表5.3.1描述的一致。

又由于它的逻辑功能与传输门控 D 锁存器完全相同,所以逻辑符号亦相同。

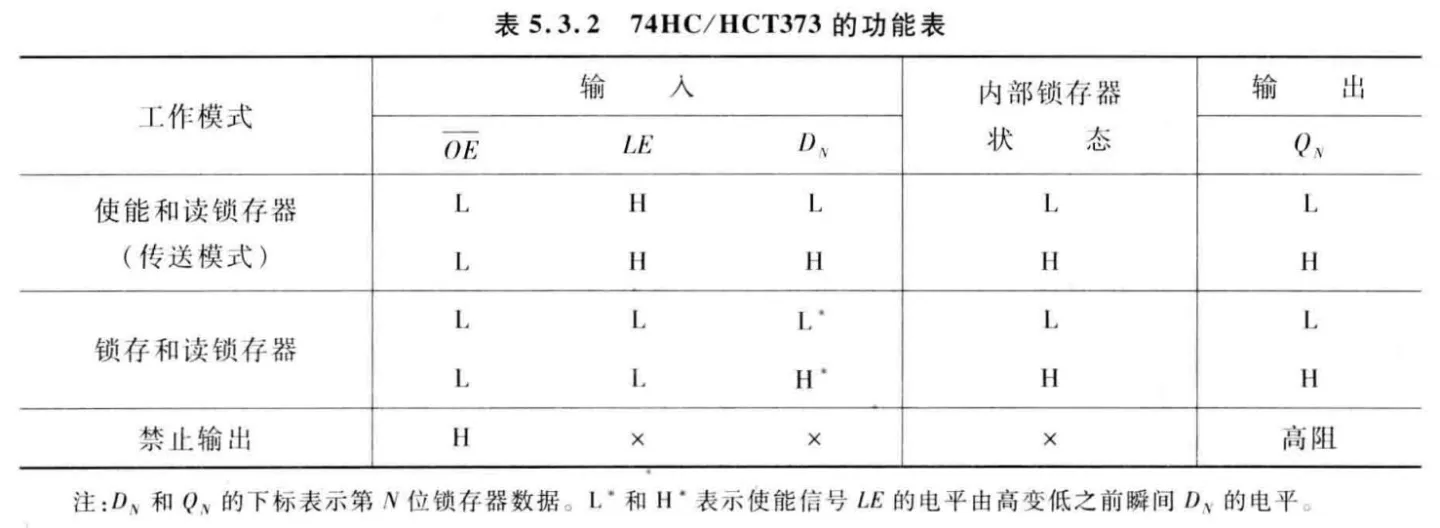

——3)74HC/HCT373(8D锁存器)

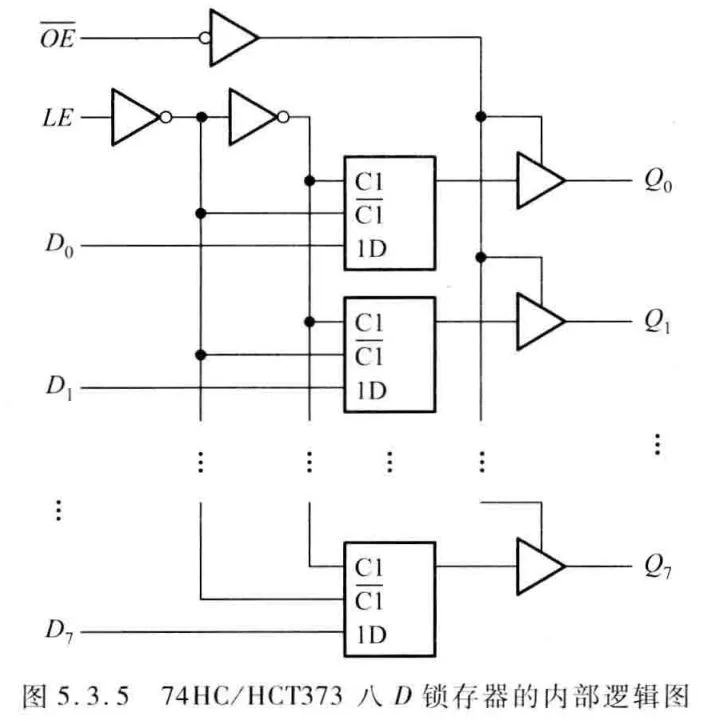

图5.3.5为中规模集成的 CMOS 八 D 锁存器 74HC/HCT373 的内部逻辑图,其核心电路是8个如图5.3.1(a)所示的传输门控 D 锁存器。

8个锁存器共用同一对互补的传输门控制信号 C 和 C¯ ,这对信号又由锁存使能信号LE 所驱动。

当 LE 为高电平时,允许各 D 锁存器的输出跟随相应输入信号的变化; LE 为低电平时则保持状态不变。

8个 D 锁存器输出端都带有【三态门】,当输出三态门使能信号 OE¯ 为低电平时,三态门有效,输出锁存的信号;当 OE¯ 为高电平时,输出处于高阻状态。

这种三态输出电路,一方面提高了对负载的驱动能力,在锁存器与输出负载之间起到隔离作用,避免因负载变化而影响锁存器的动态特性;更重要的是使 74HC/HCT373 可以方便地应用于微处理机或计算机的总线传输电路。

根据LE 和OE¯的不同逻辑电平, 74HC/HCT373 可分为三种工作模式∶

| ①使能和读锁存器 (传送模式) | ②锁存和读锁存器 | ③禁止输出 |

表5.3.2 所示为其功能表。

【2-4】锁存器的动态特性

——1)基本SR锁存器的动态特性

此前的讨论仅考虑了电路的逻辑关系,没有涉及门电路输出信号对输入信号的【时间延迟】,即电路的【动态特性】,而构成图5.2.1(a)所示电路的两个或非门在工作时都存在一定的【传输延迟】。

当输入信号 S 或 R 变为高电平后,输出信号 Q 或 Q¯ 需要经过一定延迟才会产生变化。

这种延迟有时会影响到被其驱动的后续电路的动作,可能造成错误的逻辑输出或出现工作不稳定的情况。 此外,为保证锁存器状态可靠转换,对输入信号也需要有一定的时间要求。

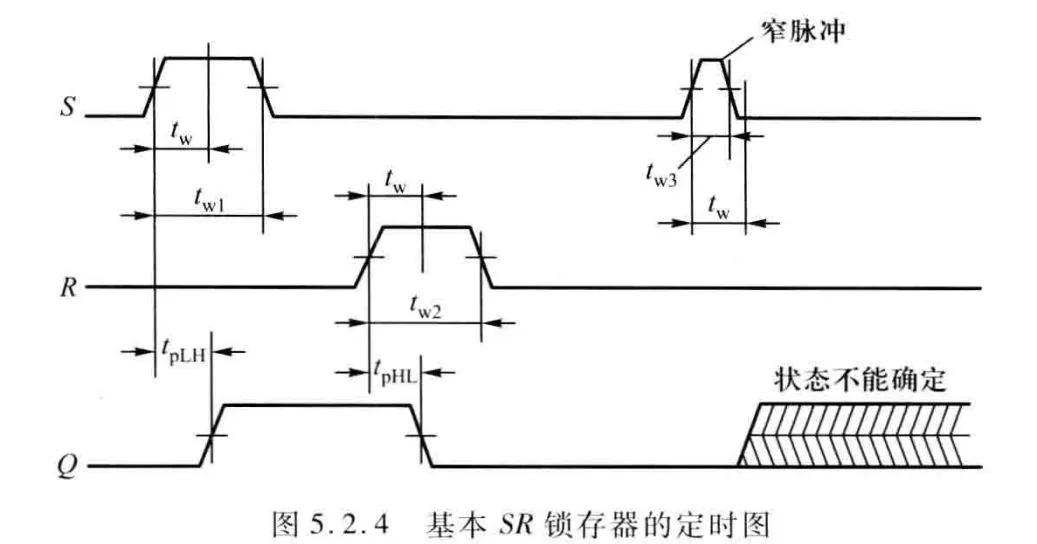

定时图是表达时序电路动态特性的工具之一,它表达了电路动作过程中,输出对输入信号响应的延迟时间,以及对各输入信号的时间要求。图5.2.4是基本 SR 锁存器的定时图。

图中,脉冲信号的上升沿和下降沿均用斜线表达,表示存在一定的上升时间和下降时间,脉冲沿的【基准时间】定位在上升沿和下降沿的 50%。

传输延迟时间 tpLH 和tpHL

如图5.2.4所示,当置1信号 S 上升为高电平时,需要一定的传输延迟时间tpLH之后, Q 端才转换为高电平。同样,置0信号 R 作用于电路, Q 端电平也经一定的传输延迟时间 tpHL 才变化为0。 Q¯ 端的变化相对于输入信号 S 或 R 的变化也存在一定的传输延迟。

这里,把tpLH和tpHL定义为基本 SR 锁存器的传输延迟时间。对于具体电路,由于信号通过的路径不同,tpLH和tpHL一般不完全相等。

脉冲宽度 tw

基本 SR 锁存器工作时,必须保证 S 和 R 的高电平脉冲宽度不小于某一最小值tw。

例如,图5.2.4中的tw1和tw2均满足要求,从而电路能可靠地实现翻转。如果加在 S 或 R 端的脉冲宽度过窄,如图5.2.4所示宽度为tw3的【窄脉冲】,在 Q 端电压尚未越过逻辑阈值电平时, S 端的高电平就被撤除,电路可能又回到原来的状态,或者使Q的最终状态不能确定。

所以基本 SR 锁存器应用中要求输入信号 S 和 R 的脉冲宽度必须不小于一个最低限值tw,才能保证在 S 或 R 脉冲作用之后有确定的状态。

——2)D锁存器的动态特性

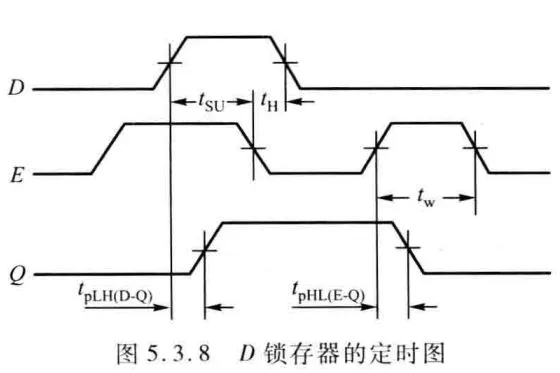

图5.3.8所示是 D 锁存器的定时图,对于传输门控和逻辑门控两种电路结构的 D 锁存器都是适用的,只是具体参数值有所差异。下面对各参数进行说明。

(1)传输延迟时间 tpd

tpd是输出信号对输入信号的响应延迟时间,对于 D 锁存器则是指 D 信号和 E 信号共同作用后, Q (或 Q¯ )端响应的延迟时间。

图5.3.8中所示 tpLH(D−Q) 是输出 Q 从低电平到高电平对 D信号的延迟时间, tpHL(E−Q) 则是 Q 从高电平到低电平对 E 信号的延迟时间。

根据不同的输入状态,还存在图中没有显示的tpLH(E−Q)和tpHL(D−Q)。对于 CMOS 集成电路,因为输出信号对各输入信号的延迟相差不多,有时统一以 tpHL 和 tpLH 表达,更经常的是取平均传输延迟时间∶

(2)建立时间tSU

信号 D 的逻辑电平必须在使能信号 E 下降沿到来之前建立起来,才能保证正确地锁存。

tSU 表示 D 信号对 E 下降沿的最少时间提前量。

(3)保持时间tH

在 E 电平下降后, D 信号不允许立即撤除,否则不能确保数据的锁存。

tH 表示 D 信号电平在 E 电平下降后需要继续保持的最少时间。

(4)脉冲宽度 tw

为保证 D 信号正确传送到 Q 和 Q¯ ,要求 E 信号的脉冲宽度不小于 tw 。

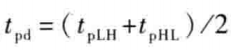

上述 tSU 、 tH 和 tw 是对输入信号的时间要求。如果电路运行中达不到要求,则会分别出现如图5.3.9所示的情况,可能导致 D 锁存器不确定的逻辑输出。

(a)tSU 表示 D 信号对 E 下降沿的最少时间提前量。此处 tSU′<tSU ,因此无法保证正确的锁存;

(b) tH 表示 D 信号电平在 E 电平下降后需要继续保持的最少时间。此处 tH′<tH ,因此无法保证正确的锁存;

(c)为保证 D 信号正确传送到 Q 和 Q¯ ,要求 E 信号的脉冲宽度不小于 tw 。此处 tw′<tw ,因此因此无法保证正确的数据传送。

本文详细介绍了双稳态电路的基础知识,包括基本的SR锁存器和D锁存器的工作原理、逻辑功能及动态特性。重点讨论了SR锁存器的4种状态和D锁存器的传输延迟、建立时间、保持时间等关键参数,阐述了它们在数据存储和时序电路中的应用。同时,提到了门控SR锁存器和D锁存器的电路结构,以及在实际应用中应注意的信号延迟和时间要求问题。

本文详细介绍了双稳态电路的基础知识,包括基本的SR锁存器和D锁存器的工作原理、逻辑功能及动态特性。重点讨论了SR锁存器的4种状态和D锁存器的传输延迟、建立时间、保持时间等关键参数,阐述了它们在数据存储和时序电路中的应用。同时,提到了门控SR锁存器和D锁存器的电路结构,以及在实际应用中应注意的信号延迟和时间要求问题。

2419

2419

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?