V oltage Drop-based Fault Attacks on FPGAs using Valid Bitstreams论文笔记

摘要

背景+现有存在问题由于FPGA在许多关键应用领域的广泛应用,其安全性备受关注。

在最近的系统中,例如云端FPGA或Systemson芯片(SoC),用户甚至可以远程访问可重新配置的结构以实现定制加速器。这种访问可以通过恶意使用FPGA结构在整个系统中暴露新的安全漏洞。在过去,对电源级别的攻击需要本地访问硬件。

**现有存在问题+我们的工作(创新点):**在本文中,我们揭示了FPGA中的一个安全漏洞,该漏洞允许有效配置产生严重的电压波动,从而在几微秒内使FPGA崩溃。由于此漏洞可能导致使用基于FPGA的加速器的系统受到严重的安全攻击,我们还分析了其潜在机制,并讨论了缓解的可能性。

前言

- 先讲解了FPGA应用背景,举例证实FPGA的应用越来越广泛

- 然后讲述了这些应用趋势也产生了新的安全问题,阐述了以前的安全问题(引用)和新的安全问题是如何产生的

- 我们的工作(创新点:本文揭示了FPGA在电气级别上的此类安全漏洞),然后详细阐述了 该漏洞所需要的条件,实验结果,对比传统漏洞更恶意在哪。最后总结重点本文的重点是全面分析该漏洞及其总体影响。我们分析了系统崩溃的确切条件,以及系统如何再现。此外,我们还为可能缓解这一漏洞提供了初步分析和指导。)

电路设计和实验装置

III-A节中解释电压波动传感器在FPGA中的实现。

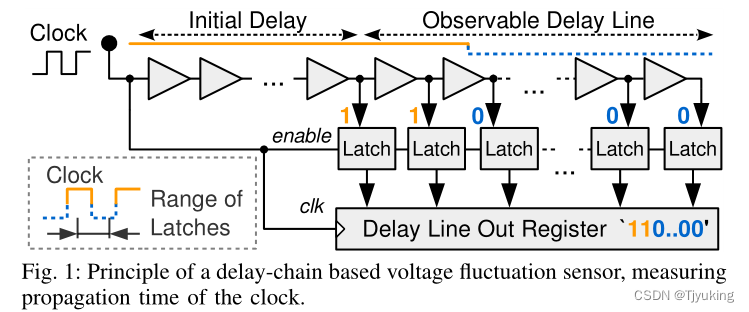

用于V电压波动分析的延迟传感器,该传感器的概念。它显示了一条延迟线,简化为一条缓冲链。在这些缓冲器之间,连接了锁存器,这些锁存器使用相同的时钟信号启用。

第III-B节中解释如何通过RO产生电压降。

当需要自发的高电流时,可以故意引起电压降。使用具有适当定时的高开关活动来导致PDN上的过大电流和由此产生的负载。

第III-C节中详细介绍了基于电压紧急情况的攻击原理及其实验设置。

我们启用和禁用RO以快速连续地产生压降脉冲,这意味着它们在一定时间内振荡,在另一时间内被停用,我们称之为RO切换频率fRO−t。

下文描述基于固定数量的RO。

在测试fRO−t的不同频率时,需要考虑到最坏的临界情况需要一段时间才能形成。当在ML605板上简单启用RO时,从路径延迟增加开始到达到最低点并再次开始恢复,大约需要10−20µs,如图2所示。这意味着,我们应该保持RO振荡,直到它们引起足够高的电压降,并在电压开始恢复之前重新启动。因此,减少fRO−t将更有效地使FPGA崩溃,直到恢复范围(<25−50 kHz)。

结果和讨论

在下面的小节中,我们将暴露前面提到的漏洞,这些漏洞可用于这些设备中的DoS。我们将首先在第IV-A节中分析崩溃所需的条件,然后在第IV-B节中解释根本原因。在第IV-C节中,我们将展示使用基于延迟线的传感器检测电压降是否足够快,以防止其发生,并讨论停止导致崩溃的活动的不同可能性

A崩溃所需条件

B攻击分析

对于定时故障或SRAM状态保持损失,电压紧急情况所需的时间Tt和幅度Vdrop是不同的,在这种情况下,当以正确的频率施加压力时,配电网络可能会有弱点。

主要是对实验现象的一种描述

总之,崩溃的永久性取决于稳压器崩溃或出于安全原因关闭。这种情况反过来又直接由PDN中的谐振引起,或者由FPGA的逻辑和配置存储器中的其他问题引起。更多细节将在未来的工作中进行分析。

C讨论

故意导致DoS的电压紧急情况的性质,如果能在过度的开关活动升级为整个芯片的电压紧急情况之前,检测并禁用过度开关活动,这样的威胁可能会减少。

在另一个实验中,我们展示了在检测到低于“30”的传感器值后,当禁用所有RO时,电压恢复的速度有多快。通过这种方式,我们可以估计传感器的延迟以及电压降的衰减速度。

未来:

为了防止恶意比特流加载,可以在软件中对其进行健全性检查,其挑战是保持合法比特流正常工作,但不会为恶意比特流留下漏洞。最近的FPGA工具已经用作默认约束的一个选项是在比特流生成过程中检查组合循环,用户可以禁用该循环。因此,检查需要在用户或应用程序开发人员无法访问的特权系统软件级别进行。

对于所有这些可能性,需要进行新的实验。

为了能够足够快地停用任意恶意电路,可能需要制造新的FPGA。

结论

现有研究问题:

FPGA越来越广泛地被用作用户定义的加速器,例如在云中或集成在SoC中。在这些新的使用场景中,像比特流加密这样的经典安全实施方式变得不可行,使得它们容易受到新的安全威胁。

本文主要内容:

在本文中,我们通过展示一种系统方法来崩溃两代FPGA和包含FPGA的SoC,揭示了这样一个安全漏洞,这可能导致这些系统中的拒绝服务威胁。此外,我们还讨论了如何实施适当的缓解措施以防止拒绝服务。

实验现象和机理:

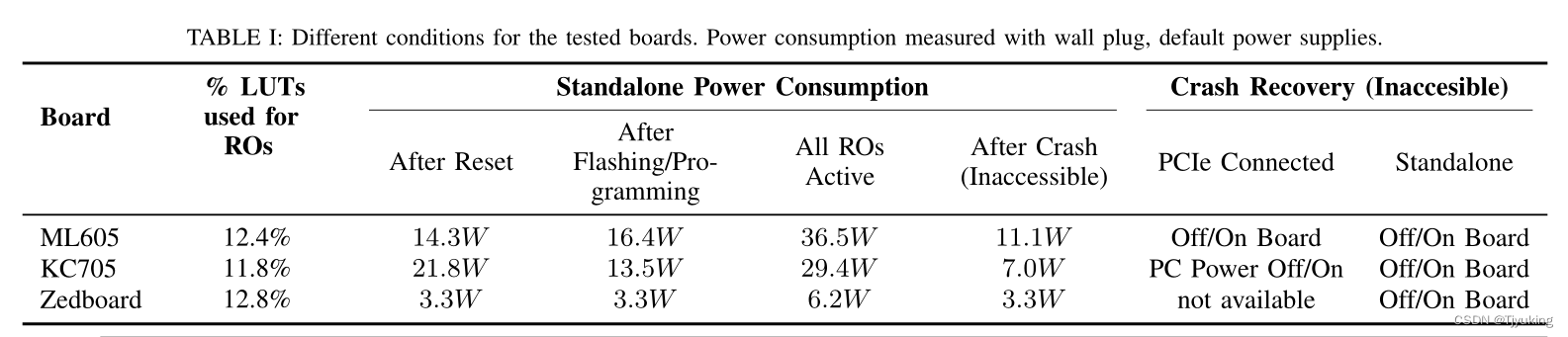

这种拒绝服务是由给定位流级访问时的特定配置引起的,并且只需要测试FPGA中可用LUT资源的大约12%。此类漏洞可允许对数据中心、SoC和其他应用程序域中使用的FPGA进行攻击,在这些域中,整个系统需要重新启动,甚至完全断开电源,以便重新启动崩溃的FPGA。

6728

6728

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?