基于FPGA的云基础设施拒绝服务

作者:Tuan La, Khoa Pham, Joseph Powell and Dirk Koch

机构:The University of Manchester, UK

联系方式:tuan.la@postgrad.manchester.ac.uk

[khoa.pham,joseph.powell,dirk.koch]@manchester.ac.uk

专业词汇:

CSP(cloud service provider) 云服务提供商

AFI :全称为Amazon FPGA Image,本质是FPGA的比特流配置文件。

EBS: Elastic Block Store 弹性块存储

MELT:Malicious Electrical Level Threats 恶意电气级威胁

DCP:the vendor propriety design checkpoint format (DCP).设计检查点格式

摘要

本文介绍了通过power-hammering在电气级别针对A WS F1实例的FPGA的攻击

演示了通过F1实例上实现的所有AWS安全围栏(包括FPGA供应商DRC)的不同的power-hammering攻击,

最重要的是,我们提供了一个FPGA病毒扫描框架,该框架经过改进,以支持大型数据中心FPGA来防止此类攻击,包括几乎所有当前的侧通道攻击。

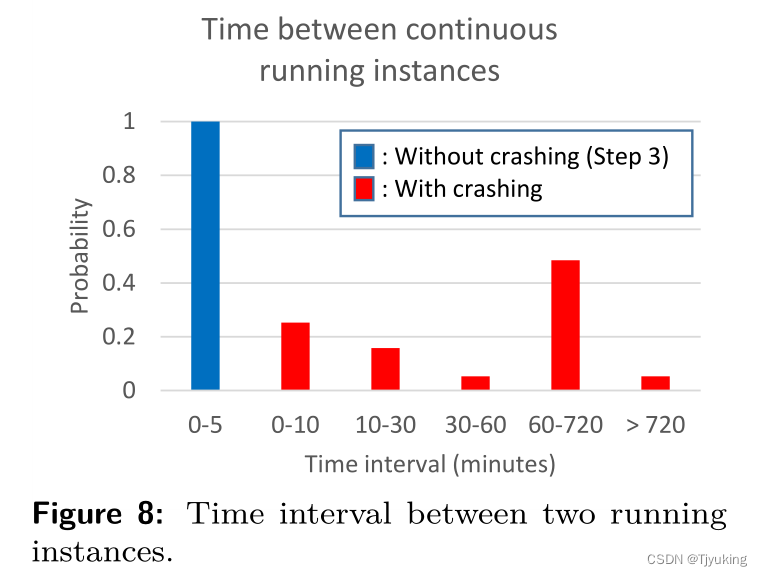

我们的实验表明,AWS F1实例通过启动要求369W的FPGA设计而立即崩溃。通过使用FPGA-fingerprinting,我们发现崩溃的实例不可用时间在在大约一到200小时

引言

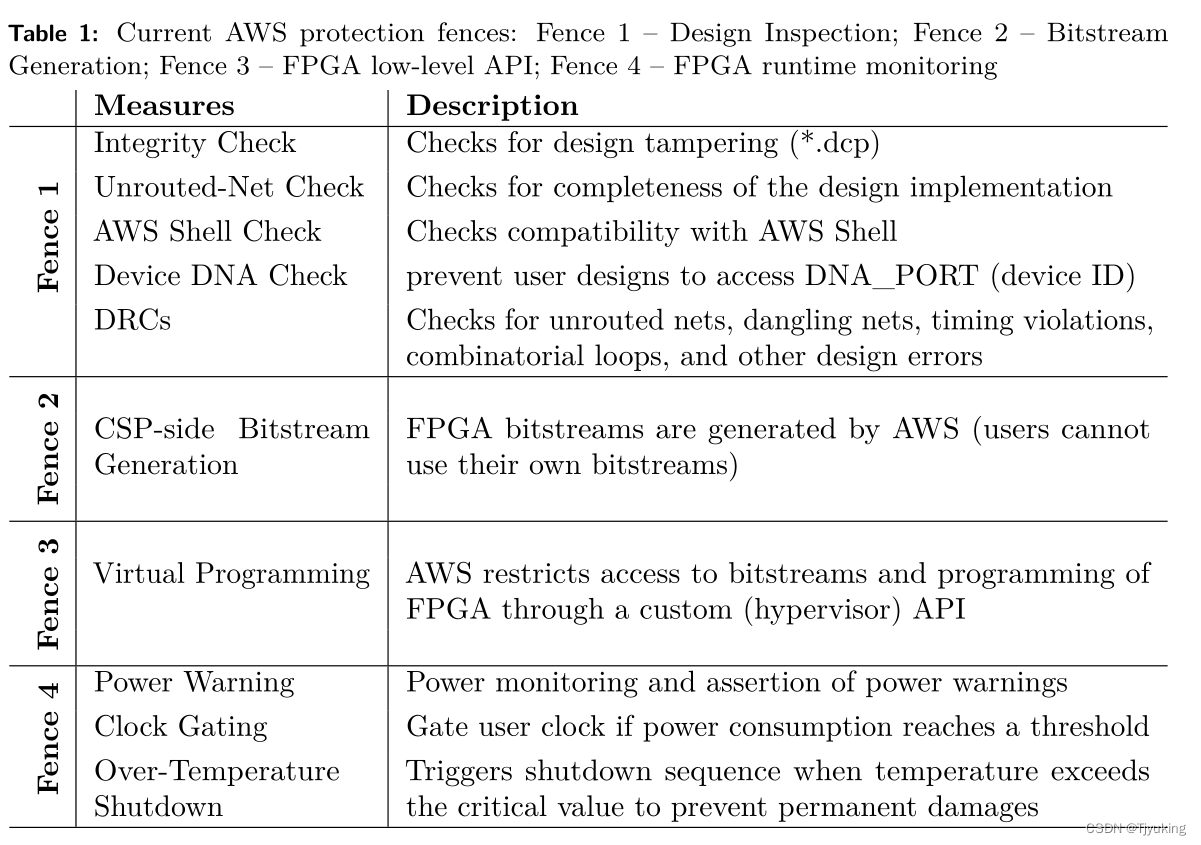

为了防止(攻击者收集潜在CSP和其他租户的敏感数据)情况,CSP实施了若干围栏

1) 检查FPGA设计是否存在潜在的恶意电路,2)CSP生成配置位流,3)阻止直接访问FPGA配置端口的低级API,以及4)FPGA的运行时监控

我们将讨论并演示拒绝服务攻击的多种场景

对于后者,我们重新实现了FPGADefender病毒扫描器[LMG+20],以扩展到大型数据中心FPGA。

为了验证发起的攻击是否成功,并衡量对WS F1云实例可用性的影响,我们实施了指纹识别技术(在第8节中)。

贡献:

1.针对基于FPGA的云计算实例的攻击,对不同(恶意)强力锤击设计进行评估(见第4.3节);

2.将FPGA结构用作AWS F1实例上的温度监测和指纹识别(通过物理不可克隆功能,PUF)传感器(见第4.5节);

3.WS F1 FPGA云实例上的拒绝服务(DoS)演示(第4.6节);

4.缓解策略,包括供应商工具流程的自定义设计规则检查(DRC),以及FPGADefender FPGA病毒扫描器[LMG+20]的重新实施(见第5节)。

此外,我们在第2节中提供了FPGA技术、FPGA开发和部署A WS的背景,第3节中对基于FPGA的系统的当前攻击和对策进行了文献综述,第6节中进行了讨论,第7节中给出了结论。

背景

本文着重于攻击AWS F1

如[JCM15]所示,无法通过防止配置篡改的FPGA安全远程重新配置协议来防止这种情况。这种方法对于封闭系统很有用,但对于希望向大型客户群提供简单可用服务的CSP来说,这种方法无法使用。因此,如第4节所述,CSP正在使用安全基础设施,该基础设施在FPGA部署之前检查用户设计,并在运行时监控FPGA。

FPGA Technology

讲解了LUT在FPGA中起的作用,power_harmingpotential P的意义,FPGA中的一些模块,起的作用,有可能会构成震荡环消耗大量功率

FPGA设计的实现

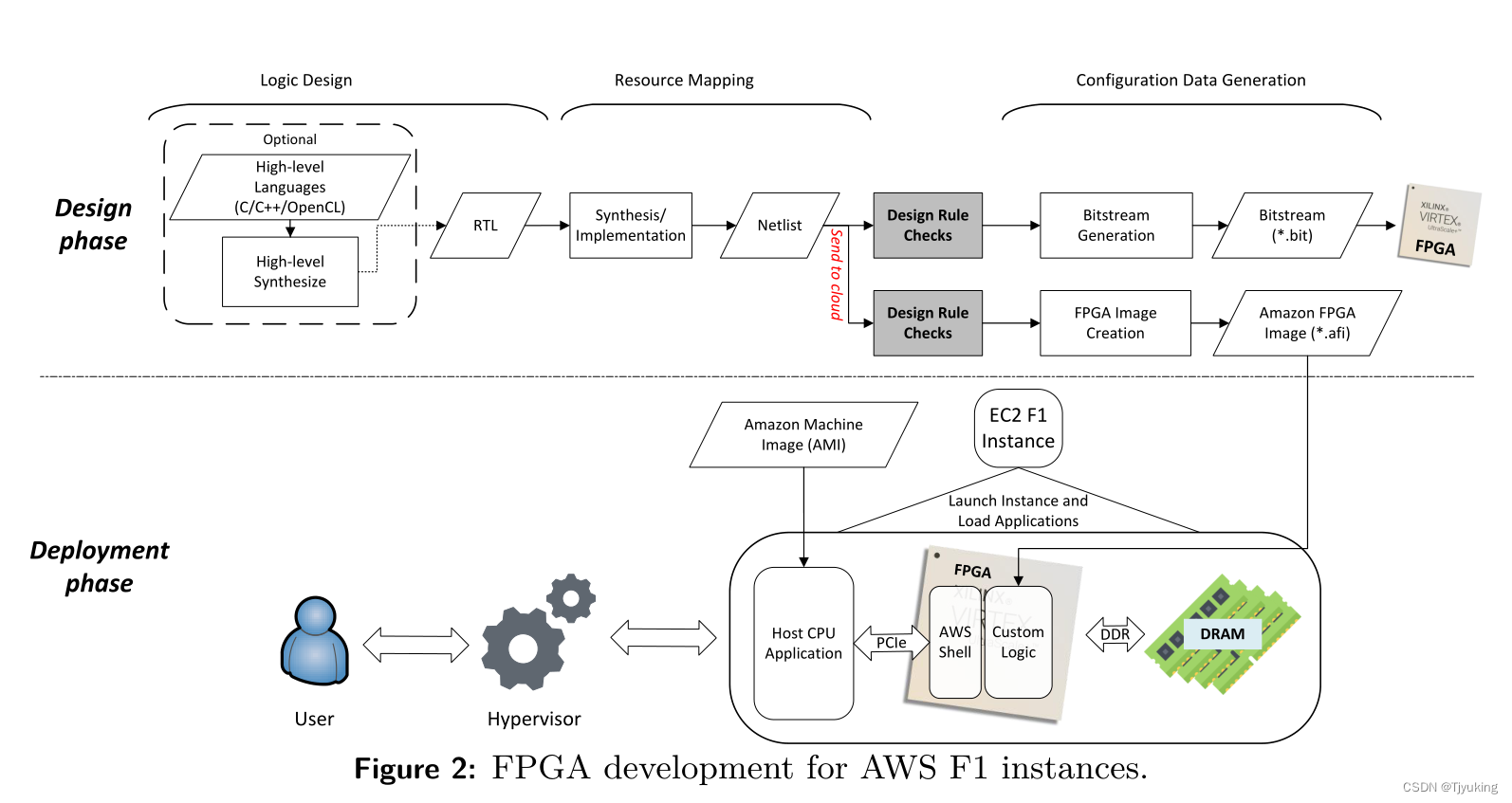

主要讲了FPGA中设计一个实例需要的三个主要过程:

logic design 用户选择自己使用的在FPGA上生成比特流的语言

resource mapping 综合,进行网表映射

Configuration Data (Bitstream) Generation:生成配置比特流,FPGA得以执行任务

用户设计在AWS的注册

介绍了用户如何在AWS上新建网表并生成比特流的过程

用户设计在AWS上的部署

用户的design如何在AWS上安全运行,AWS所作的工作,介绍了用户收费

基于FPGA的系统攻击与对策

基于客户端的FPGA使用与基于云的FPGA使用之间,涉及方的数量以及攻击者与受害FPGA之间的物理接近程度不同,从而导致不同的攻击场景,如以下段落所述

客户端的FPGA使用

一些具有物理访问权限的攻击者可以使用多种技术提取存储在系统中的信息。

恶意电气级威胁MELT

窃取IP

基于云的fpga的使用

云计算模型涉及CSP、FPGA供应商、客户端和其他云用户。

基于云的FPGA 有 数据泄漏、错误注入和拒绝服务攻击

信息泄露

根据远程传感器 测量 FPGA运行速度 从而 测量温度 和 电压

测量运行速度 要进行 区分 同步设计和 任意设计

超频电路 :

原理: 通过快速采样,测量加法器速度,从而测量FPGA的频率和温度

应用:虽然在大多数实际应用中,超频是不可接受的,但在[SOY+20]中表明,超频对机器学习推断是有益的,然而,超频同步电路比振荡器更不适合传感

振荡器:

乎所有演示过的对FPGA泄漏信息的远程攻击都使用振荡器。在[LMG+20]中,据报道,FPGA上的环形振荡器可以在6GHz下运行,这允许高精度地测量电源电压波动,并且基于ROM的传感器已用于远程电源侧信道攻击[SGMT18,ZS18];串扰攻击[GRS19、RGE19、RPD+18];和热隐蔽通道[TS19,Sze20]。

注意:振荡器是自由运行的,不依赖于外部时钟。基本环形振荡器在A WS实例上被禁止,DRC检测。

错误注入攻击

DoS攻击是本文研究的核心问题。鉴于没有一家主要的云供应商在其云基础设施中提供多租户FPGA共享[Ama19b、Ali19、Hua19、Bai19、Ten19、Nim19、Mic19、OVH19],拒绝服务攻击正在对大多数成熟的云FPGA供应商构成严重和直接的威胁。

多租户共享的基础设施组件。例如,过多的热量产生可能会影响相邻实例,或者电源轨通常是共享的,使得来自一个FPGA实例的电压降可能会影响另一个实例。最后,过度消耗电力可能会损坏设备。

对策

系统可以被设计为对故障注入攻击具有鲁棒性(例如,通过引入额外的定时延迟和随机化时钟)

另一种策略是监视系统以检测恶意行为

云FPGA上的拒绝服务攻击

攻击模型

CSP (here A WS)

a cloud service user or an IP core provider in the A WS marketplace

the attacker is using other users to run the attack. (比特币挖矿加速器提供嵌入式强力锤击木马)

AWS FPGA安全架构

All designs have to pass the DRCs

Fence 1 – Design Inspection

Fence 2 – Bitstream Generation 我们无法用短路攻击云FPGA(因为这需要比特流操作)

Fence 3 – FPGA API 安全围栏3防止攻击者直接访问配置位流(AFI)和配置端口

Fence 4 – FPGA Monitoring ①电源监控 ②第二种安全机制允许减慢用户设计 ③AWS使用内置于FPGA中的故障保护机制来保护设备免受过热

AWS EC2 F1强力锤击攻击例子

芯片功耗包括静态功耗和动态功耗。在良性设计中,动态功率可占总功耗的20%-70%[SGDK92]。

动态功耗取决于开关活动,该活动由活动因子α表示,该因子表示信号在一个时钟周期内切换的频率。

由于α依赖于数据,因此通常使用估计来模拟这种效应。E、 g.,Xilinx的功率估计器默认将α设置为12.5%[Xil19d]。然而,恶意电路可以更快地切换100倍[LMG+20]

我们将恶意设计分为两组:1)使用组合循环的设计和2)产生glitches的设计。

绕过fence4 FPGA的监视

我们的实验证实,1)可以绕过clock gating,2)超过134W可以连接丢失SSH。

AWS EC2 F1上的FPGA指纹

本文贡献: 可部署在AWSF1 无法使用组合反馈回路 的实例

耶鲁大学的一个小组使用DRAM衰变来指纹AWS F1实例[TXG+20]。这种方法利用了这样一个事实,即每个FPGA芯片都可以访问四个专用DRAM模块。随后讲解了我们并没有使用这种方法的原因。

作为替代方案,本文 实现了基于振荡器的PUF用于指纹识别,使用透明锁存器 实现(implement) 60个RO环。

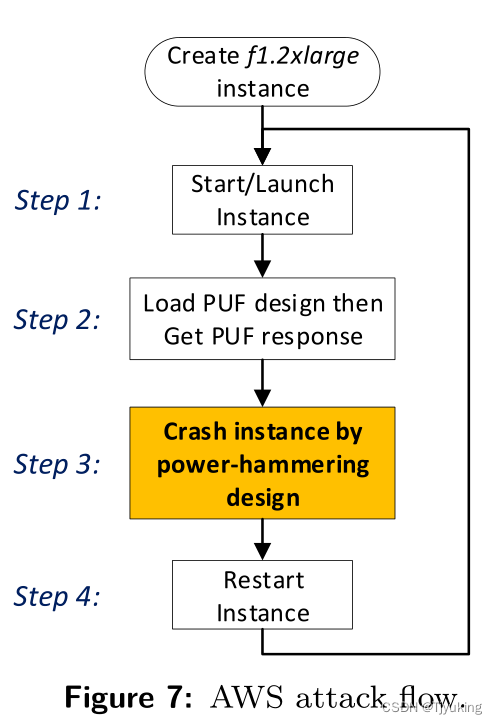

AWS上的DoS–部署和攻击

五次尝试后,我们发现,在没有崩溃的情况下,花了少于5min去 i)建立一个实例,ii)对其进行指纹识别,iii)关闭它我们总是得到相同的FPGA实例。之后,我们又进行了96次实验,包括实例崩溃。如图8所示,我们观察到,在崩溃后,平均需要大约一个小时才能启动新实例,最长的等待时间长达22小时。

缓解策略

通过使用毛刺放大和高扇出网络,任何振荡器电路都可以用于具有远远超过1KW的电势的功率锤击。

因此,重要的是防止部署任何振荡器。

如果没有这一点,任何FPGA监控都会很容易被淹没,而且电源冲击的风险几乎无法控制。

每种方法有有其利弊,本文认为对可用性的攻击 设计检查 是首选方法;与此相反,硬件健壮性和监控是减轻FPGA上运行的攻击的策略。

网表/比特流扫描机

向FPGADefender提供了两项贡献:①处理大型数据中心FPGA设计的扫描仪的实现②我们提供了一个输入路径,可以直接从Xilinx供应商专有的DCP网表文件格式扫描恶意电路。

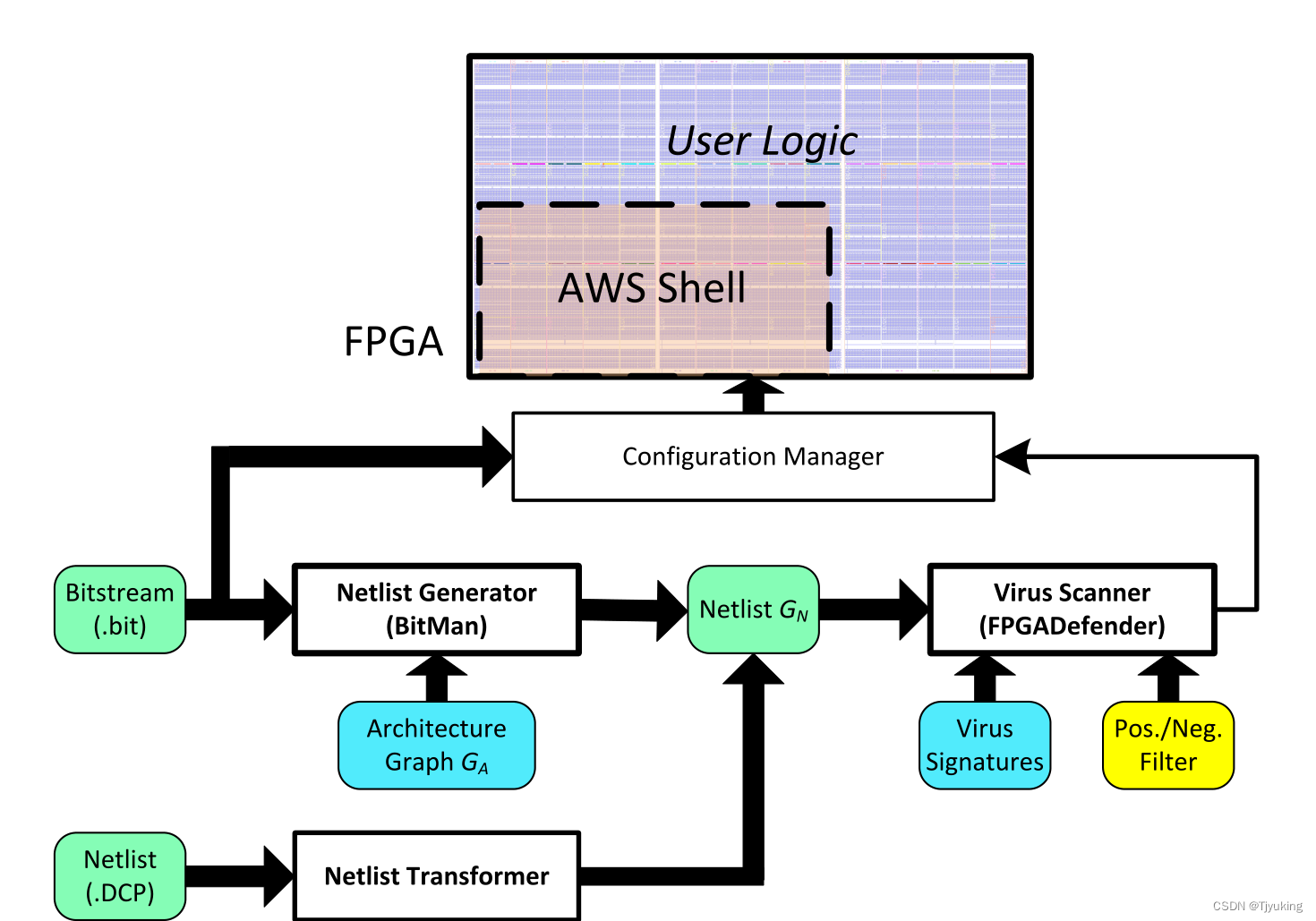

The FPGADefender Framework:

FPGADefender 对于FPGA数据中心

FPGADefender扫描大型设计(通常部署在数据中心FPGA上)需要一天时间才能完成

为了在大型FPGA上实现病毒扫描,开发了C++实现,重点是 实时运行。

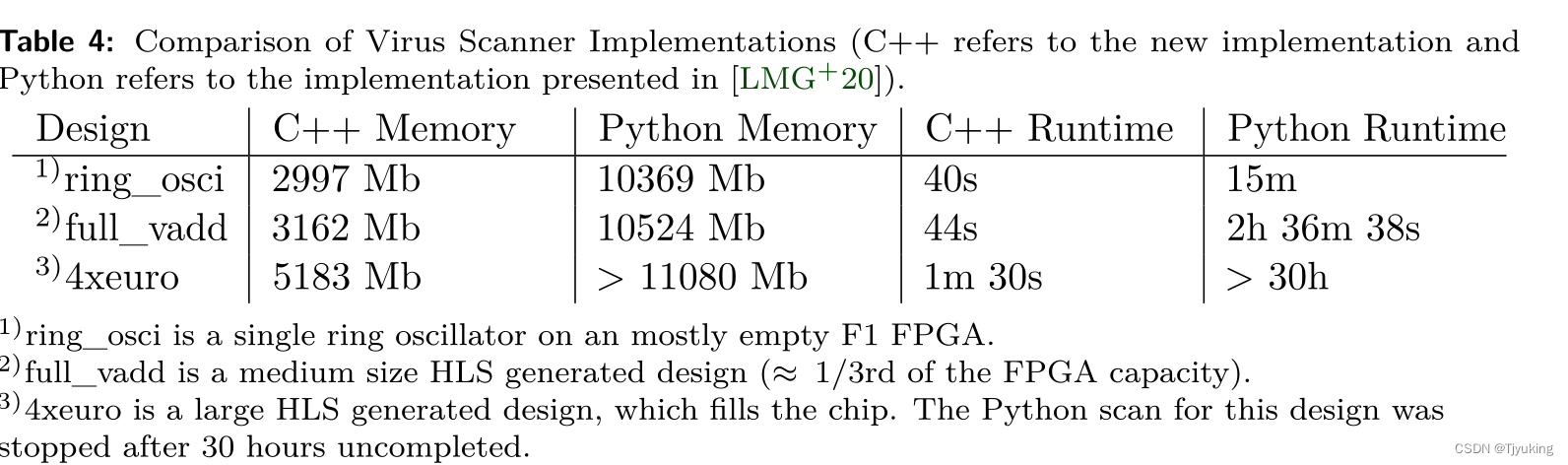

表4中的C++和Python实现的比较显示了扫描速度的差异,我们的重新实现将扫描速度从一天多减少到几分钟。

讨论

们在本文中的主要贡献是以更系统的方式探索A WS FPGA安全生态系统。

为了使CSP能够保护其设备,我们开发了一个DRC收据,该收据使用供应商DRC和静态时序分析来在围栏2中执行更稳健的设计检查。

我们的发现并不局限于AWS或特定的FPGA供应商,本文中提出的攻击将在其他供应商的FPGA上非常类似

结论

本文首先介绍了第一个演示的DoS攻击部署在AWS F1 FPGA云实例上的。

通过PUF使用FPGA指纹,我们发现崩溃的实例通常至少在一个小时内不可用,这强烈表明我们的攻击成功,

最重要的是,我们已经提出了扫描机制,该机制可以减轻本文中提出的所有攻击,并且可以无缝嵌入到A WS FPGA实例的A WS安全基础结构中。这包括一个FPGA病毒扫描器和一个新的设计规则检查收据,该扫描仪可以区分用户加速器和恶意设计。

1384

1384

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?