上拉电阻:电源(Vcc)经过一个电阻接到芯片的信号引脚。

下拉电阻:地(GND)经过一个电阻接到芯片的信号引脚。

作用:

①维持输入引脚处于稳定状态。芯片引脚有三个类型:输入,输出,IO;然后输入有3种状态,高电平,低电平,高阻态。上下拉电阻就是为了使输入稳定在高低电平中一个,二不是高阻态,毕竟高阻态的输入结果是不定态的,可能引起输出振荡。常用于按键电路,复位电路等设计中。

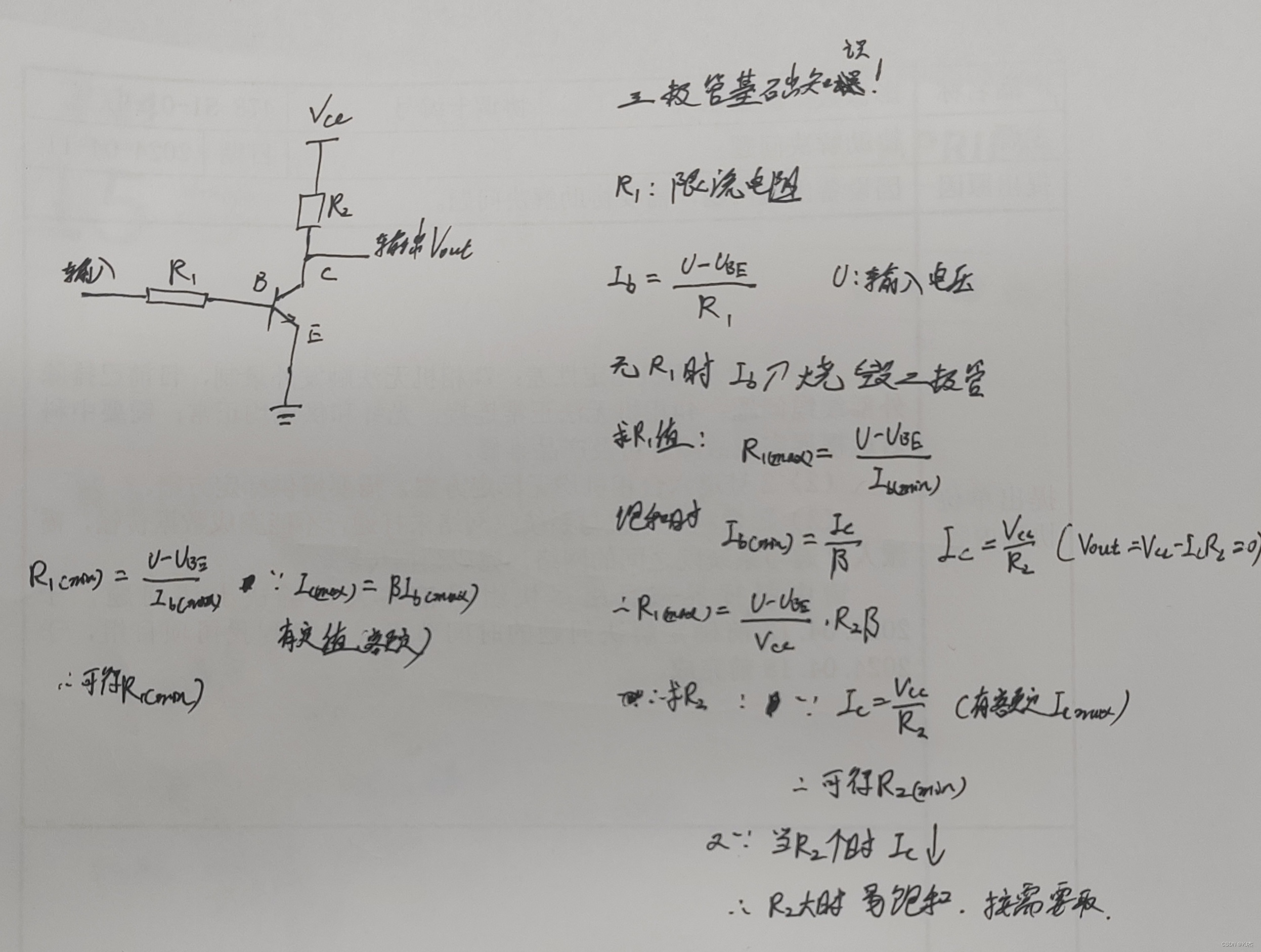

②配合三极管设计电平转换电路。

由上图分析可得:理论是R1的最大最小值,还有R2的最小值,不过实际要考虑三极管放大倍数,电阻,电压的误差和波动,所以有留有余量,工程设计中有个方案里算出的R1最大为11.25kΩ最后所以了1k欧姆的电阻。

(缺补个三极管的链接)

③OC(集电极开路),OD(漏极开路)电路。

上拉电阻主要是给集电极开路输出的电路通过输出电流(这方面我还有待提高理解,望大佬指点)

④总线I/O接口上下拉电阻。

I²C总线一般会接上拉电阻。

就推挽电路可以避免电路短路。

⑤增加输出引脚的驱动能力。

主要是通过上下拉来增加或者减小驱动电流。

⑥电平标准匹配。

不同标准的电平间匹配,如TTL电平和CMOS电平之间的匹配。TTL电路输出的高电平低于COMS电路是最低高电平,如果是TTL驱动COMS电路时,要在TTL的输出端接上拉电阻,提高输出高电平值。注得考虑TTL电路的电流的影响。

⑦增强电路抗干扰能力。

首先是提高输出电平,进而提高噪声容量,增强抗干扰能力。在长距离传输中,电阻不匹配容易引发反射波干扰,可以用上下拉电阻进行匹配,抑制发射波干扰。

6261

6261

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?