目录

选择题

CPLD基本原理:可编程逻辑控制单元

FPGA基本原理:可编程的查找表结构

例化语句端口的关联方式:

名称关联法

h_adder U2(.B(cin),.CO(net3))

位置关联法

h_adder U2(cin,net3)

数字系统优化

面积优化: 资源共享,逻辑优化,串行化

速度优化:流水线设计,寄存器配平,关键路径法,乒乓操作法,加法树法

编码常理

行为描述:always和initial引导的具有顺序执行的语句,if case等

数据流:assign引导的连续赋值

结构描述:例化语句

assign:右边信号的值只要发生变化就会赋值给左边的信号,为并行赋值语句

reg:寄存器类型 wire:网线型

verliog综合器默认为wire型

assign中的输出信号变量必须是wire型,且必须是显式定义

assign左边的目标信号必须为wire型

输入端口信号不能定义为reg型

always块之间为并行语句,always块内部为顺序语句

用关键词or连接所有敏感信号,每当里面的敏感信号发生变化,都启动过程语句,执行所有程序语句

begin_end仅限在always引导的过程语句结构中使用

两类条件语句 if_else 和 case_endcase都必须在always中使用

多个分之同时满足case表达式的时候,执行最先满足表达式的分支项,然后跳出case语句

case语句最末一句条件句必须加上default语句

{}并位运算符,将两个或多个信号按二进制位拼接起来 "{4{1'b0}A}:0000A"

b为二进制,o为八进制,h为十六进制,d为十进制

sb是定义有符号二进制限定关键词

==比较时未知的值x和z认为为0,位数不等高位补0

===位数不等高位不补0,直接认为两个数不等,将x和z当成确定的值进行比较

SO ? D : C : 当SO为1的时候,为D;当SO为0的时候,为C

无符号数乘法运算直接用*

有符号数乘法运算则需将操作数和输出结果用signed定义为有符号数

加法和减法对有无符号数全部认为为无符号数

integer型指示循坏次数,不必特指位数,默认为32位的二进制数寄存器

integer A; A=-20; 将-20赋予A,对应无符号数为65516 65536-20=65516

>>右移 <<左移

无符号数:腾空的位用0补充

有符号数:右移的空位用符号位补充,左移和无符号数一样用0补充

parameter 通过例化语句来传递参数

顶层设计:module MULT4B #(parameter s = 4)(r,a,b);

模块:MULT4B #(.s(8)) U1(rp,ap,bp);

posedge CLK 上升沿 negedge CLK 下降沿

时钟使能EN:EN=1时,时钟上升沿才有效

敏感信号表中一旦有posedge 或 negedge , 所有其他变量都不能放在敏感信号表中

简答题

时序仿真:是接近真实器件运行特性的仿真,仿真文件中已包含了器件硬件特性参数,仿真精度高

功能仿真:是直接对HDL,原理图描述或其他描述形式的逻辑功能进行模拟测试,以了解其实现的功能是否满足原设计的要求.

verliog基本的门级元件 12种基本的门级元件

and多输入端的与门

or多输入端的或门

xor多输入端的异或门

timescale:时间标尺,timescale 10ns/100ps,仿真的基本时间单元是10ms,仿真时间的精度为100ps

串并行语句

assign引导的连续赋值语句为并行语句

always块为并行语句,always块内部为顺序语句

阻塞与非阻塞

阻塞式赋值:一旦执行完当前的赋值语句,赋值目标变量y即刻获得来自等号右侧表达式的计算值

非阻塞式赋值:必须在块语句执行结束时才整体完成赋值操作

循坏语句:for repeat while forever

for(初值;条件;变量增减) begin 循坏语句 end

repeat(循环次数) begin 循坏语句 end

while(条件) begin 循坏语句 end

程序分析题

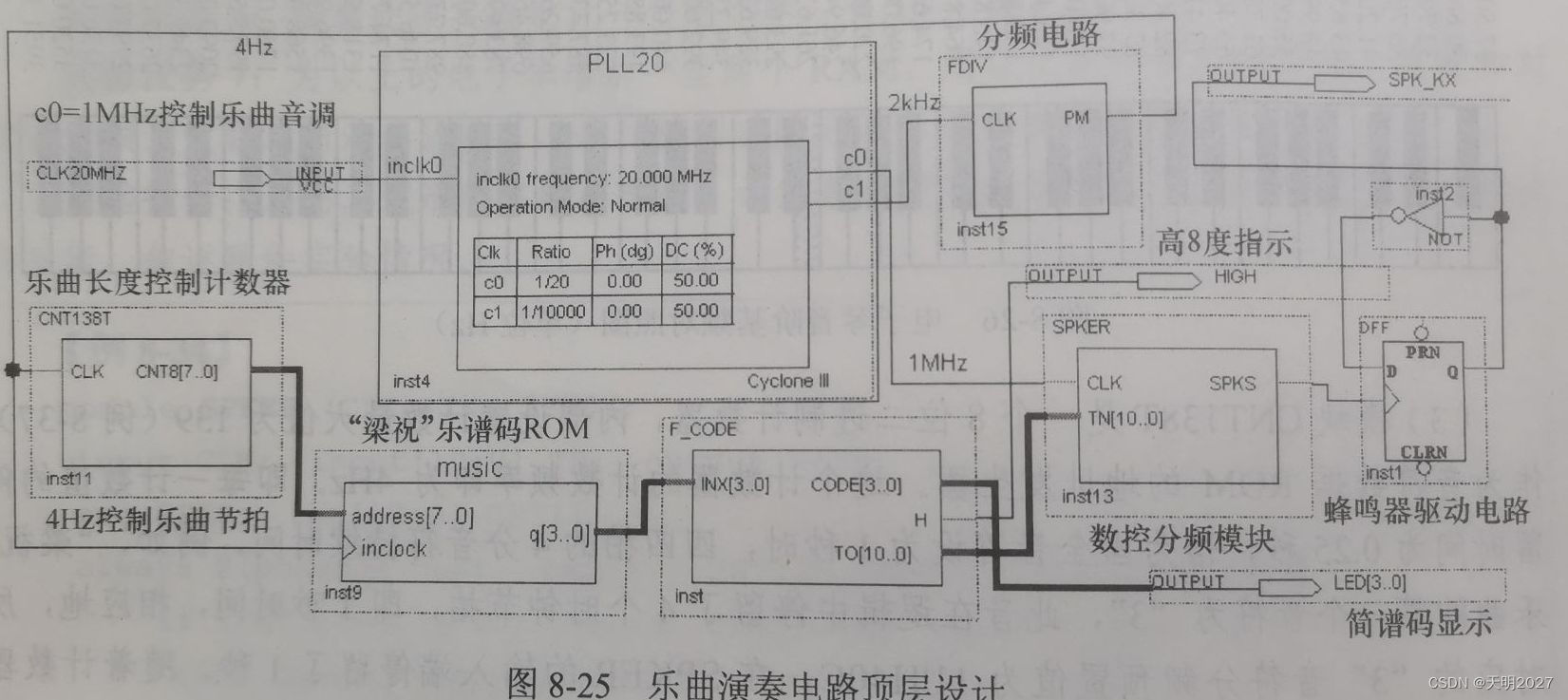

11位分频器SPKER:这是一个用作分频器的可预置计数器,CLK输入较高频率的时钟信号,通过SPKER分频后,经由D触发器构成分频电路,由SPK_KX口输出.SPLK_KXD 输出频率将决定每一音符的音调

D触发器:由于直接从分频器中出来的输出信号是脉宽极窄的信号,为了有利于驱动扬声器,需另加一个D触发器分频以均衡其占空比

F_CODE:为模块SPKER提供所发音符的分频预置数,次数在SPKER输入口停留的时间为此音符的节拍周期;是乐曲简谱码对应的分频预置数查表电路

音乐节拍和音调发生查表模块MUSIC:和工作时钟inclock的频率共同决定每一音符的停留时间;是一个LPM_ROM,它的输入频率来自自锁环PLL20的输出频率

自锁相环PLL20:为MUSIC提供输入频率

模块CNT138T: 是一个8位二进制计数器,作为音符数据ROM的地址发生器

(不一定考)音符节拍:例如第一个音符为3,停留4个时钟节拍,即1秒时间,相应的,所对应的3音符分频预置值为11'H40C,在SPKER的输入端停留一秒,随之计数器CNT138T按4HZ的时钟速率作加法计数时,即随地址递增时,音符数据ROM模块MUSIC中的音符数据将从ROM中通过q[3:0]端口输向F_CODE模块,乐曲开始演奏起来,CNT138T的节拍对应ROM中的简谱码数

966

966

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?