ARM架构与汇编指令

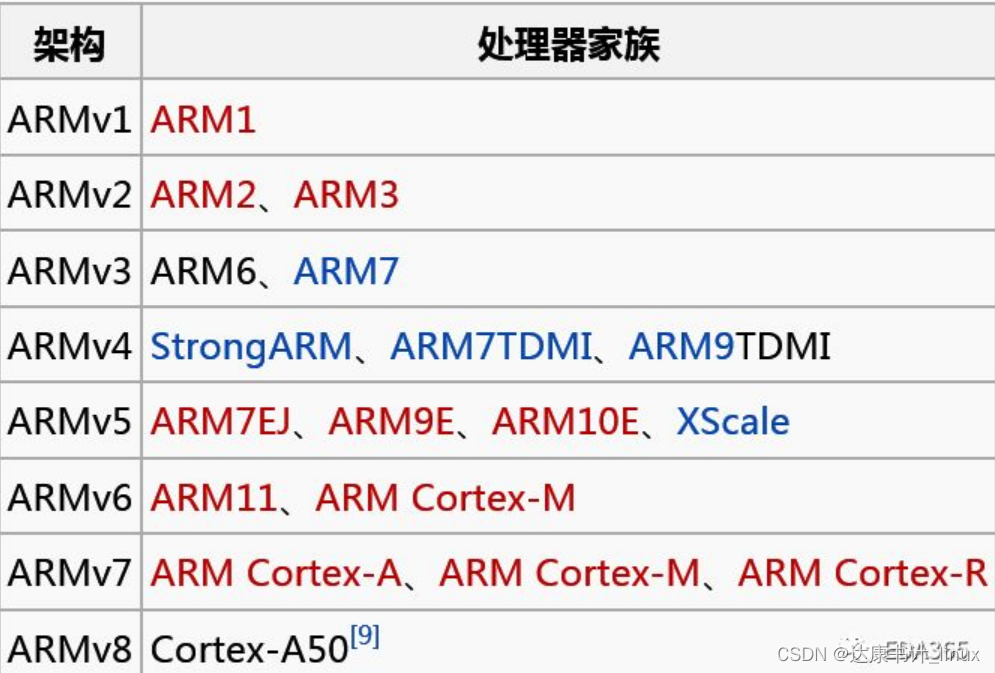

ARM架构

ARM处理器

冯诺依曼结构:ARM7

冯诺依曼结构中不独立区分程序和数据空间,处理器只有一套总线,即程序和数据空间共用地址和数据总线,取指令和取数据不能同时进行。

哈佛结构:ARM9

哈佛结构中程序空间和数据空间是独立的,具有各自独立的地址线和数据总线,即处理器有两套总线,一套是程序存储器的数据和地址总线,一套是数据存储器的数据和地址总线。取址和取数据能并发进行。

改进的哈佛结构 ARM9以后的大部分内核采用改进的哈佛架构

改进型哈佛结构是在普通哈佛结构的基础上加上独立的缓冲区cache, 虽然处理器只有一套总线,但由于cache的存在,CPU直接访问的是cache,而cache又分为指令cache和数据cache,这两个cache是独立的,所以可以同时访问指令和数据,也就是说能够并行运行。

处理器的流水线技术

流水线介绍

三级流水线:arm7

取指级 :读取指令。

译码级 :对指令进行译码。占有“译码逻辑”,不占有“数据路径”。

执行级 :指令占有“数据路径”,寄存器堆栈被读取,操作数在桶式移位器中被移位,ALU产生相应的运算结果,并写回目的寄存器中。并根据需求更改状态寄存器的条件位。

五级流水线:ARM9

六级流水线:ARM10,还有更多级的流水线,但是最基本的就是取指令,译码,执行这三个操作。

Cortex‐M3讲解

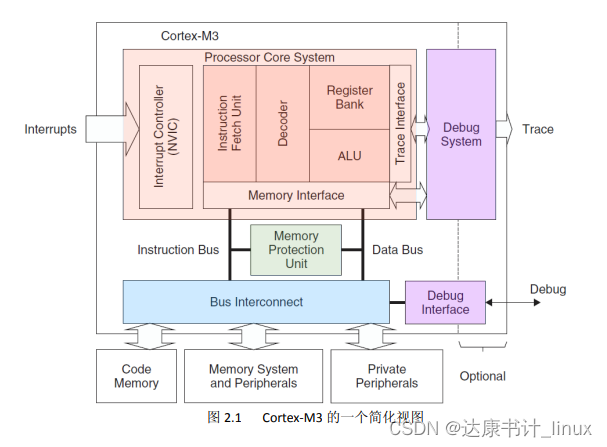

cortex-m3架构

Cortex‐M3采用哈佛结构,三级流水线。如图可以看到有一条数据总线和指令总线。

CPU内核运行程序,是先从code memory取出指令,然后芯片内部译码,执行(计算和对memory的读写操作)

CPU内核如何一条一条的读取指令,然后计算,最后再写入memory呢?芯片也有自己的寄存器组,通过寄存器组的值,自动的实现取指令,译码,执行的操作。

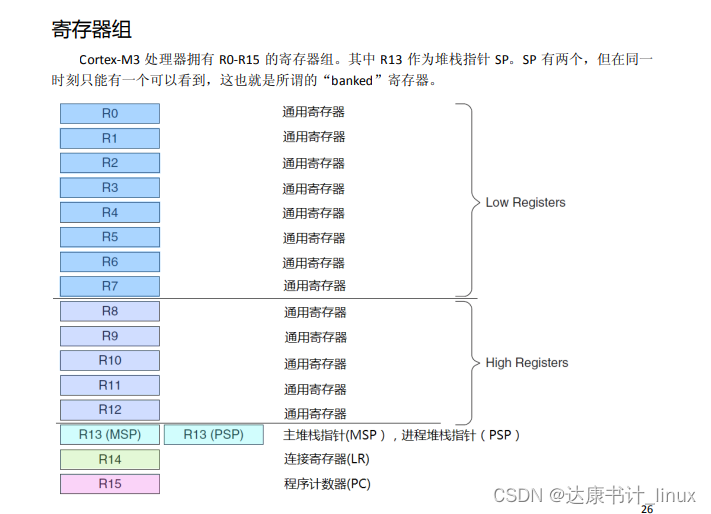

寄存器组

PC(R15):CPU内核会自动从PC寄存器的值所在的地址读取指令,然后自动累加PC值到下一条指令处,就这样一条一条的往下运行程序。

程序复位后如何从第一行指令开始运行:复位之后,CPU会自动从0x0000 0004获取PC指针的起始值

,然后一条条取指令,执行。(0x0000 0000 地址的值是用来初始化堆栈指针,即初始化SP寄存器(R13)的值,也是CPU自动操作)。

汇编语言

基本语法

操作码 操作数1,操作数2,… ; 注释

操作码:指令助记符

汇编语言中 ; 分号表示注释。

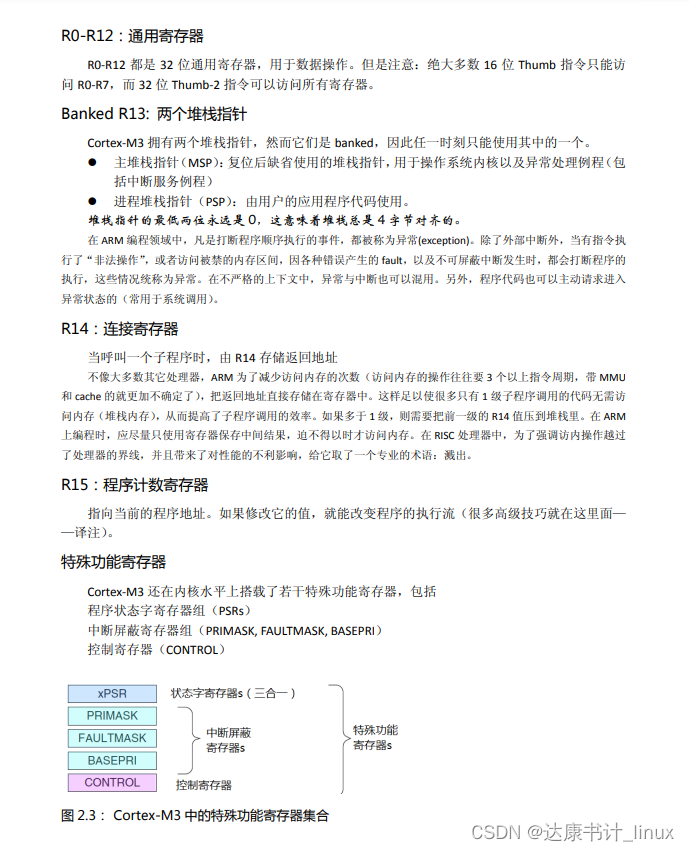

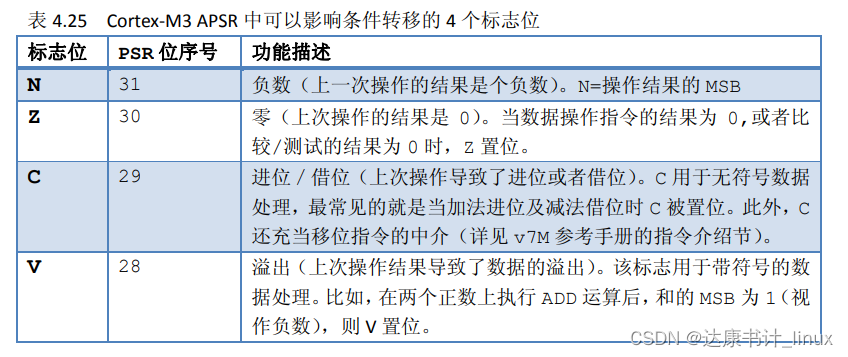

APSR寄存器

APSR 中的 5 个标志位

N: 负数标志(Negative)

Z: 零结果标志(Zero)

C: 进位/借位标志(Carry)

V: 溢出标志(oVerflow)

S: 饱和标志(Saturation),它不做条件转移的依据

数据传送指令

两个寄存器间传送数据

MOV R8, R3 ;将R3的值赋值给R8

寄存器与存储器间传送数据

LDRB Rd, [Rn, #offset] ;从地址 Rn+offset 处读取一个字节到 Rd

LDRH Rd, [Rn, #offset] ;从地址 Rn+offset 处读取一个半字到 Rd

LDR Rd, [Rn, #offset] ;从地址 Rn+offset 处读取一个字到 Rd

STRB Rd, [Rn, #offset] ;把 Rd 中的低字节存储到地址 Rn+offset 处

STRH Rd, [Rn, #offset] ;把 Rd 中的低半字存储到地址 Rn+offset 处

STR Rd, [Rn, #offset] ;把 Rd 中的字存储到地址 Rn+offset 处

多个寄存器访问:

LDMIA.W Rd!, {寄存器列表} ;从 Rd 处读取多个字。每读一个字后 Rd 自增一次,32

位宽度

STMIA.W Rd!, {寄存器列表} ;存储多个字到 Rd 处。每存一个字前 Rd 自减一次,32

位宽度

后索引

STR.W R0, [R1], #-12 ;后索引

该指令是把 R0 的值存储到地址 R1 处的。在存储完毕后, R1 <- R1+(‐12)

把一个立即数加载到寄存器

MOV R0, #0x12 ; #号表示立即数

访问特殊功能寄存器

这两条指令是访问特殊功能寄存器的“绿色通道”——当然必须在特权级下,除 APSR 外。

指令语法如下:

MRS , ;加载特殊功能寄存器的值到 Rn

MSR , ;存储 Rn 的值到特殊功能寄存器

数据处理

加法 ADD

ADD R0, R1 ; R0 += R1

ADD R0, #0x12 ; R0 += 12

ADD.W R0, R1, R2 ; R0 = R1+R2

不加后缀和s加后缀s和

ADD.W R0, R1, R2 ; 不更新标志位

ADDS.W R0, R1, R2 ; 更新标志位

减法 SUM

SUB Rd, Rn ; Rd -= Rn

乘法 MUL

MUL Rd, Rm ; Rd *= Rm

除法 UDIV/SDIV

UDIV Rd, Rn, Rm ; Rd = Rn/Rm (无符号除法)

SDIV Rd, Rn, Rm ; Rd = Rn/Rm (带符号除法)

常用逻辑操作指令

按位与

AND Rd, Rn ; Rd &= Rn

AND.W Rd, Rn, #imm12 ; Rd = Rn & imm12

按位或

ORR Rd, Rn ; Rd |= Rn

ORR.W Rd, Rn, #imm12 ; Rd = Rn | imm12

按位异或

EOR Rd, Rn ; Rd ^= Rn

EOR.W Rd, Rn, #imm12 ; Rd = Rn ^ imm12

位段清零

BIC Rd, Rn ; Rd &= ~Rn

BIC.W Rd, Rn, #imm12 ; Rd = Rn & ~imm12

移位和循环指令

逻辑左移

LSL Rd, Rn, #imm5 ; Rd = Rn<<imm5

LSL Rd, Rn ; Rd <<= Rn

逻辑右移

LSR Rd, Rn, #imm5 ; Rd = Rn>>imm5

LSR Rd, Rn ; Rd >>= Rn

转移指令

无条件转移指令

BL Label ;转移到 Label 处对应的地址,并且把转移前的下条指令地址保存到 LR

BLX reg ;转移到由寄存器 reg 给出的地址,根据 REG 的 LSB 切换处理器状态,

;并且把转移前的下条指令地址保存到 LR

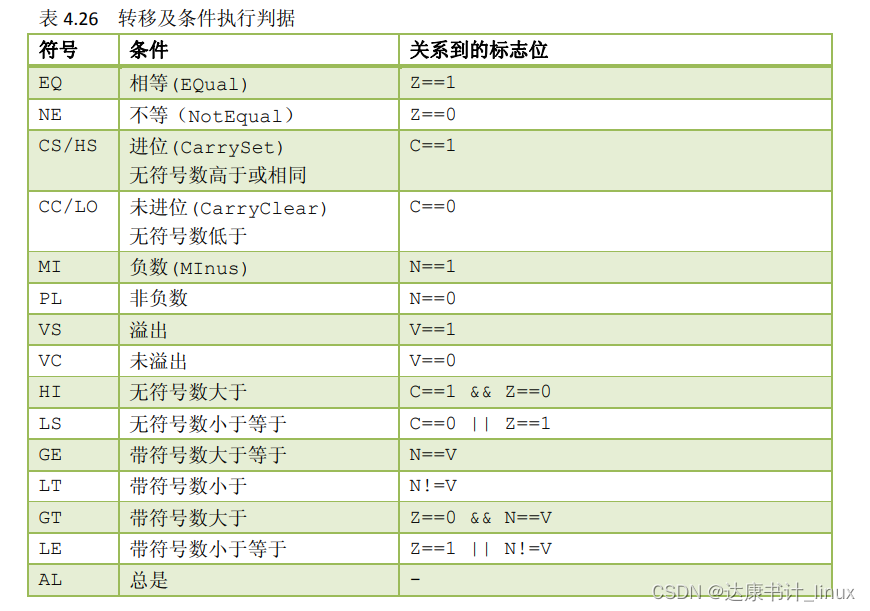

标志位与条件转移指令

标志位

条件后缀

带条件跳转指令

BEQ label ;当 Z=1 时转移

BCC label ;当C == 0时转移

用法:

cmp r2,r3;r2-r3,

BCC label;当r2 < r3 时跳转。减法错位跳转

5267

5267

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?