前两篇分别详解了ADS1256的数据手册以及代码分析,这篇文章来介绍一下实际操作以及精准分析。附上上一篇文章的链接:FPGA控制ADS1256的ADC采集(二)。

测试

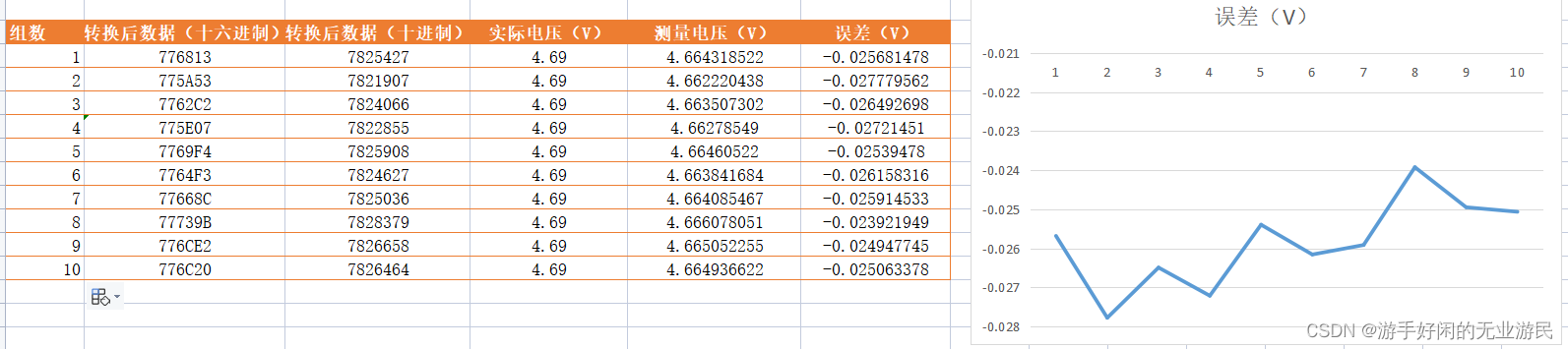

(1)4.69V电压测试

实际上本来想测的是FPGA管教上的5V,但是用万用表一测发现只有4.69V,分析了一下发现板子上的一个二极管压降导致的(不是自己画的板子),不过关系不大,4.69V也可以测。测试结果如下所示:

上图可见数据为77 6813h,转换为十进制就是7,825,427,每一个单位是2的23次方-1,所以最终的电压就是 2 × 2.5 × 7,825,427 /(2^23-1)= 4.664V。可以看到这边有一个25mv左右的误差。我陆陆续续测了十组数据,由于篇幅问题不一一贴上来了,我将它们打成excel图表,如下所示:

可以看到,误差主要集中在20——30mv之间(这让我很怀疑参考电压是否真的是5V,实验的时候,忘记了测一下了。。。),不过最大上下的波动依旧有4mv,这个我想和单端测量有很大的缘故,如果换成差分输入,波动幅度会小很多。

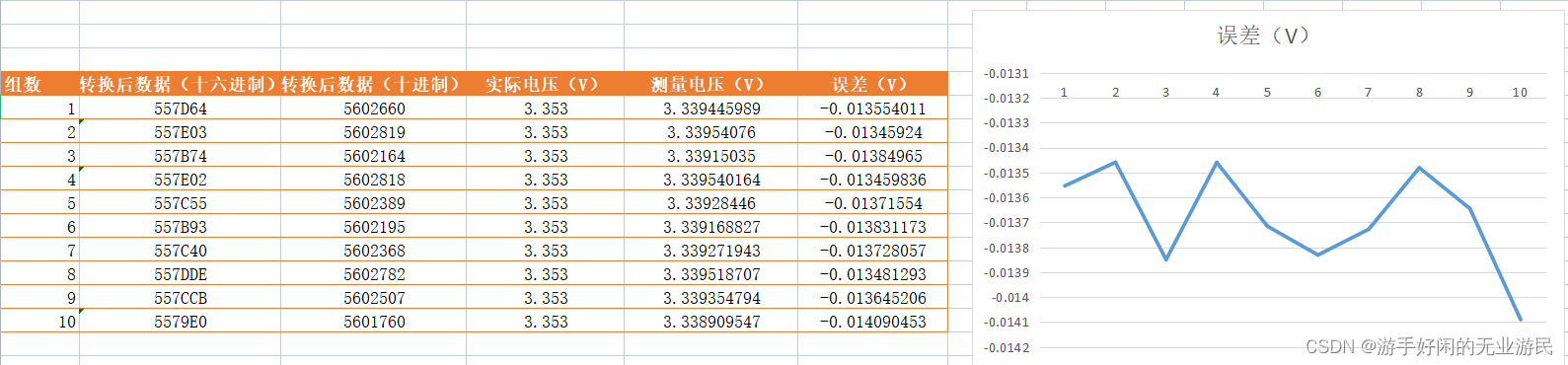

(2)3.353v电压测量

同理,我们来测一下3.353V的电压,同样附上一张ILA的截图以及excel表格:

可以看到,测量3.353V的误差集中在13——14mv之间,最大浮动误差有0.6mv。

工程链接

CSDN下载链接:FPGA控制ADS1256进行ADC采样

百度网盘下载链接:FPGA控制ADS1256进行ADC采样,提取码vde4。

结语与思考

分析完数据后发现单端测量的浮动其实是比较大的,我想第一和我的连接方式有关,杜邦线的稳定性未知,第二参考电压是否为准确的5.0V还有待考究,我想测得准确的参考电压后再测应该会准上不少,再加以差分输入,有希望将误差与浮动降到最低,这些我就给个参考方式,具体的实现就交给读者自己解决了,就是改个硬件条件,软件改个寄存器配置即可。如果有什么问题欢迎评论区指出。

2393

2393

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?