距离上一次的介绍IOBUF已经过去不少时间了,我们知道,大多数时候编译器会帮助我们给顶层模块加上IBUF以及OBUF,如若需要其他类型的BUF,需要我们手动添加。这回继续分析差分IO逻辑资源。

IBUFDS 和 IBUFGDS

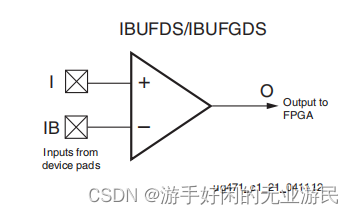

介绍之前,先来看一下对应原语的框图:

由上可见,该原语有三个端口,差分输入以及单端输出,其中IB为差分的N端,I为差分的P端。IBUFDS和IBUFGDS的原语结构是一样的,但是应用场景不同, IBUFGDS通常用来差分时钟输入,而IBUFDS则用于一般的差分信号线输入。

以下是调用的模板例程:DIFF_TERM表示是否打开内置的差动终端,这个我们一般不开启;IBUF_LOW_PWR是老朋友的,表示是否开启低功耗,注意开启低功耗仅在LVDS以及HSTL电平下有效;IOSTANDARD 表示电平标准,默认即可。

-- VHDL

Library UNISIM;

use UNISIM.vcomponents.all;

-- IBUFDS: Differential Input Buffer

-- 7 Series

-- Xilinx HDL Language Template, version 2022.2

IBUFDS_inst : IBUFDS

generic map (

DIFF_TERM => FALSE, -- Differential Termination

IBUF_LOW_PWR => TRUE, -- Low power (TRUE) vs. performance (FALSE) setting for referenced I/O standards

IOSTANDARD => "DEFAULT")

port map (

O => O, -- Buffer output

I => I, -- Diff_p buffer input (connect directly to top-level port)

IB => IB -- Diff_n buffer input (connect directly to top-level port)

);

-- End of IBUFDS_inst instantiation

// Verilog

// IBUFDS: Differential Input Buffer

// 7 Series

// Xilinx HDL Language Template, version 2022.2

IBUFDS #(

.DIFF_TERM("FALSE"), // Differential Termination

.IBUF_LOW_PWR("FALSE"), // Low power="TRUE", Highest performance="FALSE"

.IOSTANDARD("DEFAULT") // Specify the input I/O standard

) IBUFDS_inst (

.O(O), // Buffer output

.I(I), // Diff_p buffer input (connect directly to top-level port)

.IB(IB) // Diff_n buffer input (connect directly to top-level port)

);

// End of IBUFDS_inst instantiation

OBUFDS

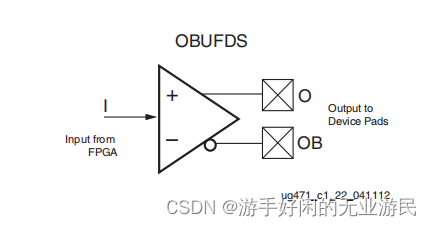

如下所示为OBUFDS的原语框图:

同样的道理,这个原语就是单端转差分输出使用的原语,OB表示输出的N端,O表示输出的P端。一般而言这个原语用于信号输出,时钟输出的话建议使用ODDR原语。

以下是调用的模板:IOSTANDARD表示电平标准,SLEW表示速率。

-- VHDL

Library UNISIM;

use UNISIM.vcomponents.all;

-- OBUFDS: Differential Output Buffer

-- 7 Series

-- Xilinx HDL Language Template, version 2022.2

OBUFDS_inst : OBUFDS

generic map (

IOSTANDARD => "DEFAULT", -- Specify the output I/O standard

SLEW => "SLOW") -- Specify the output slew rate

port map (

O => O, -- Diff_p output (connect directly to top-level port)

OB => OB, -- Diff_n output (connect directly to top-level port)

I => I -- Buffer input

);

-- End of OBUFDS_inst instantiation

// Verilog

// OBUFDS: Differential Output Buffer

// 7 Series

// Xilinx HDL Language Template, version 2022.2

OBUFDS #(

.IOSTANDARD("DEFAULT"), // Specify the output I/O standard

.SLEW("SLOW") // Specify the output slew rate

) OBUFDS_inst (

.O(O), // Diff_p output (connect directly to top-level port)

.OB(OB), // Diff_n output (connect directly to top-level port)

.I(I) // Buffer input

);

// End of OBUFDS_inst instantiation

结语

Xilinx的原语不计其数,但是很多我们日常项目设计中都是不会去使用的,所以就挑两个最常使用的来介绍,如若有朋友需要使用到其他的原语或者其他设计要求的,欢迎评论区讨论。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?