之前转载过一片有关FPGA的差分输入输出的文章,这些天终于有空静下心来分析了,通过在官网的不懈努力,愈发觉得应该写一篇有关IOBUF逻辑原语相关的文章,也算是作为自己的学习笔记。

整体介绍

开头已经说了,接下来会介绍7系列中有关BUF相关的一系列资源,我想将他们分为两大块,单端IO标准以及差分IO标准,本文将会着重介绍单端IO标准,差分的IO标准将会放到下一篇文章介绍。说起IOBUF,它到底是一个什么东西?它有什么用?应该怎么去用?有哪些类型?具体的应用场合是什么?代码应该怎么写?别急,这些内容在接下来都会有所介绍。

IOBUF是什么?

这一点我在官网上没有找到解释,不过我的理解是,当外部的信号进入我们FPGA的IO,或者FPGA内部信号出去时,往往其驱动能力是有限的,例如说一个外部的时钟信号只能驱动一个逻辑块,但是加上BUF之后可以对其进行扩展,加强驱动能力。

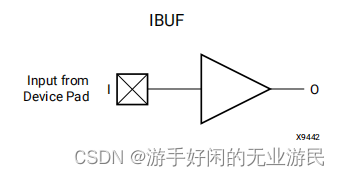

IBUF/IBUFG

这两个原语的使用方法和功能一摸一样,一般情况下,IBUF作用是提高输入端口的驱动能力,IBUFG用作时钟信号输入的缓冲。需要注意的是,大多数情况下vivado会帮助我们自动添加上IBUF/G,不需要用户手动添加,如果用户想要手动添加的话,请在顶层模块调用其原语。调用方法相当简单,这边主要就是介绍一下IBUF_LOW_PWR这个参数,设置为"FALSE"可以获得最好的性能,设置为"TRUE"则在LVDS以及HSTL等差分场合下可以节省功率。

// IBUF: Single-ended Input Buffer

// 7 Series

// Xilinx HDL Language Template, version 2022.2

IBUF #(

.IBUF_LOW_PWR("FALSE"), // Low power (TRUE) vs. performance (FALSE) setting for referenced I/O standards

.IOSTANDARD("DEFAULT") // Specify the input I/O standard

) IBUF_inst (

.O(O), // Buffer output

.I(I) // Buffer input (connect directly to top-level port)

);

// End of IBUF_inst instantiation

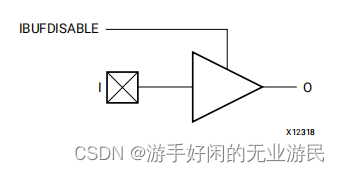

IBUF_IBUFDISABLE

这个原语的功能主要是为了在低功耗场合使用,当输入信号不需要使用的时候可以关断BUF,从而减少功耗,当你的端口供电来源为VREF时(例如SSTL和HSTL)这个功能就很有必要了,因为他们的功耗比非VREF要来得更高。使用方面,结合下方的例子,具体我想说一下有关于USE_IBUFDISABLE这个参数:如若设置USE_IBUFDISABLE为"FALSE"表明不使能,此时输入将会被忽略,且用户应该将其设置为低电平,如若设置为"TRUE",则当IBUFDISABLE信号为高电平时关断输入,并强制设置输出为高电平。IBUF_LOW_PWR同样也是在低功耗和高性能之间选择一个。

// IBUF_IBUFDISABLE: Single-ended Input Buffer with Disable

// 7 Series

// Xilinx HDL Language Template, version 2022.2

IBUF_IBUFDISABLE #(

.IBUF_LOW_PWR("FALSE"), // Low power ("TRUE") vs. performance ("FALSE") for referenced I/O standards

.IOSTANDARD("DEFAULT"), // Specify the input I/O standard

.USE_IBUFDISABLE("TRUE") // Set to "TRUE" to enable IBUFDISABLE feature

) IBUF_IBUFDISABLE_inst (

.O(O), // Buffer output

.I(I), // Buffer input (connect directly to top-level port)

.IBUFDISABLE(IBUFDISABLE) // Buffer disable input, high=disable

);

// End of IBUF_IBUFDISABLE_inst instantiation

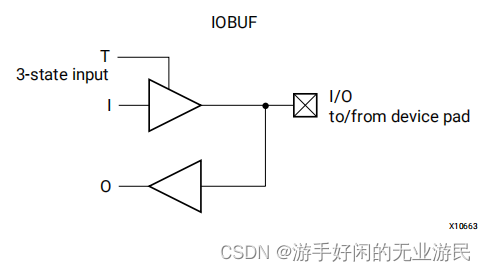

IOBUF

这个原语用来设置一个双向IO的缓冲区,将内部逻辑连接至外部的双向引脚。例如IIC通信的SDA引脚就可以使用这个原语。该原语设计了一个T端口(选择是输入还是输出),具体在下方例子注释中有说明。需要注明的参数有DRIVE,可供选择的有2, 4, 6, 8, 12, 16, 24,默认12,设置越大表明输出的驱动能力越大,例如说外挂的IIC设备很多,那么最好设置得大一点。SLEW表示输出上升沿和下降沿的速度,有"SLOW"和 "FAST"可供选择。

// IOBUF: Single-ended Bi-directional Buffer

// All devices

// Xilinx HDL Language Template, version 2022.2

IOBUF #(

.DRIVE(12), // Specify the output drive strength

.IBUF_LOW_PWR("TRUE"), // Low Power - "TRUE", High Performance = "FALSE"

.IOSTANDARD("DEFAULT"), // Specify the I/O standard

.SLEW("SLOW") // Specify the output slew rate

) IOBUF_inst (

.O(O), // Buffer output

.IO(IO), // Buffer inout port (connect directly to top-level port)

.I(I), // Buffer input

.T(T) // 3-state enable input, high=input, low=output

);

// End of IOBUF_inst instantiation

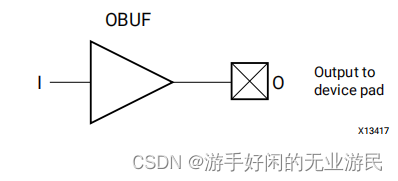

OBUF

这个原语必须为每一个输出端口都加上,第一与FPGA内部隔离,第二可以增大IO的驱动能力。当然,大多数的设计软件都会自动的给端口加上IBUF以及OBUF,所以就不需要我们手动添加(手动添加也没有错,但是大多数人都不会去添加),但还是建议知道一下。调用的方法也是相当简单,于此不多介绍了。需要说明的参数包括DRIVE,可供选择的有2, 4, 6, 8, 12, 16, 24,默认12,设置越大表明输出的驱动能力越大;SLEW,可供选择的有"SLOW"和 “FAST”,表明输出上升沿和下降沿的速度。

// OBUF: Single-ended Output Buffer

// 7 Series

// Xilinx HDL Language Template, version 2022.2

OBUF #(

.DRIVE(12), // Specify the output drive strength

.IOSTANDARD("DEFAULT"), // Specify the output I/O standard

.SLEW("SLOW") // Specify the output slew rate

) OBUF_inst (

.O(O), // Buffer output (connect directly to top-level port)

.I(I) // Buffer input

);

// End of OBUF_inst instantiation

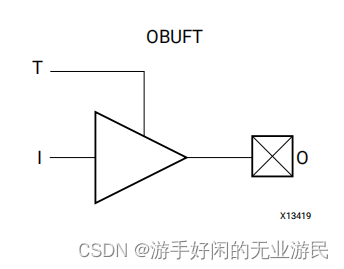

OBUFT

这个原语就是给输出加上了一个选通端,当我们设置T端口为低电平时使能输出,设置为高电平时输出为高阻态。应用场景一般是需要三态输出的双向IO的情况。需要注意的是,OBUFT按照手册上说明,电平标准为CMOS1.8V,但是我设置为CMOS3.3也没有报错,这一点更深入到板级的我就没继续深究下去了,不过可以作为一个参考依据,下次碰到问题了再说,或者说直接就使用CMOS1.8V的电平标准。

// OBUFT: Single-ended 3-state Output Buffer

// All devices

// Xilinx HDL Language Template, version 2022.2

OBUFT #(

.DRIVE(12), // Specify the output drive strength

.IOSTANDARD("DEFAULT"), // Specify the output I/O standard

.SLEW("SLOW") // Specify the output slew rate

) OBUFT_inst (

.O(O), // Buffer output (connect directly to top-level port)

.I(I), // Buffer input

.T(T) // 3-state enable input

);

// End of OBUFT_inst instantiation

结语

关于单端的原语就讲这么多了,其实单端的说起来就两种,输入和输出的缓冲器,编译器默认会给端口加上缓冲,用户可选择的就是加不加使能端,所以用起来很方便也很简单。下篇将会介绍差分的BUFS,相比于单端就要复杂一些了。

1973

1973

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?