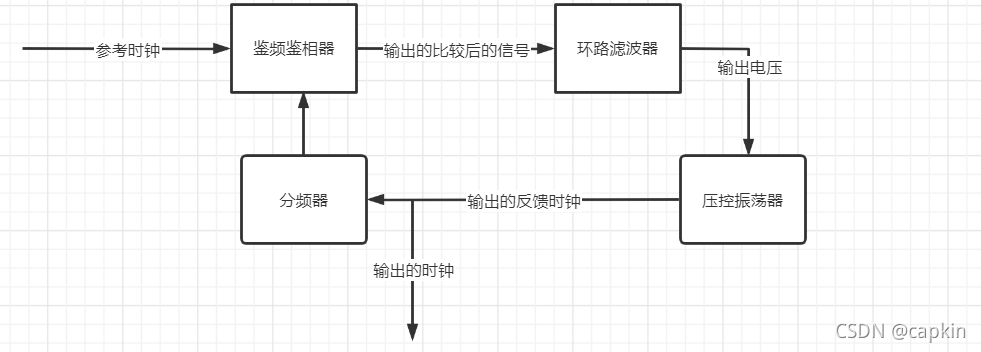

PLL是一种反馈控制电路,其特点是利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

是最为常用的ip_core之一,其性能强大,可以对输入到FPGA的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望周期。

工作原理

锁相环是一个反馈系统,参考时钟输入和反馈时钟到鉴频鉴相器,比较这两个时钟的频率和相位的差异,输出到环路滤波器,控制噪声的带宽滤掉高频噪声是我们的频率更加平滑,输出电压幅值的信号输入到压控振荡器,输入到压控振荡器的电压高输出的频率越大。

eg:参考信号的时钟为50MHz,反馈基准时钟频率为10MHz,经过鉴频鉴相器输出一个变大的成正比的一个值到环路滤波器,从而环路滤波器的输出信号电压变大导致压控振荡器输出的频率更高,直到两个时钟信号相同输出的时钟信号为50MHz

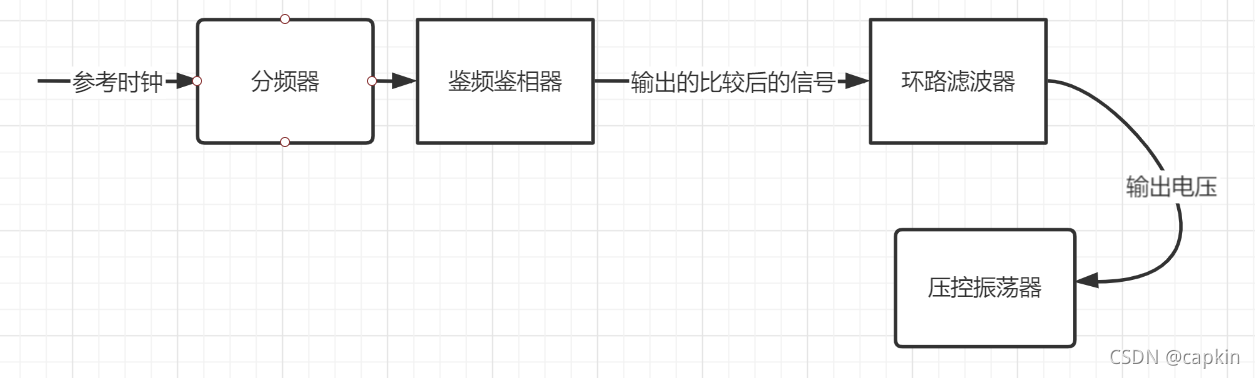

倍频的实现

与基本的PLL就多了一个分频器DIV,通过分几倍频,就倍几倍频的时钟信号。

分频的工作原理

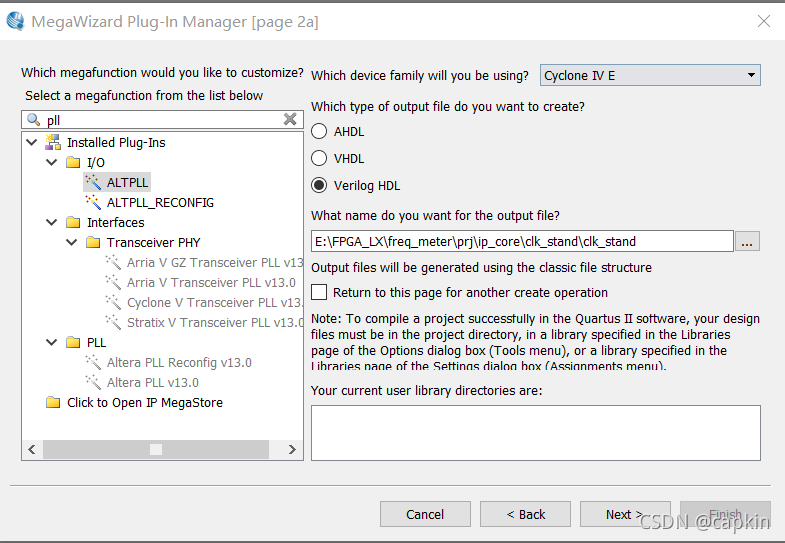

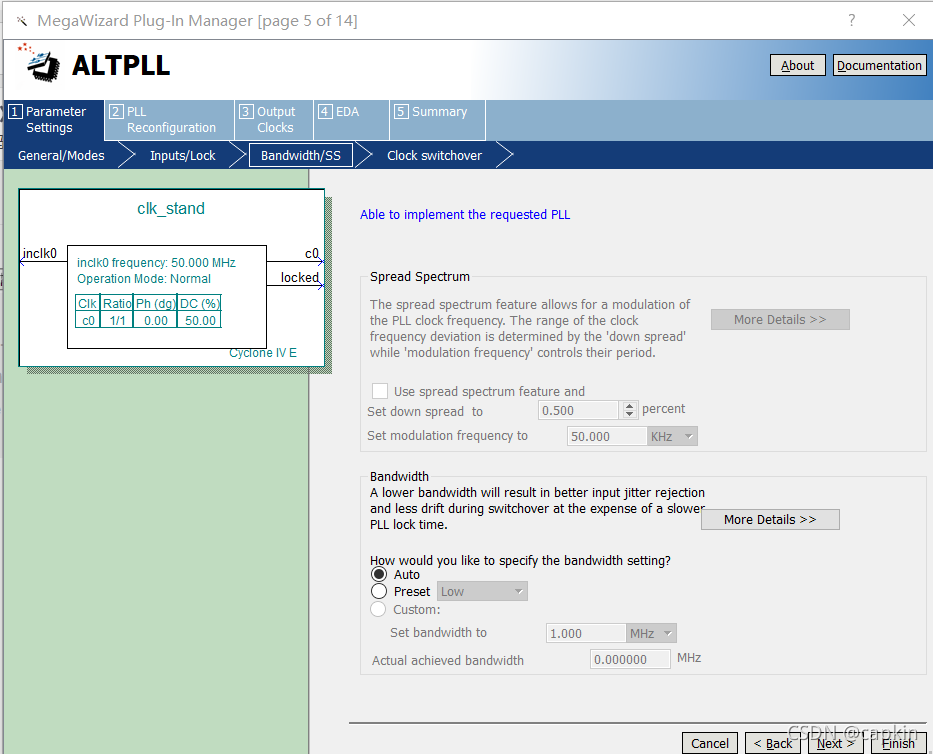

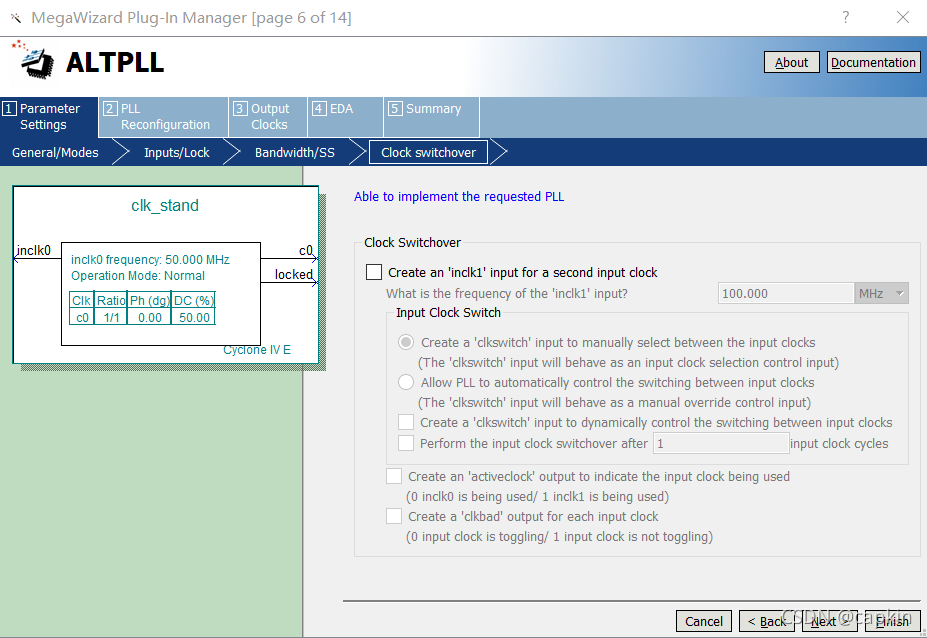

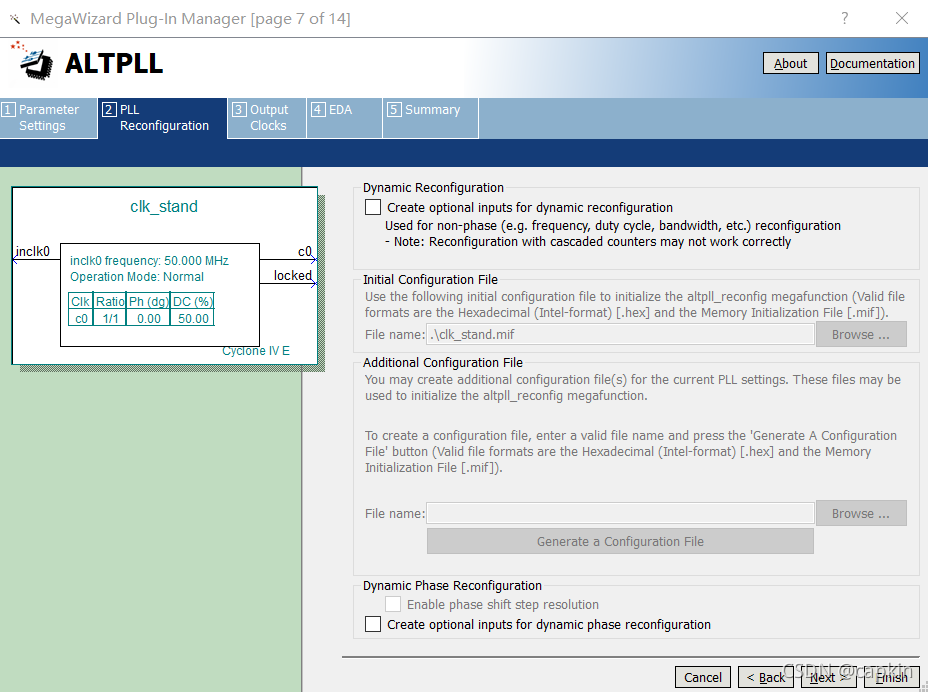

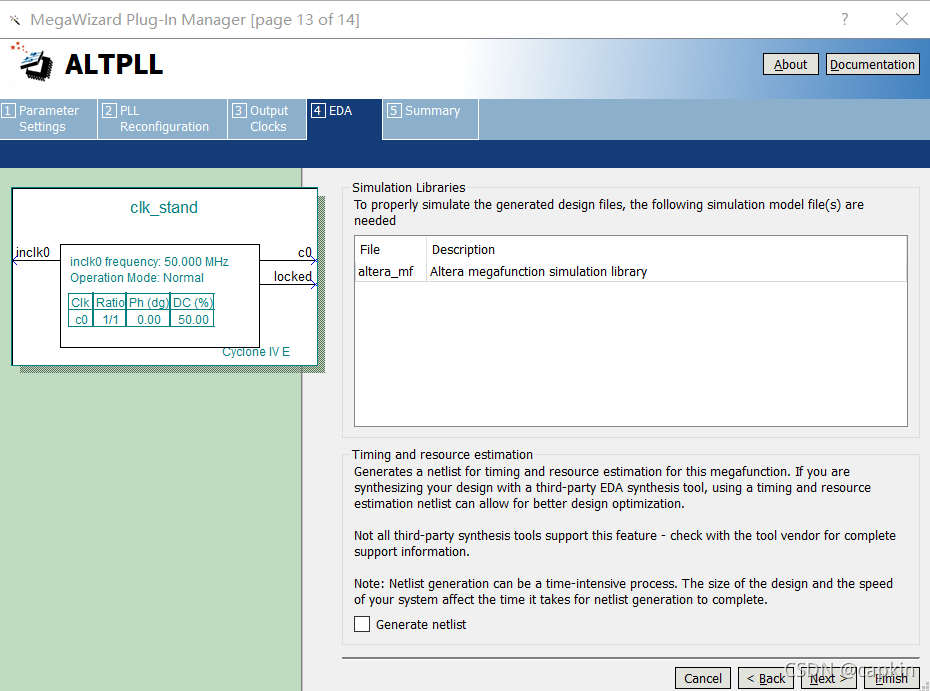

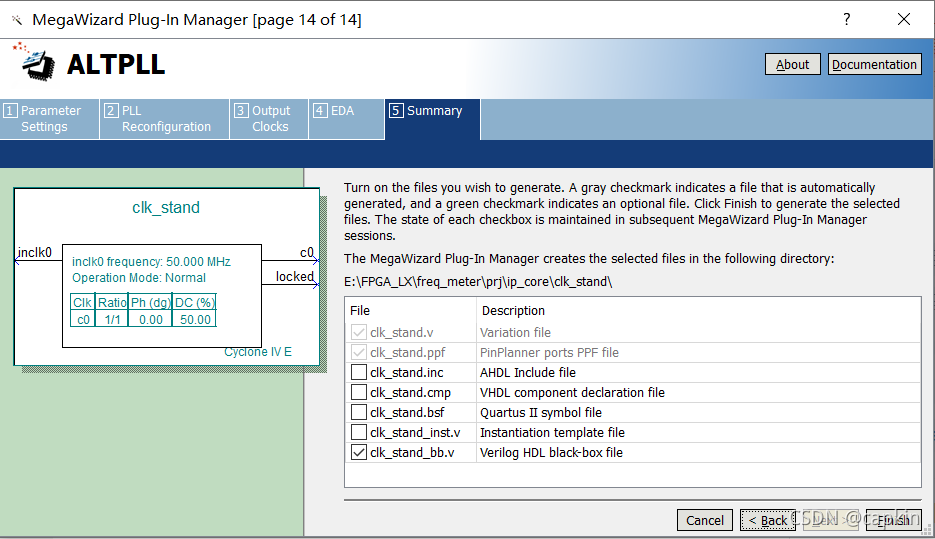

IP_core pll的配置

1.首先建立一个工程

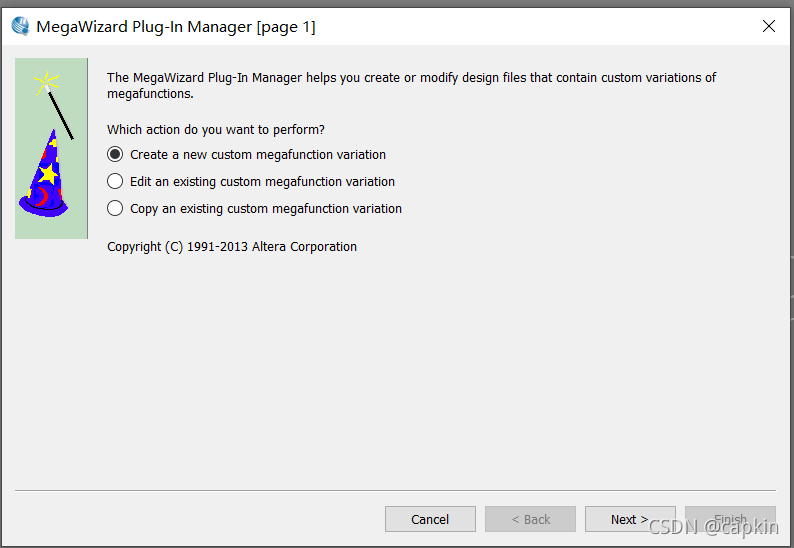

2.打开tools–>MegaWizard Plug-In Manager

第一个选项是创建一个新的IP_core

第二个选项是编辑已经存在的Ip_core

第三个选项是复制已经存在的ip_core

这里选择第一个:

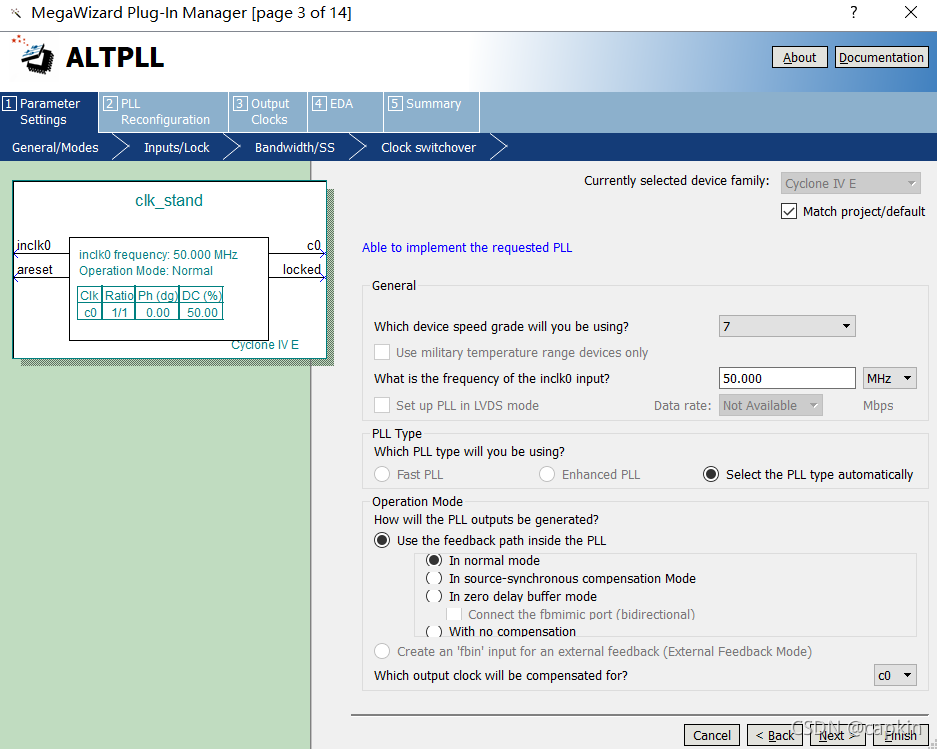

对下图进行理解

时钟反馈模式:Use the feedback path inside the pll

源同步模式:In source synchronous compensation Mode

一般使用在数据接口,特别是高速的数据接口,数据和时钟来自于同一个数据源,可以保证数据和时钟之间的相位关系

无补偿模式:with no compensation

pll不对任何时钟网络进行补偿,这样会有更好的抖动特性,但是不能确定延迟的时间

标准模式:in normal mode

普通模式使用在内部寄存器上相位保持一致,如果外部输出相位可能会超前或滞后于PLL内部时钟信号。、

零延迟缓冲模式:in zero delay buffer mode

输入到寄存器相位会发生超前或滞后,而输出外部的时钟信号的相位保持一致。

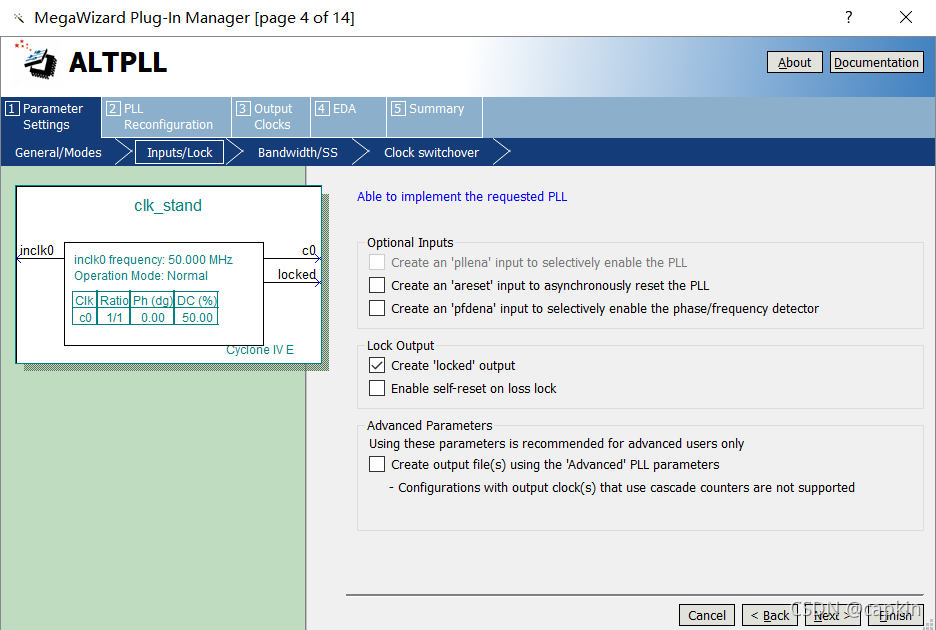

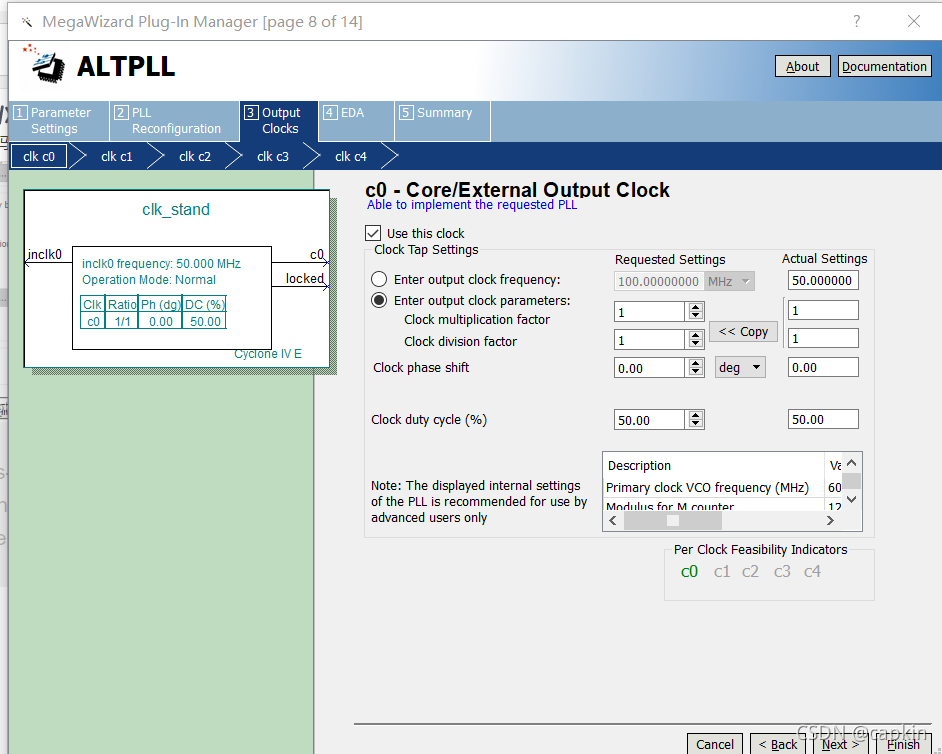

对上图use this clock 是否使用该时钟

enter output clock frequency 然后在后面写输出的时钟频率

enter output clock parameters 进行参数配置

clock multiplication factor 在后面配置乘法因子

clock division factor 在后面配置除法因子

然后在actual settings上看你是配置的输出时钟的频率

clock phase shift相位 有角度和时间两个单位deg 、ns

clock duty cycle 占空比(在一个完整的时钟周期内高电平所在的比例)

2921

2921

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?