1.主要内容:

1.基本功能的实现:串口的基本收发

2.串口的中断实现:通过控制寄存器

3.简易PC与FPGA串口通讯的架构

2.实验中用到的器件

AC7100B(核心板型号,下同)核心板,是基于 XILINX 公司的 ARTIX-7 系列 100T的 XC7A100T-2FGG484I 这款芯片开发的高性能核心板,具有高速,高带宽,高容量等特点,适合高速数据通信,视频图像处理,高速数据采集等方面使用。vivado版本2018.3

3.基本理论

串 口 指 异 步 串 行 通 信 , 异 步 串 行 是 指 UART ( Universal Asynchronous Receiver/Transmitter),通用异步接收/发送。 UART 是一个并行输入成为串行输出的芯片,通常集成在主板上。 UART 包含 TTL 电平的串口和 RS232 电平的串口。 TTL 电平是 3.3V 的,而 RS232 是负逻辑电平,它定义+5~+12V 为低电平,而-12~-5V 为高电平, MDS2710、 MDS SD4、 EL805 等是RS232 接口, EL806 有 TTL 接口。

串行接口按电气标准及协议来分包括 RS-232-C、 RS-422、 RS485 等。 RS-232-C、 RS-422 与 RS- 485 标准只对接口的电气特性做出规定,不涉及接插件、电缆或协议。

异步串口通信协议

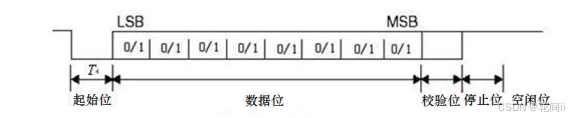

消息帧从一个低位起始位开始,后面是 7 个或 8 个数据位,一个可用的奇偶位和一个或几个高位停止位。接收器发现开始位时它就知道数据准备发送,并尝试与发送器时钟频率同步。如果选择了奇偶校验, UART 就在数据位后面加上奇偶位。奇偶位可用来帮助错误校验。在接收过程中, UART 从消息帧中去掉起始位和结束位,对进来的字节进行奇偶校验,并将数据字节从串行转换成并行。 UART 传输时序如下图所示:

从波形上可以看出起始位是低电平,停止位和空闲位都是高电平,也就是说没有数据传输时是高电平,当一个下降沿事件发生时,我们认为将进行一次数据传输。

常见的串口通信波特率有 2400 、 9600、 115200 等,发送和接收波特率必须保持一致才能正确通信。波特率是指 1 秒最大传输的数据位数,包括起始位、数据位、校验位、停止位。 假如通信波特率设定为 9600,那么一个数据位的时间长度是 1/9600 秒。

4.uartliteIP核GUI

提供官方的IP核操作下载地址:AMD Technical Information Portal

IP核详解:

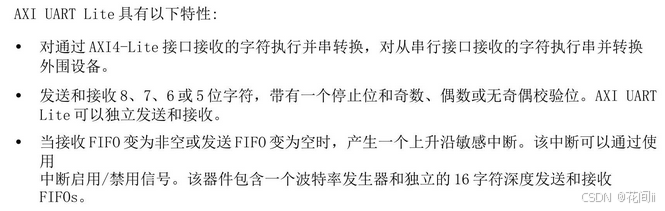

特征:

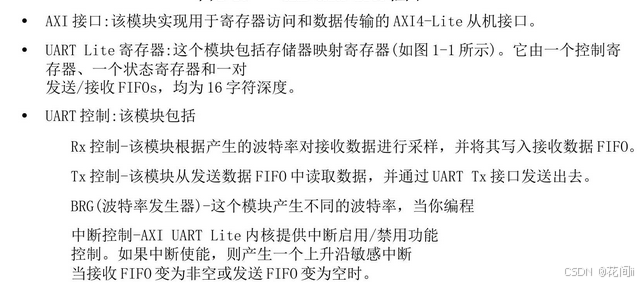

用于寄存器访问和数据传输的AXI-LITE接口

全双工

16字符发送和接收的fifo

一个字符中可配置的数据位数(5-8)

可配置的奇偶校验位数

可配置波特率

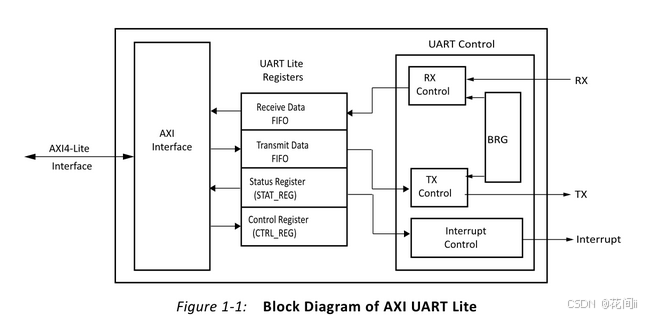

功能摘要

接口信号

| signal name | interface | i/o | initial state | description |

| system signal | ||||

| s_axi_aclk | system | i | - | 总线时钟 |

| s_axi_aresetn | system | i | - | 复位,低电平有效 |

| interrupt | system | o | o | 上升沿UART中断 |

| AXI channel Signals | ||||

| s_axi | S_AXI | - | - | |

| RX | UART_LITE | I | - | |

| TX | UART_LITE | O | 0X1 | |

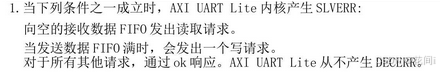

备注:

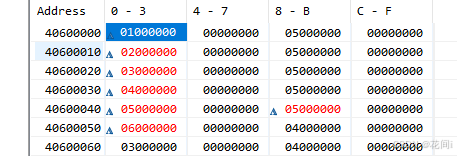

寄存器地址映射

5.创建工程

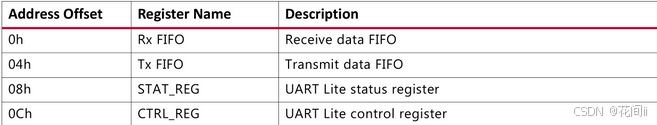

打开vivado,建立BD工程,如图:

生成bitstream,打开SDK,编写C代码驱动程序。

6.实现代码:

1.确保硬件线路是通的,先用例程代码做个收发测试,打印一个hello。

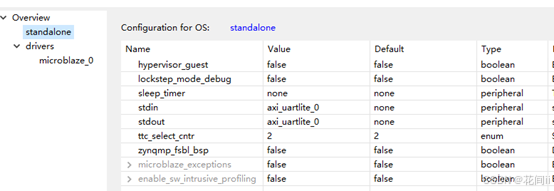

2.找到自己的板级支持包,查询下打印数据的接口,有的ZYNQ相关的硬件会默认PCMU输出,这个点成UARTlite

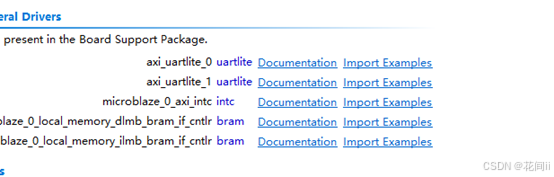

3.接下来写驱动,不知道怎么写的就直接用例程看下用到啥

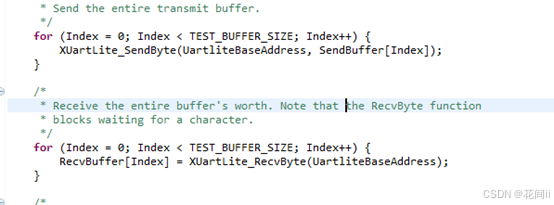

这里打开了其中一个low_level的,主要发送和接收函数是这个

4.随便写了点代码测试了一下

发送状态:hello FPGA

接收状态01-06接收数据。

7.UART中断

上述的表示接收与发送都OK了,硬件线路是OK的,然后搞中断。

所谓中断就是CPU在干什么事情的时候,达到某一个触发条件,然后执行触发条件需要的操作。

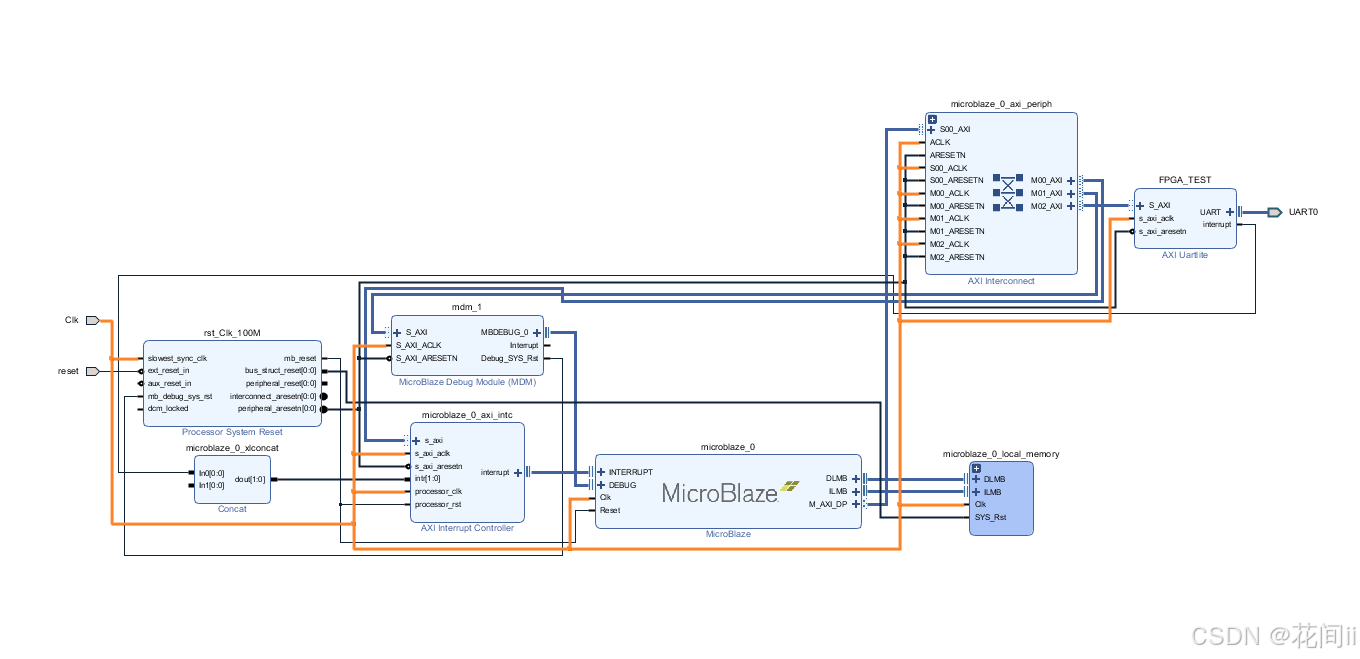

在上述架构的基础上,把中断链接到系统中断,然后重新生成bit流,创建SDK,编写驱动。

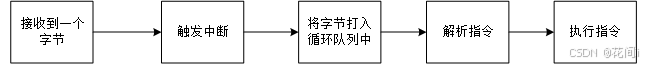

代码流程为:

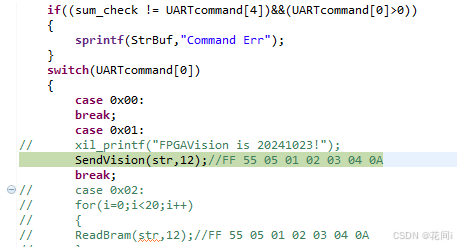

具体参考代码:

8.实现效果

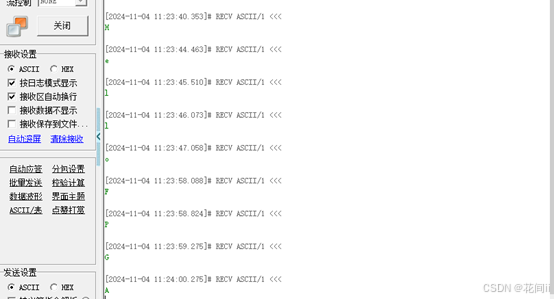

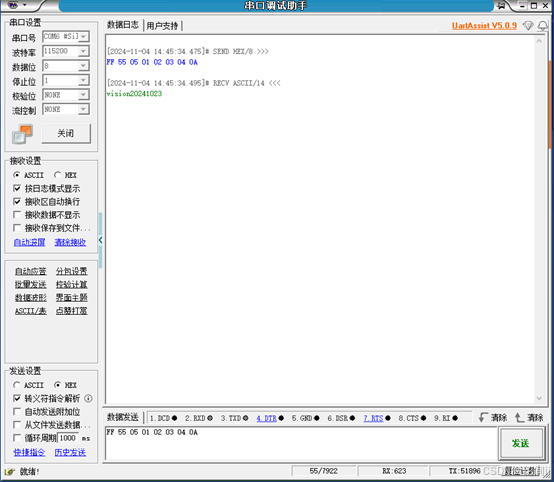

输入FF5505010203040A,得到最终版本信息。输出打印

766

766

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?