第六章 半导体存储器【微机原理】

前言

以下内容源自微型计算机原理(第四版)王忠民主编

仅供学习交流使用

请您阅读文章声明,默认同意该声明

第六章 半导体存储器

6.1 概述

6.1.1 存储器的分类

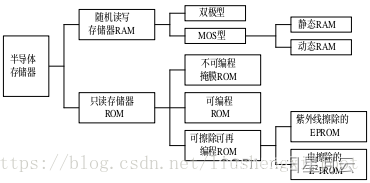

6.1.2 半导体存储器的分类

从应用角度可将半导体存储器分为两大类:

RAM: RAM中的信息断电后即丢失

ROM: 断电后信息不会丢失,常用来存放不需要改变的信息(如某些系统程序)

RAM 的分类:

- 双极型

- MOS型

双极型:

存取速度快、集成度较低、功耗较大、成本较高等特点,适用于对速度要求较高的高速缓冲存储器

MOS型:

MOS型存储器具有集成度高、功耗低、价格便宜等特点,适用于内存储器

MOS型存储器按信息存放方式又可分为:

1.静态RAM(Static RAM,简称SRAM)

2.动态RAM(Dynamic RAM,简称DRAM)

-

静态RAM:

SRAM存储电路以双稳态触发器为基础,状态稳定,只要不掉电,信息不会丢失。其优点是不需要刷新,控制电路简单,但集成度较低,适用于不需要大存储容量的计算机系统。 -

动态RAM:

DRAM存储单元以电容为基础,电路简单,集成度高,但也存在问题,即电容中的电荷由于漏电会逐渐丢失,因此DRAM需要定时刷新,它适用于大存储容量的计算机系统。

分类总览:

6.1.3 半导体存储器的主要技术指标

1.存储容量

(1)用字数 x 位数(即字长)表示,以位为单位。常用来表示存储芯片的容量,如1 K x 4位,表示该芯片有1 K个单元(1 K=1024),每个存储单元的长度为4位。

(2)用字节数表示容量,以字节为单位,如128 B,表示该芯片有 128个单元,每个存储单元的长度为8位。

2.存取时间

3.存储周期

4.功耗

5.可靠性

6.集成度

7.性能/价格比

6.1.4 半导体存储器芯片的基本结构

1.存储体

2.外围电路

6.2 典型半导体存储器介绍

6.2.1 静态随机读写存储器(SRAM)

1.SRAM的基本存储电路

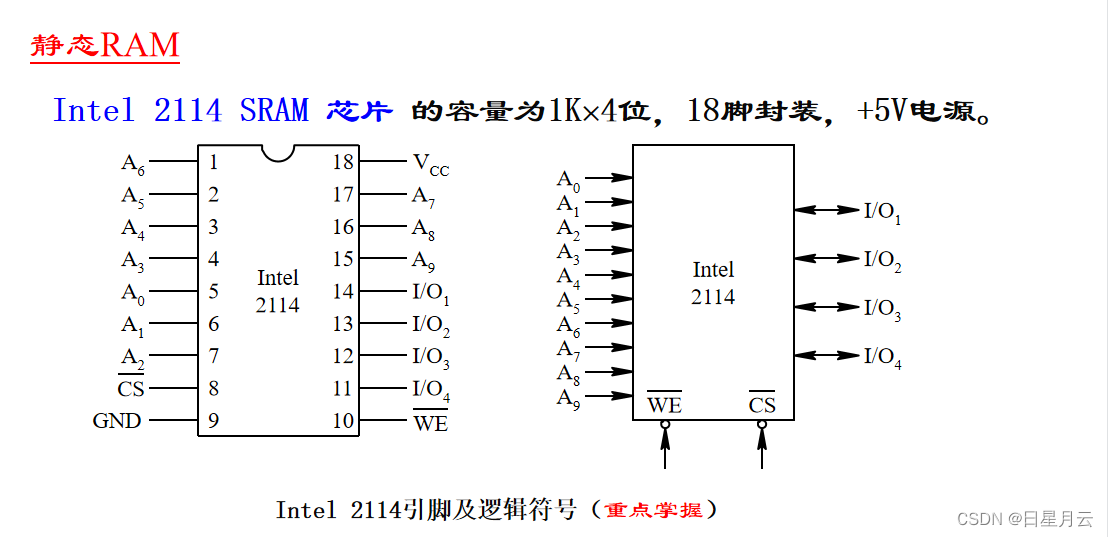

2.Intel2114SRAM芯片

6.2.2 动态随机读取存储器(DROM)

1.DRAM的基本存储电路

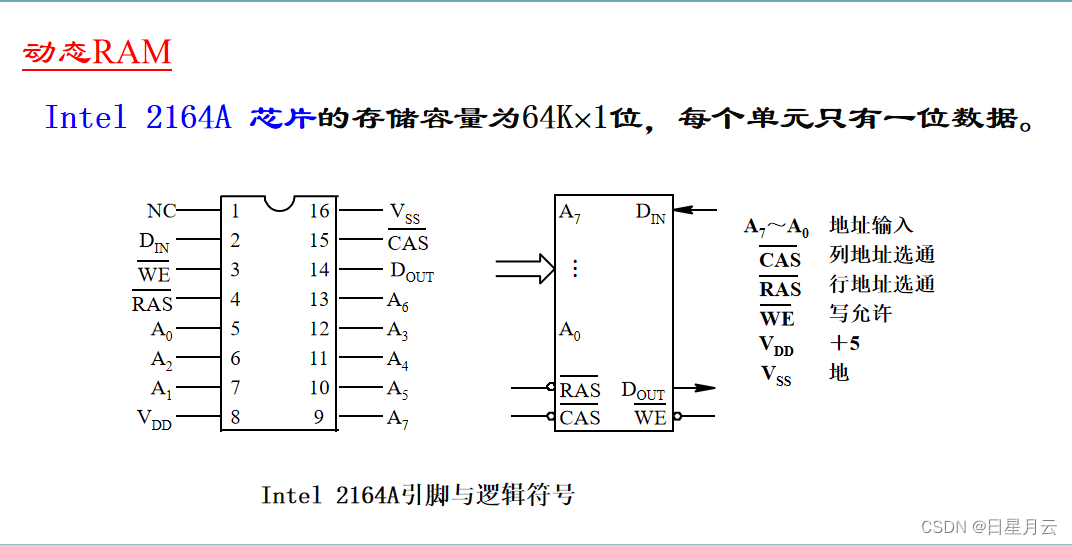

2.Inter 2164A DRAM芯片

6.2.3 掩膜式只读存储器(MROM)

6.2.4 可编程只读存储器(PROM)

6.2.5 可擦除的可编程只读存储器(EPROM、E2PROM)

1.EPROM和E2PROM简介

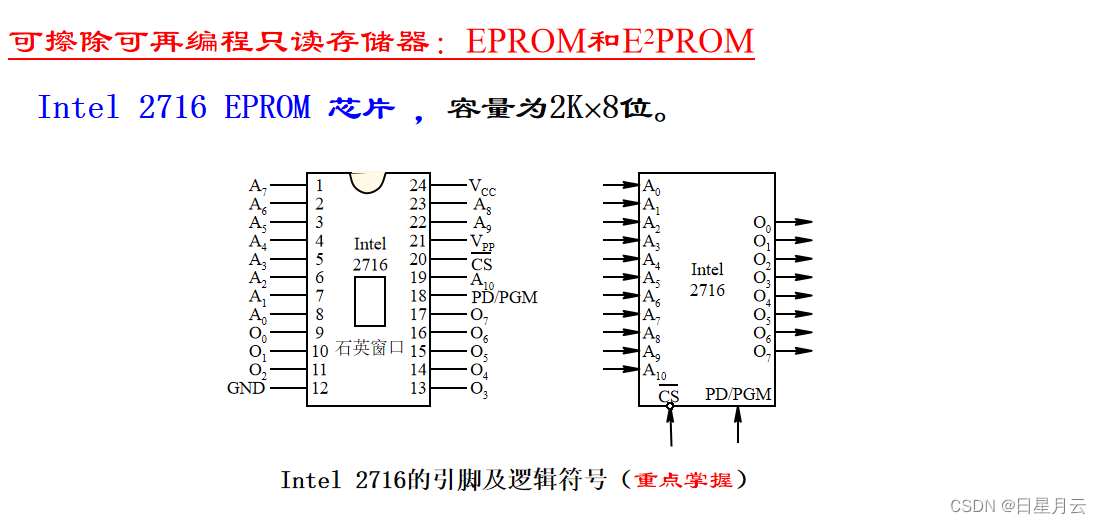

2.Inter 2716 EPROM芯片

3.Inter 2816 E2PROM

6.2.6 闪速存储器(Flash Memory)

6.3 存储器系统设计

每一个存储器芯片的容量都是有限的 ,而且其字长有时候也不能正好满足计算机系统对字长的要求。因此,微机系统的存储器总是由多个存储器芯片共同构成的。对存储芯片进行扩展与连接时要考虑两个方面的内容:

1.如何用容量较小的,字长较短的芯片组成满足系统容量要求的存储器

2.存储器如何与CPU连接

6.3.1 存储芯片的扩展

几个重要结论:(牢记)

1.存储器位宽表示每个地址下有多少位数据,与它的数据线根数相等;

2.存储器的地址线根数(N)决定了它的地址编号范围(2^N)

3.存储容量=2^地址线×数据线

4.字数=2^地址线

字长=数据线长度

存储容量 = 2^地址线×数据线

存储容量 = 字数 x 位数

字拓展(与CS有关) ,位拓展(与数据线有关) ,其余线路都并联即可!

存储芯片的扩展包括

1. 位扩展

位扩展 :将各芯片的地址线、片选CS、读/写控制线相应并联,而数据线要分别引出。

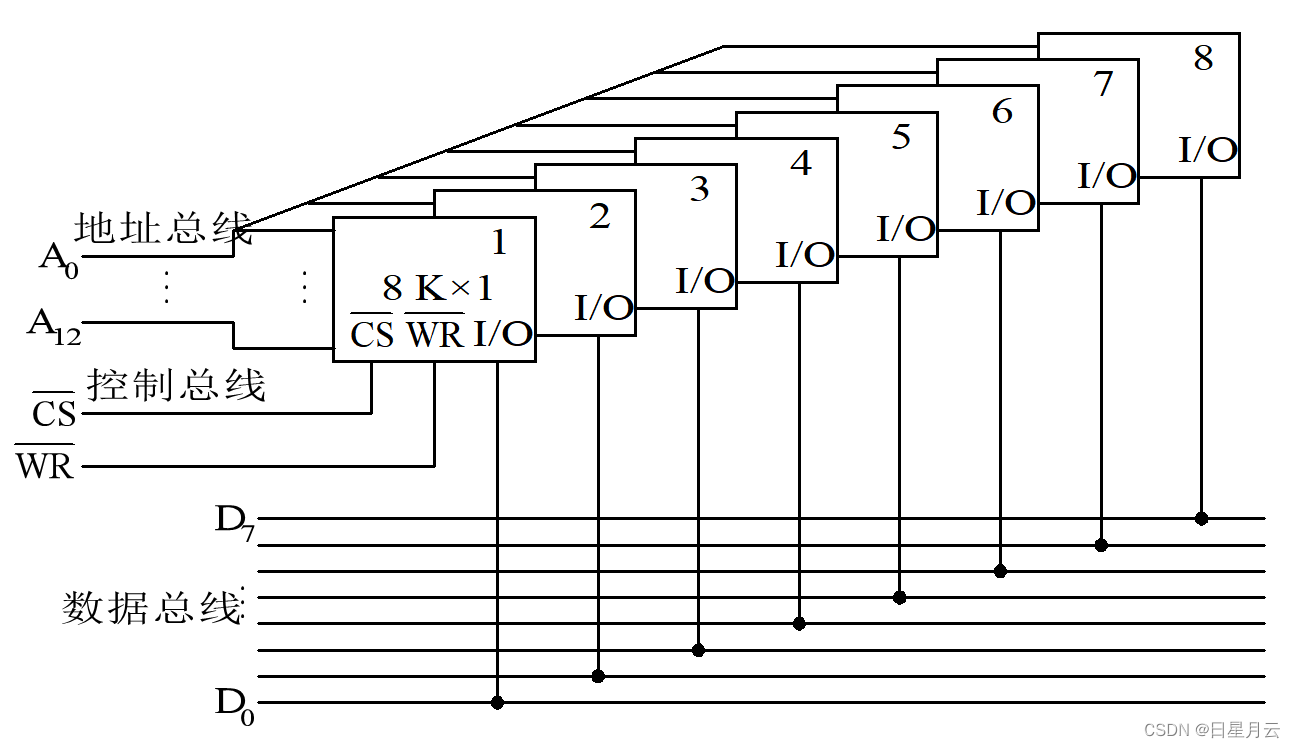

位扩展是指存储芯片的字(单元)数满足要求而位数不够,需对每个存储单元的位数进行扩展。下图给出了使用8片8 K1的RAM芯片通过位扩展构成8K x 8的存储器系统的连线图。

用8KX1位芯片组成8KX8位的存储器

说明 : 由于存储器的字数与存储器芯片的字数一致,8 K=2^13,故只需13根地址线(A12 x A0)对各芯片内的存储单元寻址,每一芯片只有一条数据线,所以需要8片这样的芯片,将它们的数据线分别接到数据总线(D7~ D0)的相应位。在此连接方法中,每一条地址线有8个负载,每一条数据线只有一个负载。位扩展法中,所有芯片都应同时被选中,各芯片CS端可直接接地,也可并联在一起,根据地址范围的要求,与高位地址线译码产生的片选信号相连。对于此例,若地址线A0~ A12上的信号为全0,即选中了存储器0号单元,则该单元的8位信息是由各芯片0号单元的1位信息共同构成的。

可以看出,位扩展的连接方式是将各芯片的地址线、片选CS、读/写控制线相应并联,而数据线要分别引出。

字扩展

字扩展 :将各芯片的地址线、数据线、读/写控制线并联,而由片选信号来区分各片地址

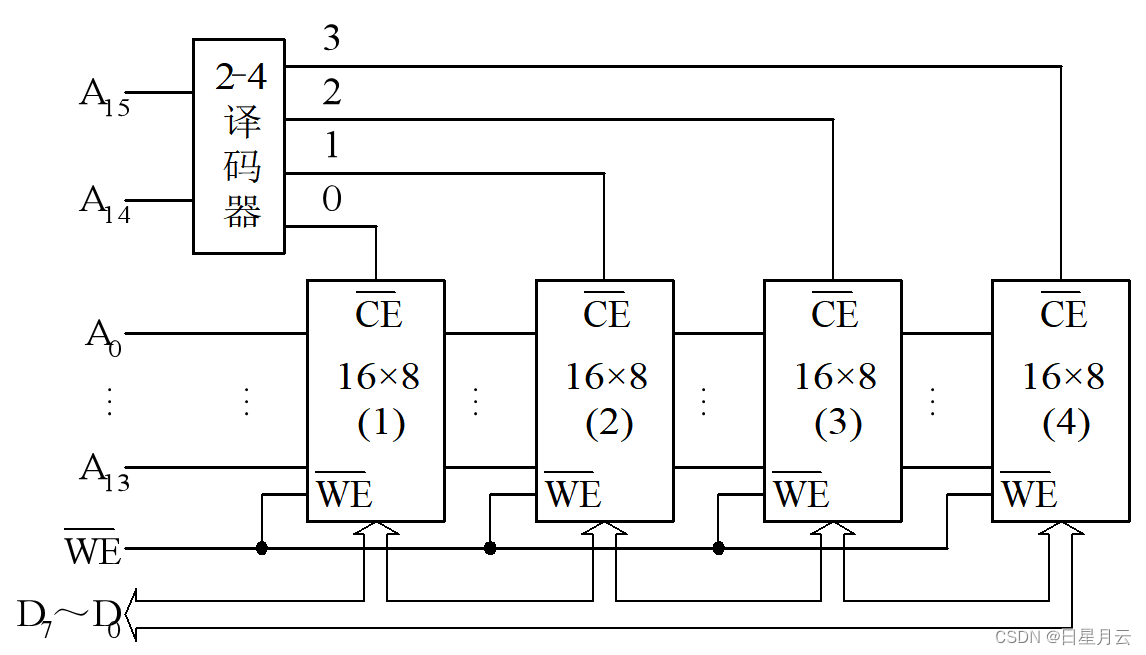

字扩展用于存储芯片的位数满足要求而字数不够的情况,是对存储单元数量的扩展。图6.18给出了用4个16 KX8芯片经字扩展构成一个64KX8存储器系统的连接方法。

用16Kx8位芯片组成64Kx8位的存储器

说明: 图中4个芯片的数据端与数据总线D7D0相连;地址总线低位地址A13A0与各芯片的14位地址线连接,用于进行片内寻址;为了区分4个芯片的地址范围,还需要两根高位地址线A14、A15经2–4译码器译出4根片选信号线,分别和4个芯片的片选端相连。

可以看出,字扩展的连接方式是将各芯片的地址线、数据线、读/写控制线并联,而由片选信号来区分各片地址。也就是将低位地址线直接与各芯片地址线相连,以选择片内的某个单元;用高位地址线经译码器产生若干不同片选信号,连接到各芯片的片选端,以确定各芯片在整个存储空间中所属的地址范围。

3. 字位同时扩展

字位同时扩展:前面相除的为组的数量,后面相除的为组内的数量。组内采用位扩展法,组间采用字扩展法

字数和位数都需要扩展的情况

若使用 l x k 位存储器芯片构成一个容量为M x N位(M>l,N>k)的存储器,那么这个存储器共需要(M/l)x(N/k)个存储器芯片。连接时可将这些芯片分成(M/l)个组,每组有(N/k)个芯片,组内采用位扩展法,组间采用字扩展法。

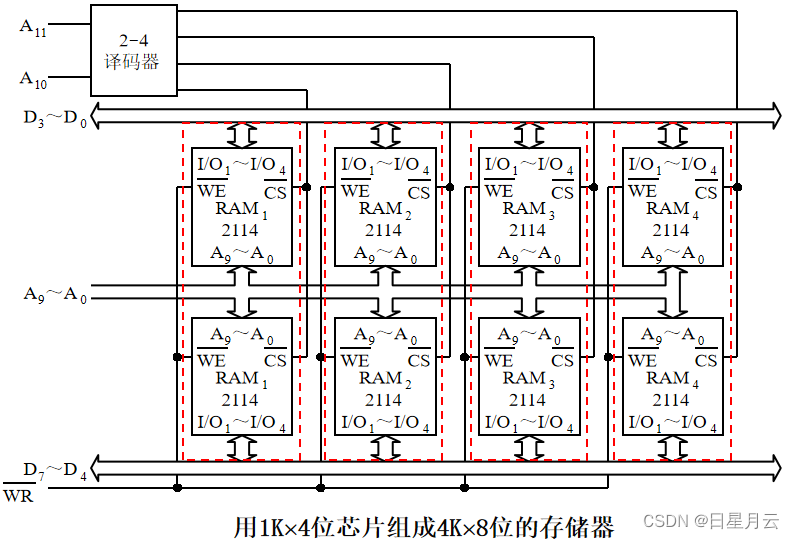

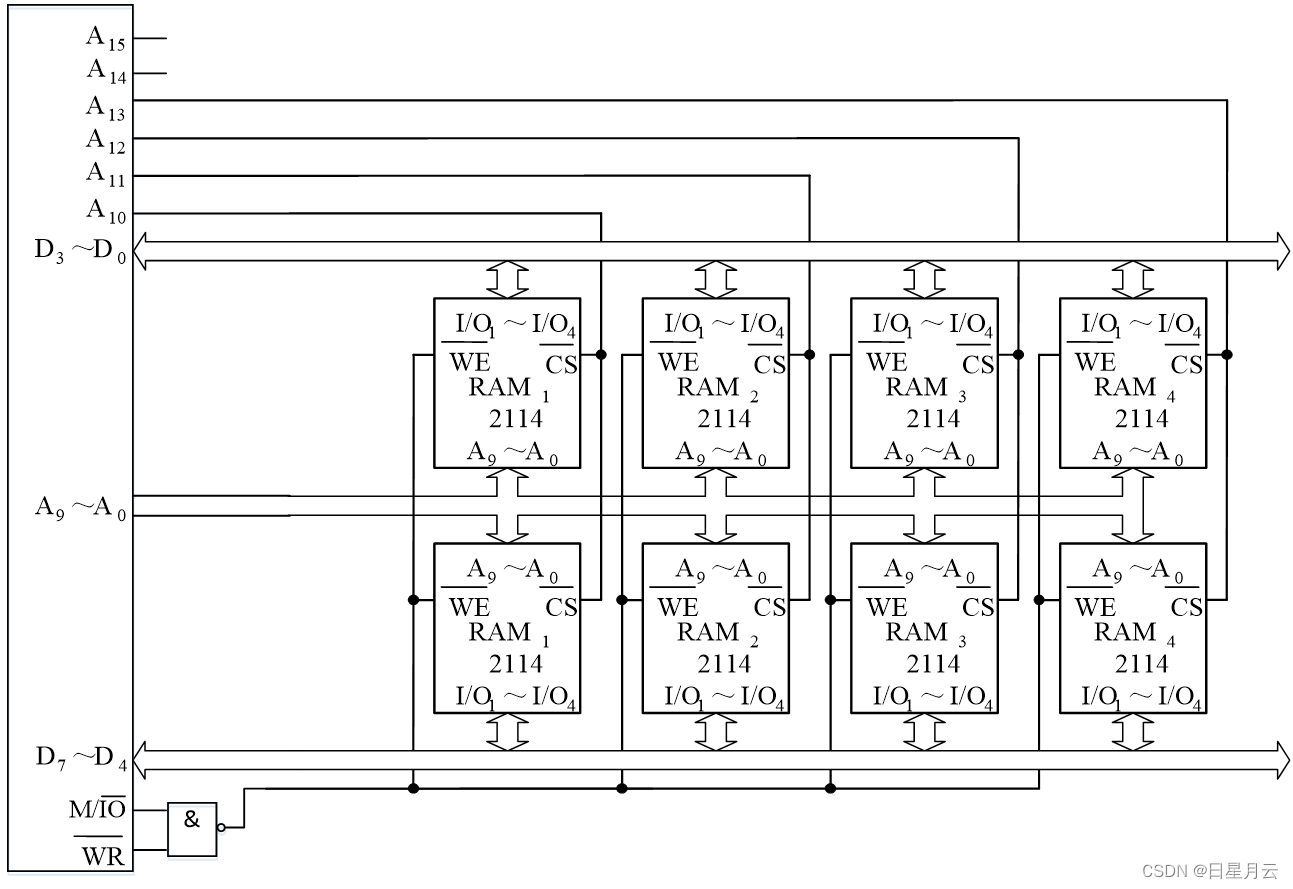

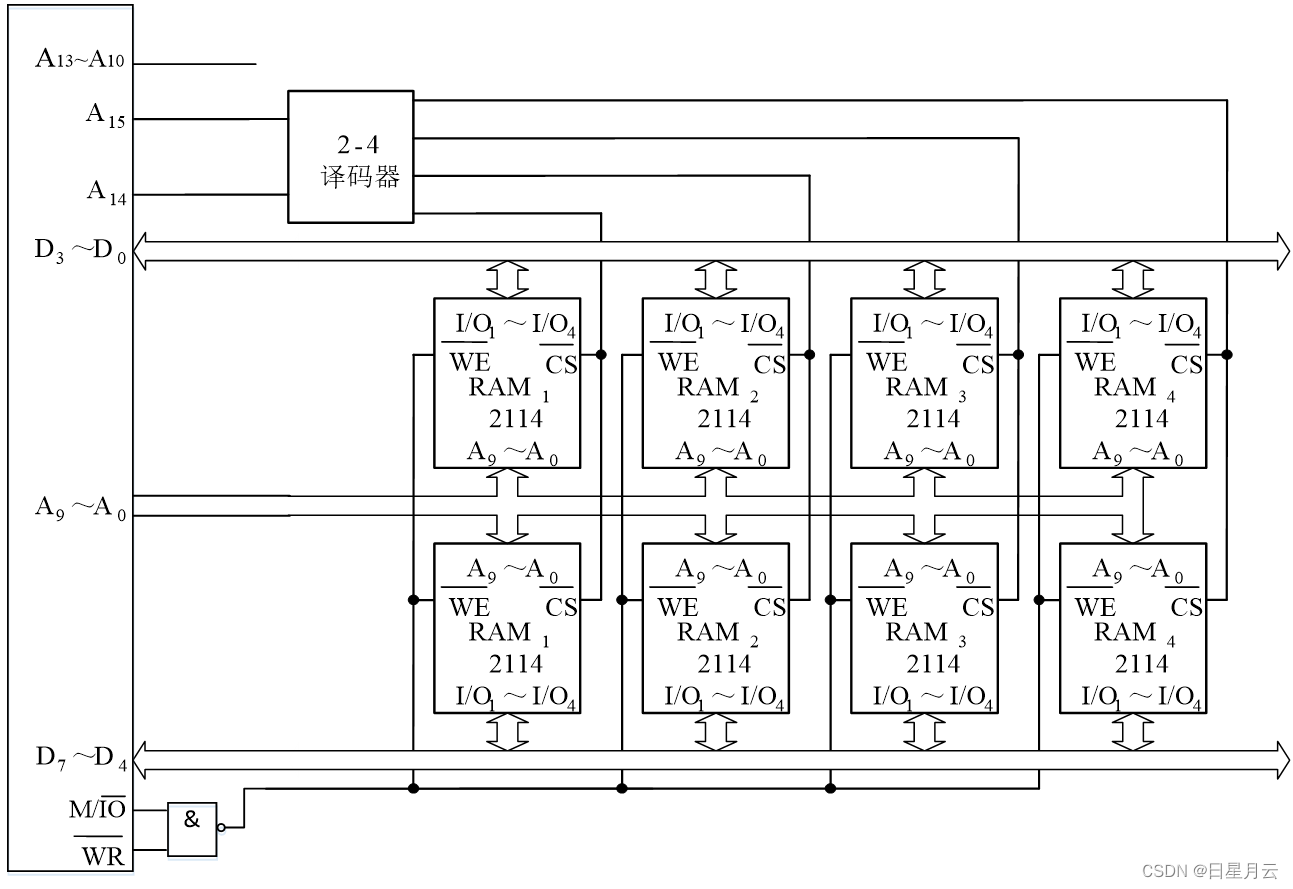

图6.19给出了用2114(1Kx4)RAM芯片构成4Kx8存储器的连接方法。

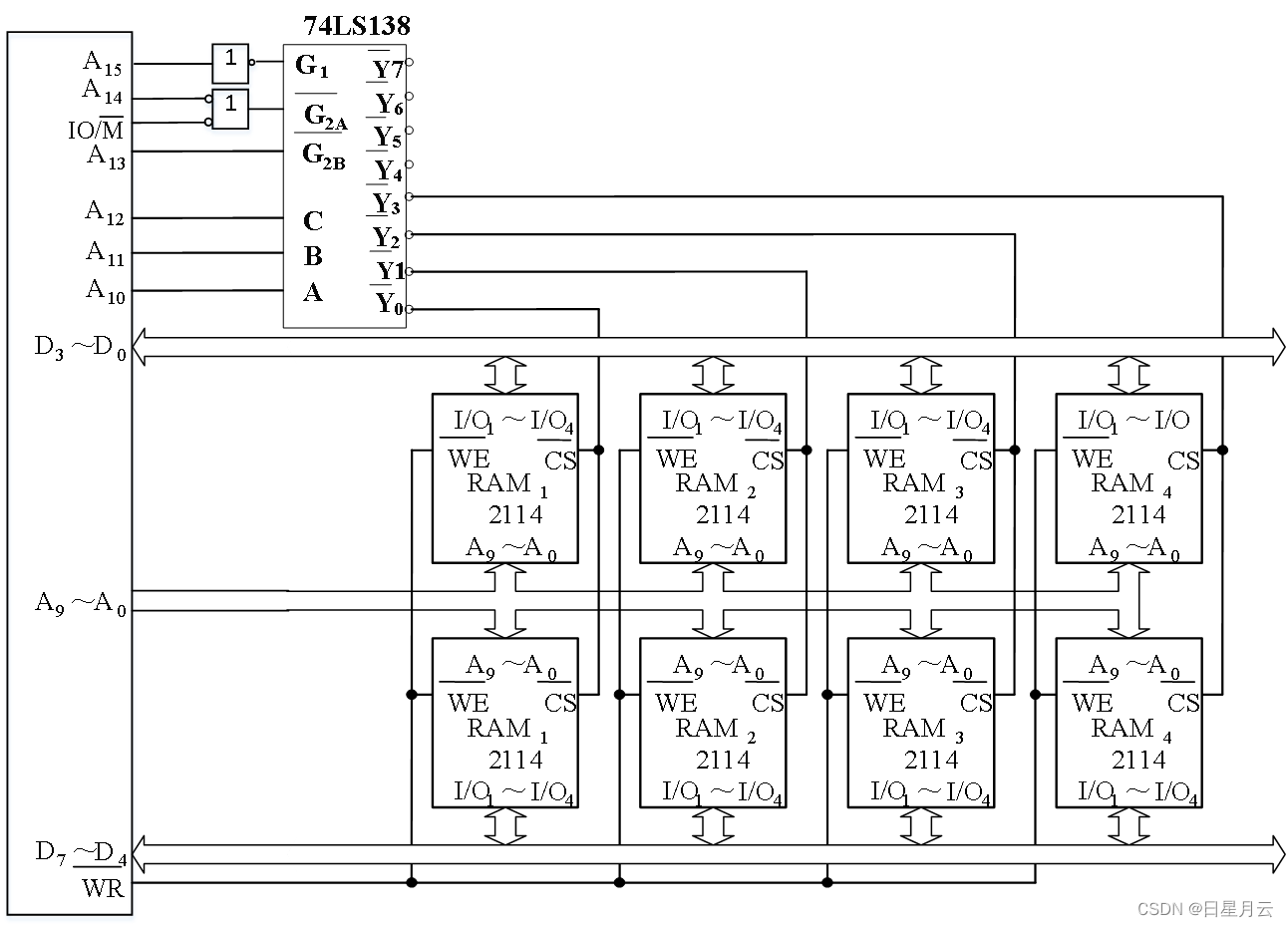

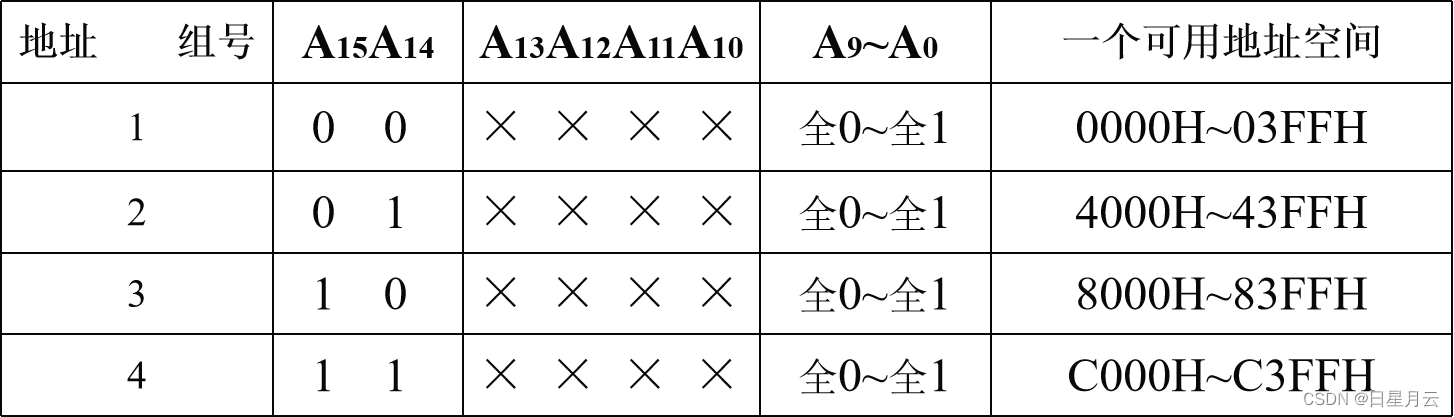

说明:图中将8片2114芯片分成了4组(RAM1、RAM2、RAM3和RAM4),每组2片。组内用位扩展法构成1K8的存储模块,4个这样的存储模块用字扩展法连接便构成了4Kx8的存储器。用A9A0 10根地址线对每组芯片进行片内寻址,同组芯片应被同时选中,故同组芯片的片选端应并联在一起。本例用2–4译码器对两根高位地址线A10~ A11译码,产生4根片选信号线,分别与各组芯片的片选端相连。

6.3.2 存储器与CPU的连接

CPU对存储器进行访问时,首先要在地址总线上发地址信号,选择要访问的存储单元,还要向存储器发出读/写控制信号,最后在数据总线上进行信息交换。因此,存储器与CPU的连接实际上就是存储器与三总线中相关信号线的连接。

1.存储器与控制总线的连接

在控制总线中,与存储器相连的信号线为数不多,如8086/8088最小方式下的M/IO(8088为M/IO)、RD和WR,最大方式下的MRDC、MWTC、IORC和IOWC等,连接也非常简单,有时这些控制线(如M/IO)也与地址线一同参与地址译码,生成片选信号

2.存储器与数据总线的连接

8086 CPU的数据总线有16根 ,其中高8位数据线D15D8接存储器的高位库(奇地址库),低8位数据线D7D0接存储器的低位库(偶地址库),根据BHE(选择奇地址库)和A0(选择偶地址库)的不同状态组合决定对存储器做字操作还是字节操作。

3.存储器与地址总线的连接

对于由多个存储芯片构成的存储器,其地址线的译码被分成

1. 片内地址译码:用于对各芯片内某存储单元的选择

2. 片间地址译码 :用于产生片选信号,

以决定每一个存储芯片在整个存储单元中的地址范围,避免各芯片地址空间的重叠

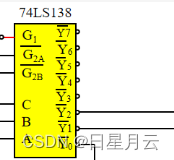

片内地址译码在芯片内部完成,连接时只需将相应数目的低位地址总线与芯片的地址线引脚相连。片选信号通常要由高位地址总线经译码电路生成。地址译码电路可以根据具体情况选用各种门电路构成,也可使用现成的译码器,如 74LS138(3–8译码器)等。

74ls138

引脚图

真值表

以下内容截取讲课PPT

片间地址译码一般有线选法和译码法两种。

线选法:直接将某一高位地址线与某个存储芯片片选端连接。

特点: 简单明了,无需另外增加电路;

存储芯片的地址范围会重叠或不连续;不能充分有效地利用存储空间。

译码法:使用译码电路将高位地址进行译码,以其译码输出作为存储芯片的片选信号;分为全译码法和部分译码法。

特点: 连接复杂,但能有效地利用存储空间;

译码电路可以使用现有的译码器芯片。

线选法:存储芯片的地址范围会有重叠或断续。

线选法:存储芯片的地址范围有重叠或有断续 。

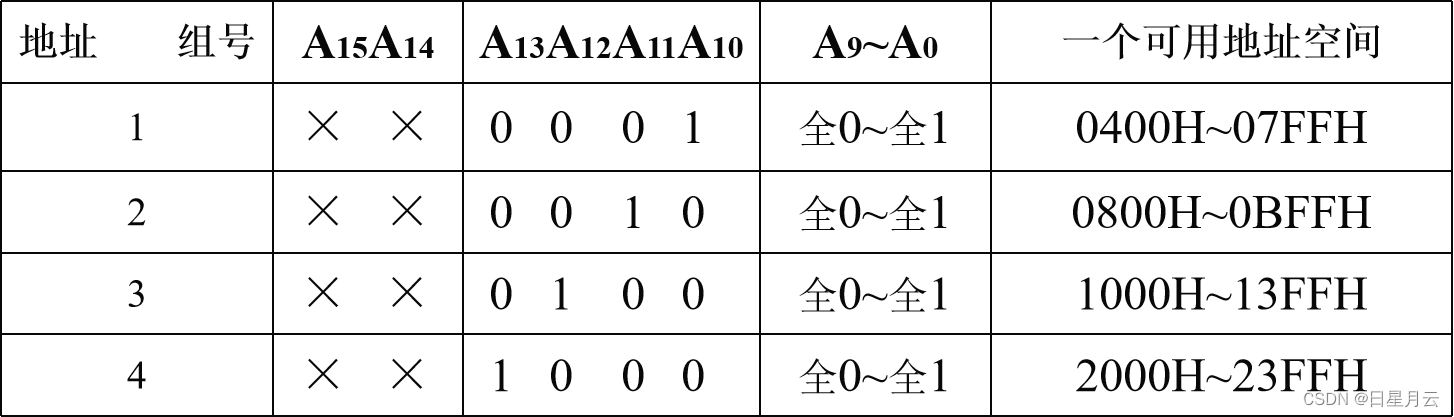

线选法地址空间

全译码法:高位地址线全部参与片间地址译码;不会产生地址重叠的存储区域,每个存储单元的地址都是惟一的。

全译码法:高位地址线全部参与片间地址译码;不会产生地址重叠的存储区域,每个存储单元的地址都是惟一的。

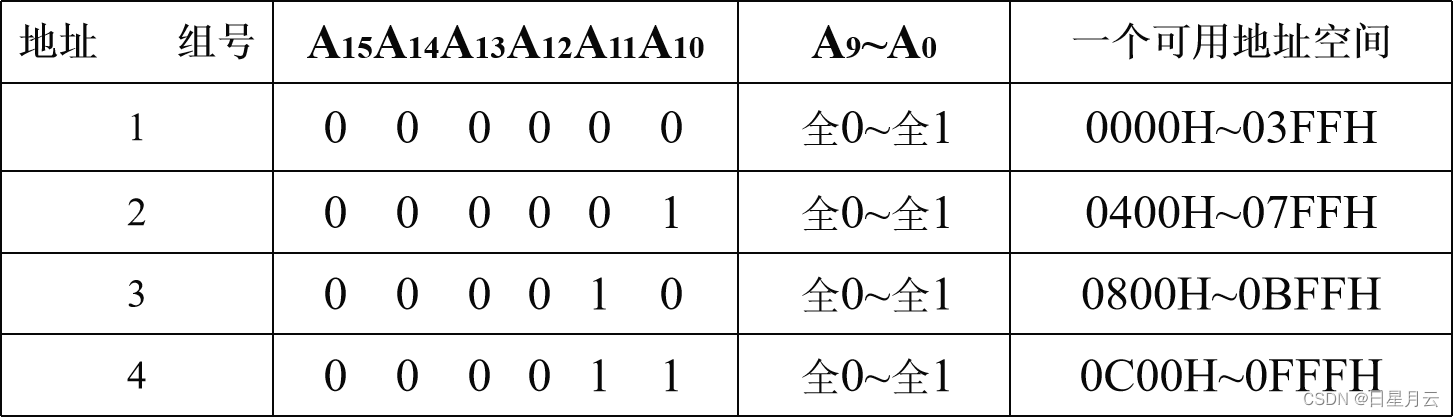

全译码法地址空间

部分译码法:部分高位地址线参与片间地址译码;相较全译码法能简化译码电路,但会产生地址重叠或不连续。

部分译码法:部分高位地址线参与片间地址译码;相较全译码法能简化译码电路,但会产生地址重叠或不连续。

部分译码法地址空间

以上内容截取讲课PPT

6.3.3 基于8086/8088 CPU 的存储器连接举例

推荐

计算机组成原理之CPU与存储器的连接

以下内容截取讲课PPT

与8位CPU的连接实例

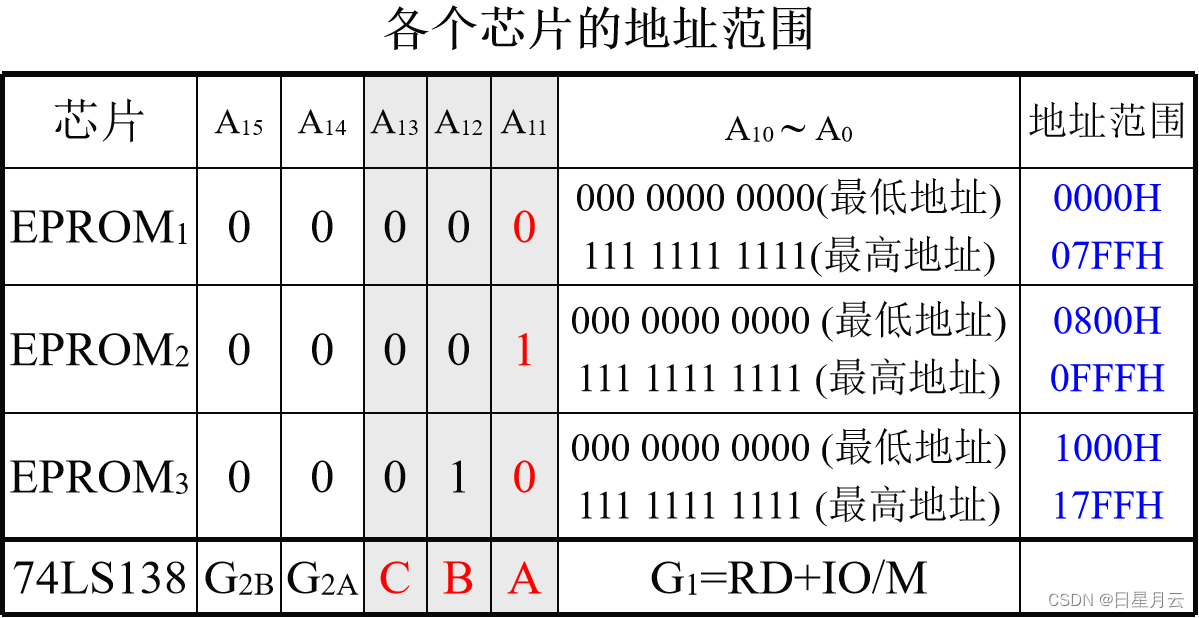

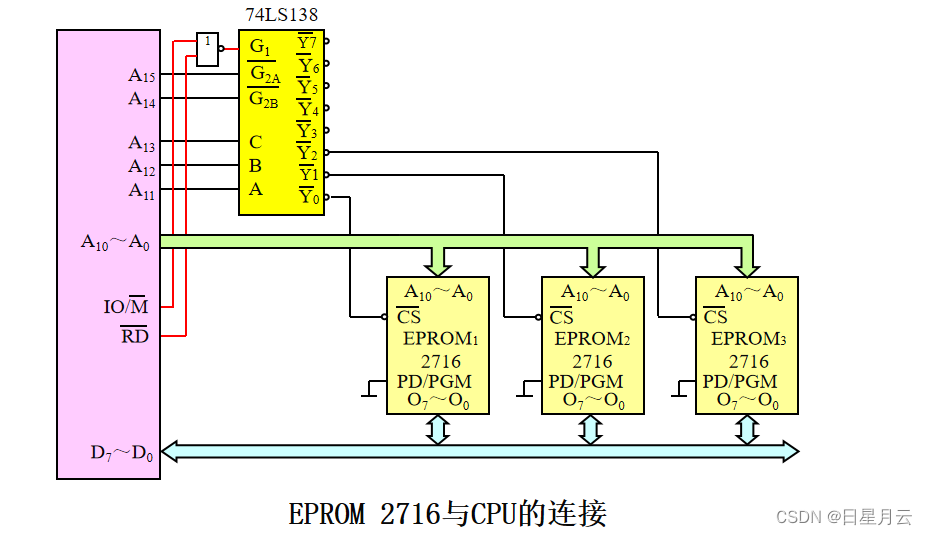

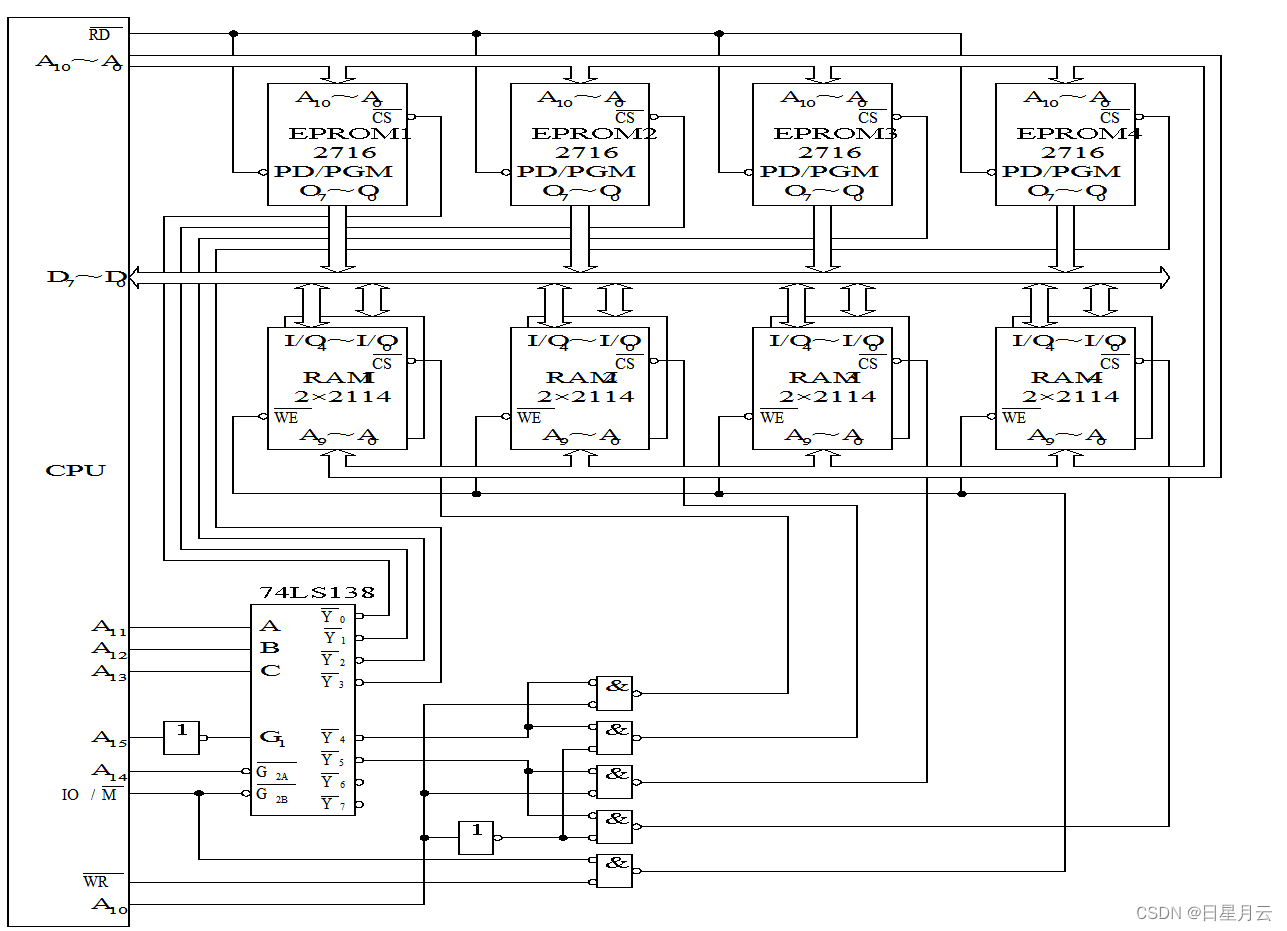

【例1】 设某8位机系统需装6KB的ROM,地址范围安排在0000H17FFH。请画出使用EPROM芯片2716构成的连接线路图。

【分析】 2716 EPROM 芯片:

- 容量为2K×8位,需用3片进行字扩展;

- 8条数据线(O7O0),与CPU的数据总线(D7D0)连接;

- 11条地址线(A10A0)与CPU的低位地址线(A10A0)连接;

- 片选信号(CS)的连接需考虑两个问题:

- 与CPU高位地址线(A15A11)和控制信号(IO/!M、!RD)如何连接;

- 根据给定的地址范围如何连接。

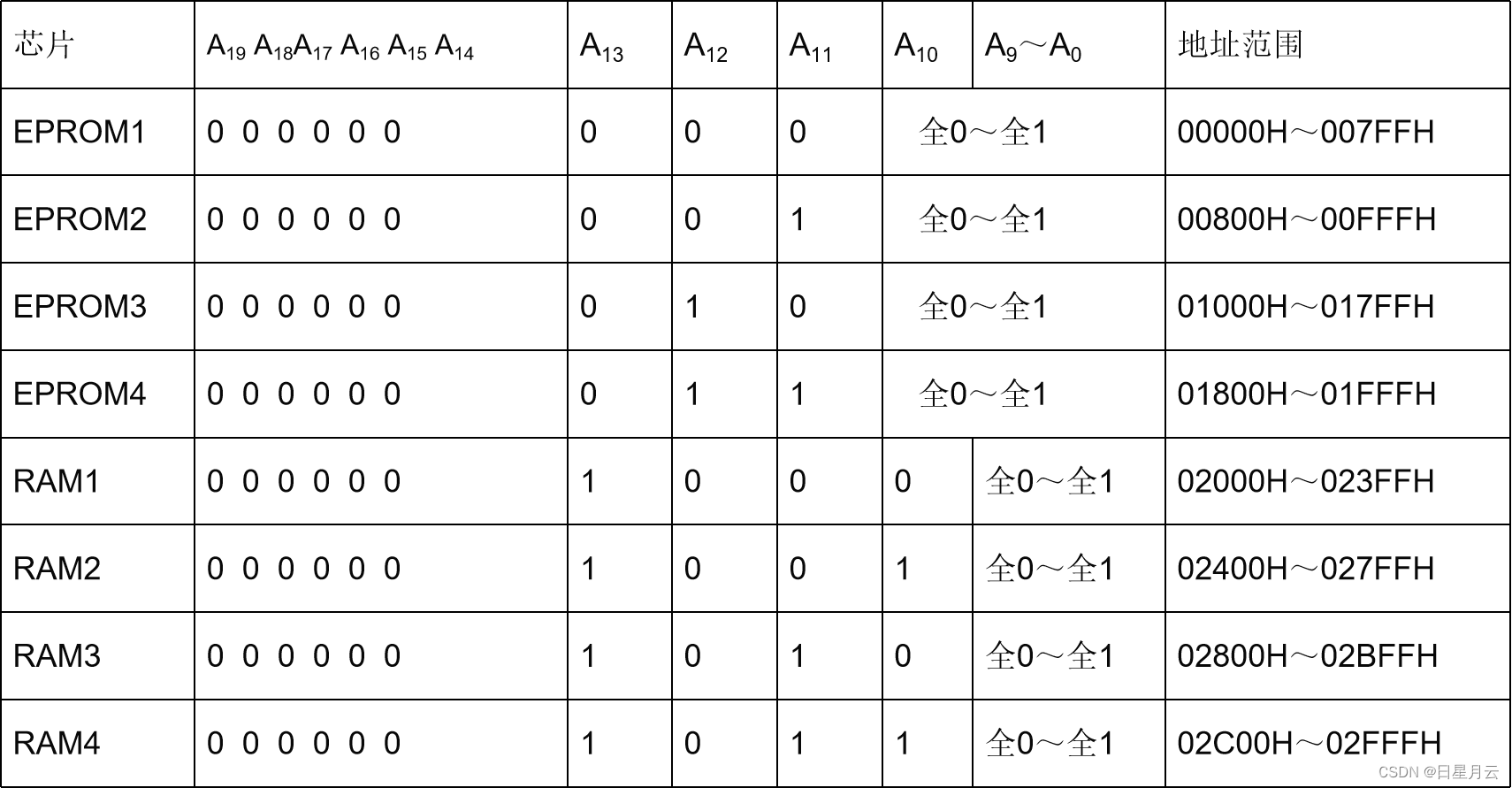

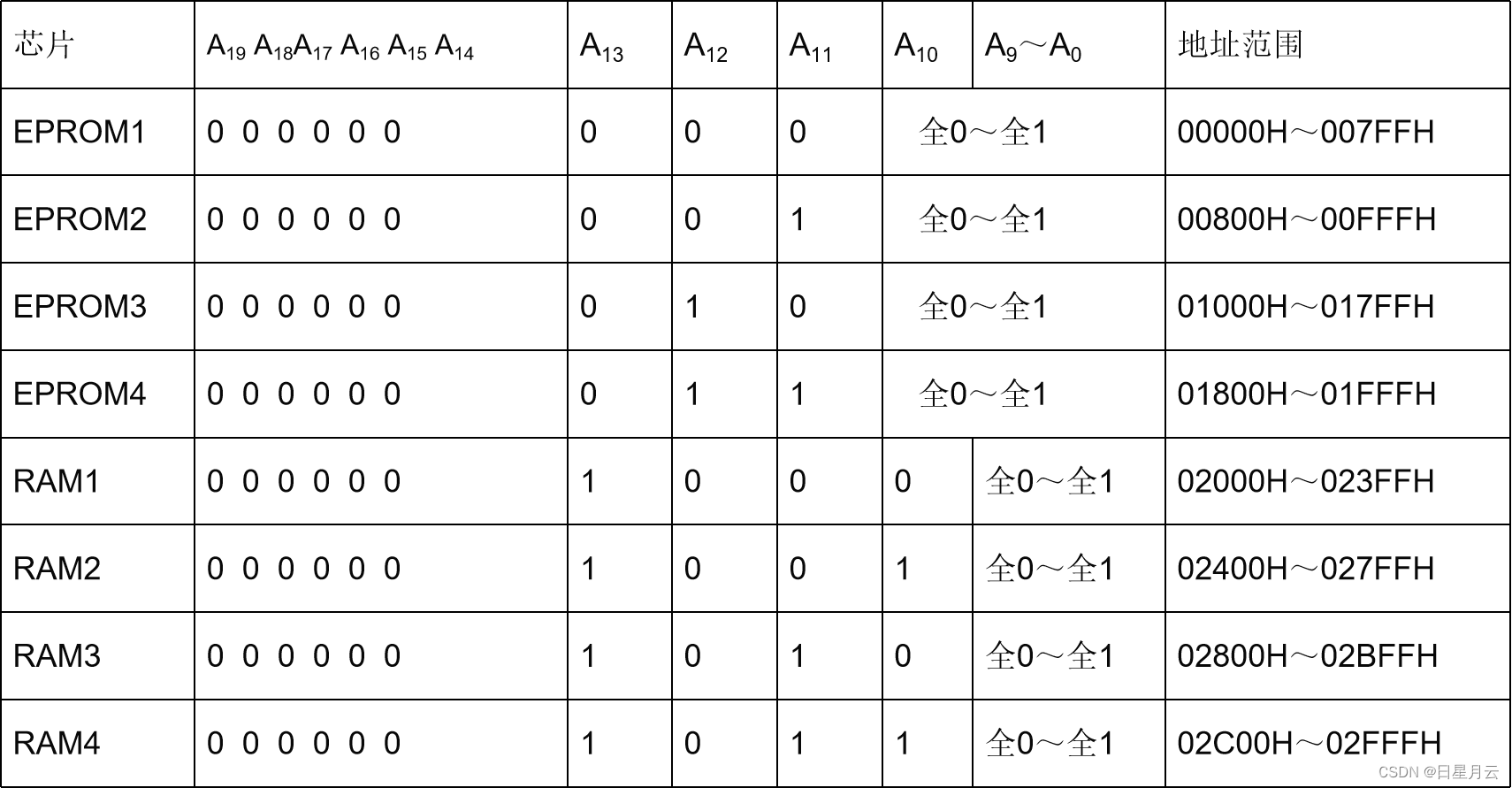

若采用译码法,根据给定的地址范围,可列出3片EPROM的地址范围如下表:

与16位CPU的连接实例

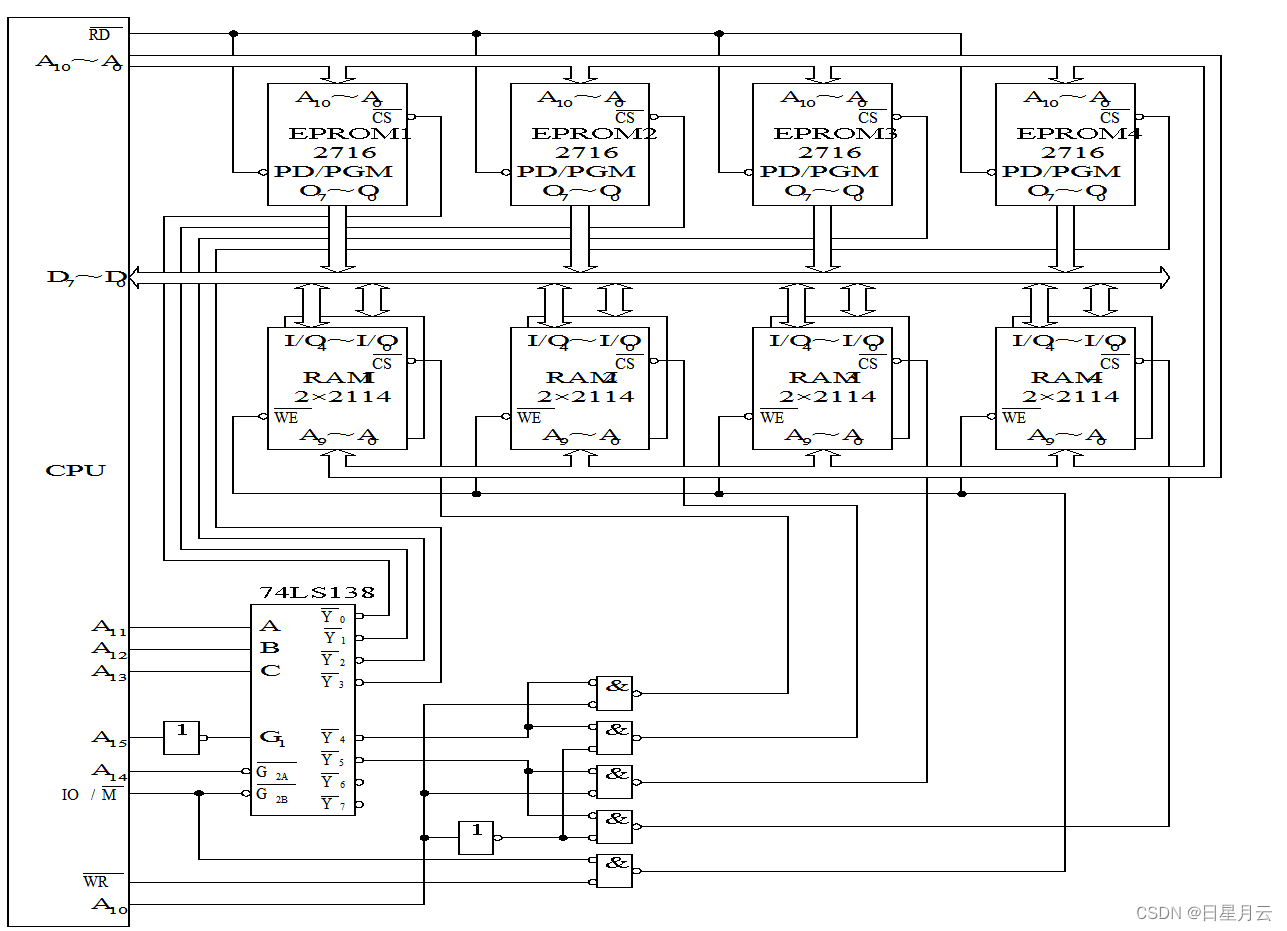

例2 有一8088微机系统,其内存地址空间中00000H~01FFFH的8K字节为EPROM,02000H~02FFFH的4 K字节为静态RAM,03000H~03FFFH的4 K字节为待扩存储空间。要求EPROM用Intel 2716,RAM用Intel 2114,用74LS138译码器作片选控制,试画出其连接图。

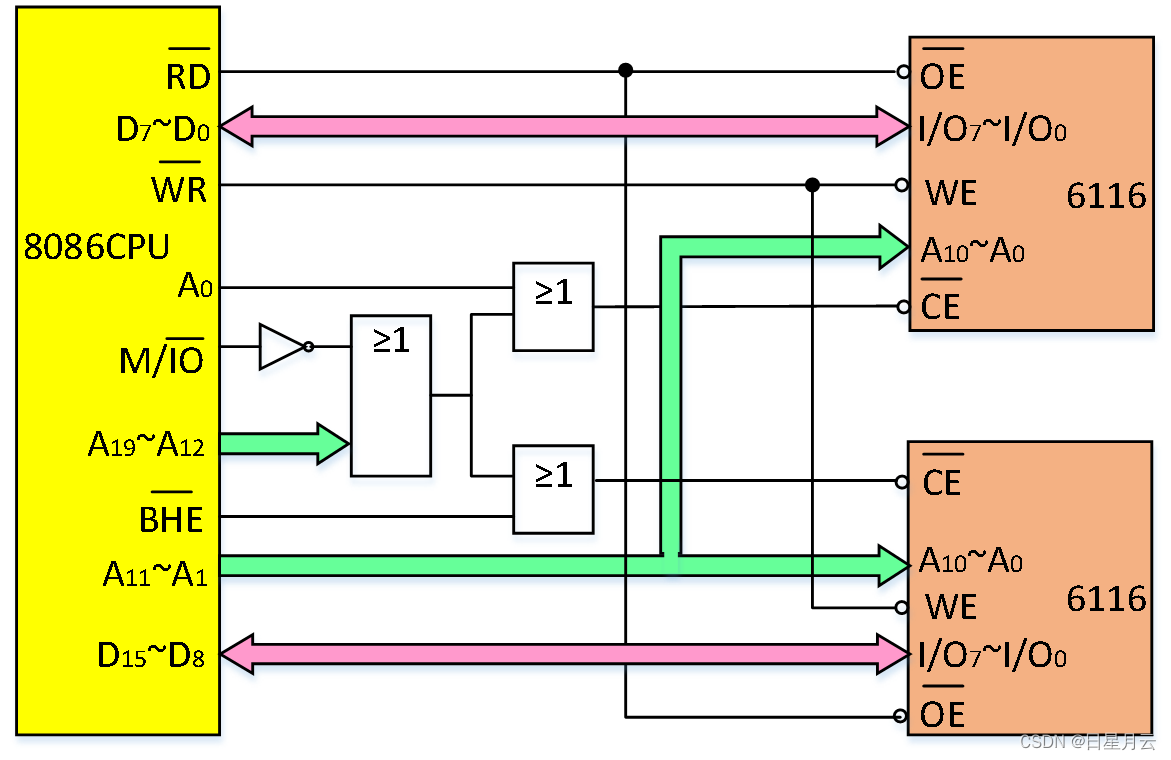

【例3】 在某8086微机系统中,采用Intel 6116 RAM存储器芯片构成2K字的存储器,试画出存储器芯片的连接线路图。

【分析】

- 8086 CPU的数据总线为16位;存储器构成分为高位(奇地址)库和低位(偶地址)库;

- 6116芯片的容量为2K×8位,需用2片芯片;

- CPU数据总线的高8位(D15~ D8)和低8位(D7~ D0)分别与两片6116的数据输入/输出线(I/O7~ I/O0)相连;

- CPU低位地址线(A11~ A1)接至两片6116的(A10~ A0);

*高位地址线、地址信号A0和控制信号!BHE用于形成两片6116的片选信号(!CE)。

6116与CPU的连接

以上内容截取讲课PPT

步骤

例2 有一8088微机系统,其内存地址空间中00000H~01FFFH的8K字节为EPROM,02000H~02FFFH的4 K字节为静态RAM,03000H~03FFFH的4 K字节为待扩存储空间。要求EPROM用Intel 2716,RAM用Intel 2114,用74LS138译码器作片选控制,试画出其连接图。

分析如下

(1)

ROM 8Kx8 2716 2K×8芯片,需4片,做字扩展,片内寻址线11根

RAM 4kx8 2114 1K×4芯片,需8片,做字位扩展,片内寻址线10根

(2)地址范围: A15 A14 A13 A12 A11 A10 A9~A0

0k

ROM1:0000H~07FFH 0 0 0 0 0 全0~全1

+2K

ROM2:0800H~0FFFH 0 0 0 0 1 全0~全1

+2K

ROM3:1000H~17FFH 0 0 0 1 0 全0~全1

+2K

ROM4:1800H~1FFFH 0 0 0 1 1 全0~全1

8k

RAM1、2:2000H~23FFH 0 0 1 0 0 0 全0~全1

+1K

RAM3、4:2400H~27FFH 0 0 1 0 0 1 全0~全1

+1K

RAM5、6:2800H~2BFFH 0 0 1 0 1 0 全0~全1

+1K

RAM7、8:2C00H~2FFFH 0 0 1 0 1 1 全0~全1

12k

(3)

A13 A12 A11 3:8译码器 译码输入 (一级译码)

0 0 0 ROM1 :Y0

0 0 1 ROM2 :Y1

0 1 0 ROM3 :Y2

0 1 1 ROM4 :Y3

1 0 0 RAM1、2 :Y4 与 A10 (二级译码) 此与是负逻辑与

0

1 0 0 RAM3、4 :Y4 与 A10

1

1 0 1 RAM5、6 :Y5 与 A10

0

1 0 1 RAM7、8 :Y5 与 A10

1

(4)画图连接

负逻辑与门

符号

就是正逻辑与门的输入输出端加小圆圈

真值表

先说正逻辑与门

正逻辑与门真值表

0无效1有效

只有全1才为1

| A | B | C |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

负逻辑与门真值表

0有效1无效

只有全0才为0

| A | B | C |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

其和正逻辑的或门真值表相同

最后

请您阅读文章声明,默认同意该声明

打赏通道

本文详细介绍了半导体存储器的分类,包括RAM和ROM,以及它们各自的特点和应用。RAM分为静态和动态两种,SRAM速度快但集成度低,DRAM集成度高但需定期刷新。此外,还讲解了存储器系统设计,如存储芯片的位扩展和字扩展,以及如何通过地址译码实现存储器与CPU的有效连接。最后,通过实例展示了基于8086/8088CPU的存储器连接方法。

本文详细介绍了半导体存储器的分类,包括RAM和ROM,以及它们各自的特点和应用。RAM分为静态和动态两种,SRAM速度快但集成度低,DRAM集成度高但需定期刷新。此外,还讲解了存储器系统设计,如存储芯片的位扩展和字扩展,以及如何通过地址译码实现存储器与CPU的有效连接。最后,通过实例展示了基于8086/8088CPU的存储器连接方法。

5397

5397

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?