1 将已经画好的原理图更新到PCB中(点击应用修改)

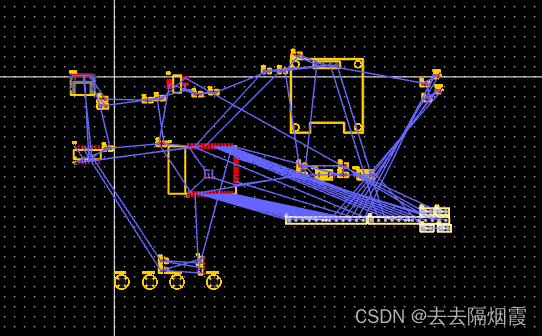

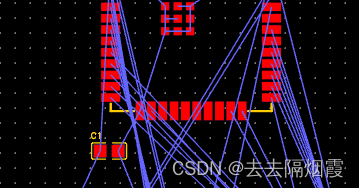

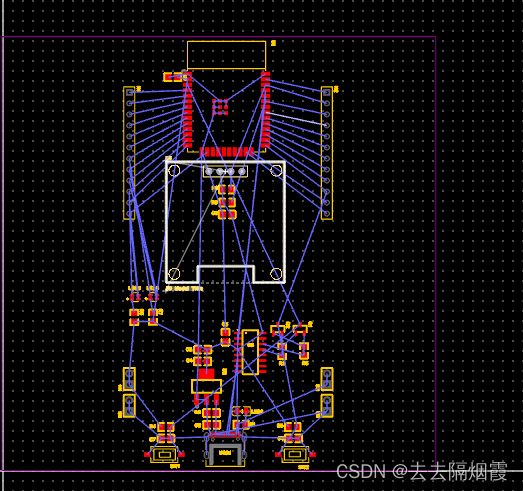

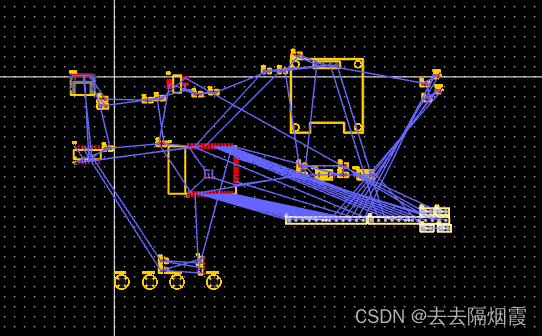

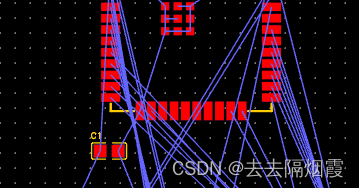

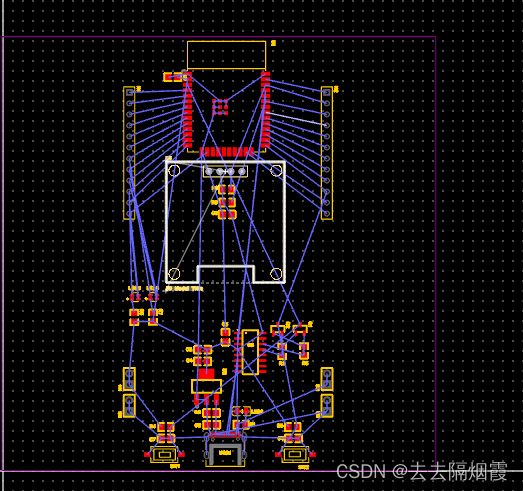

2 一开始PCB是杂乱的,需要回到原理图,框选各个模块,然后按住Ctrl+Shift+X会自动在PCB显示这个部分,然后把各个部分分开

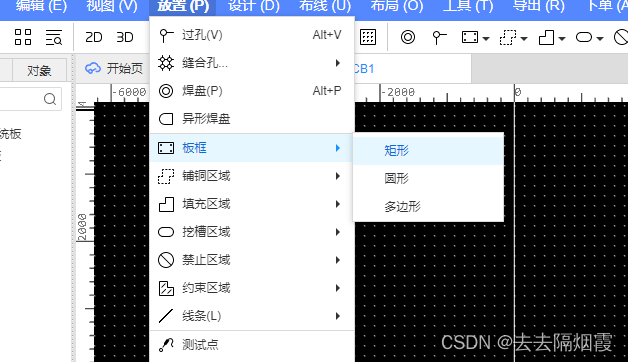

3 PCB画板需要有板框(嘉立创每个月都i有100X100mm免费打板)

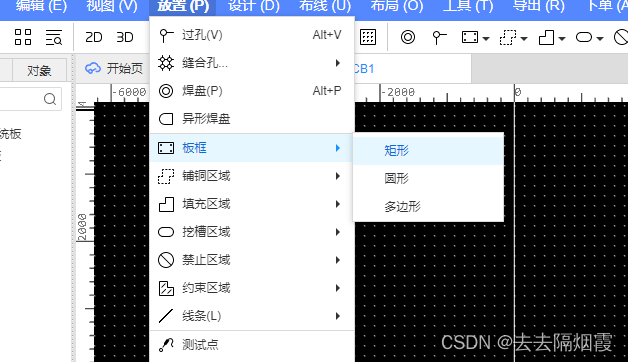

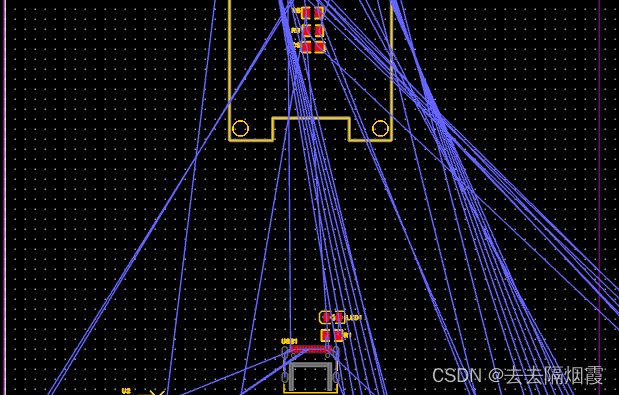

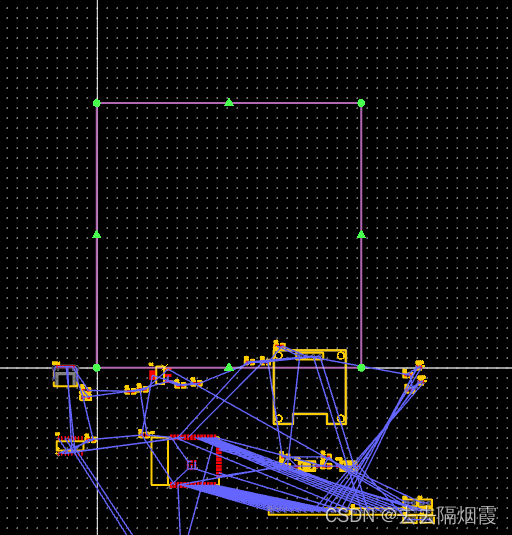

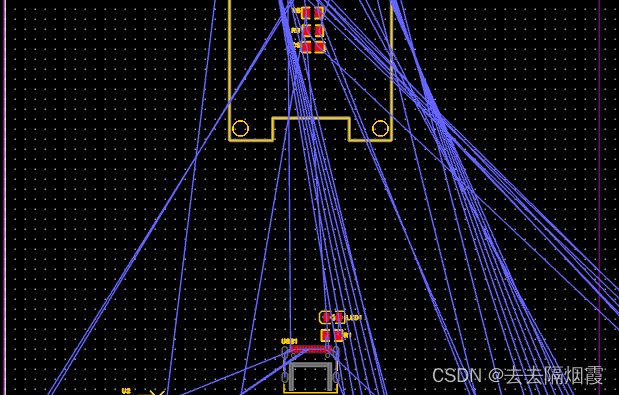

4进行布局

一般情况下优先考虑主控芯片,大器件以及供电接口

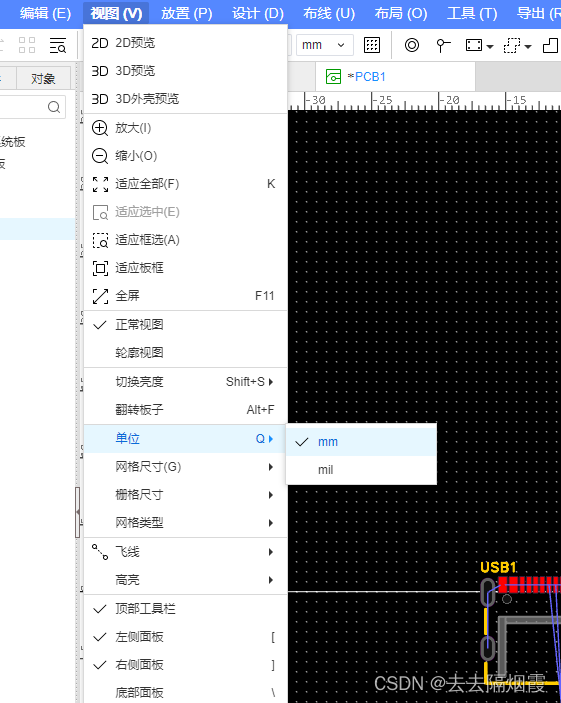

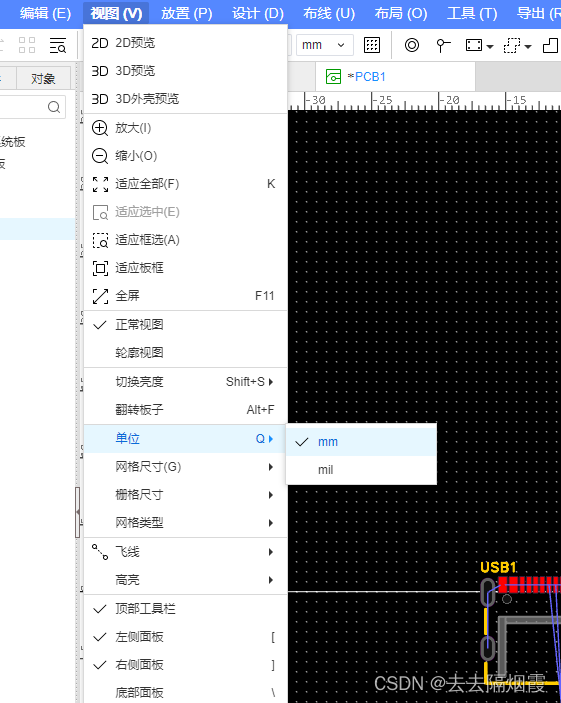

移动芯片更改栅格位置

滤波电容一般都是靠近主控芯片摆放

typ-c建议放置在下面

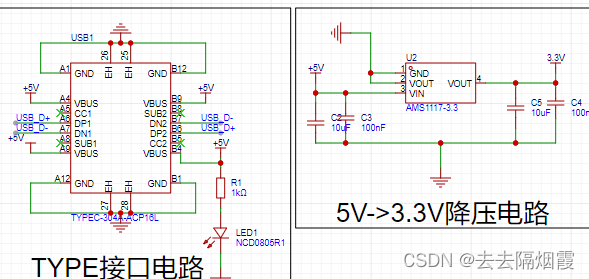

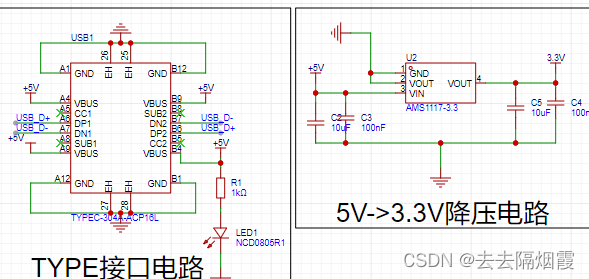

画PCB也要按照原理图来画(元器件摆放位置)

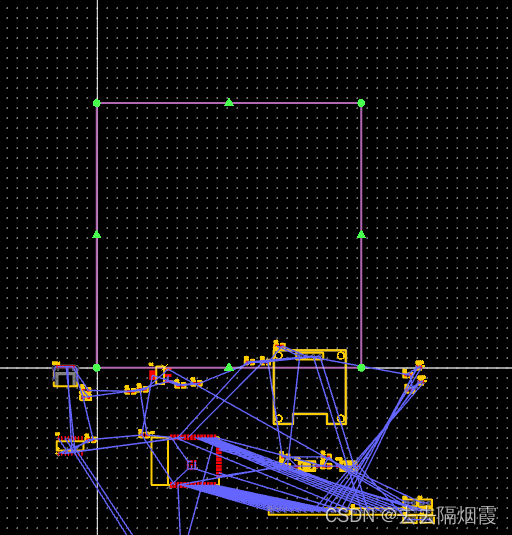

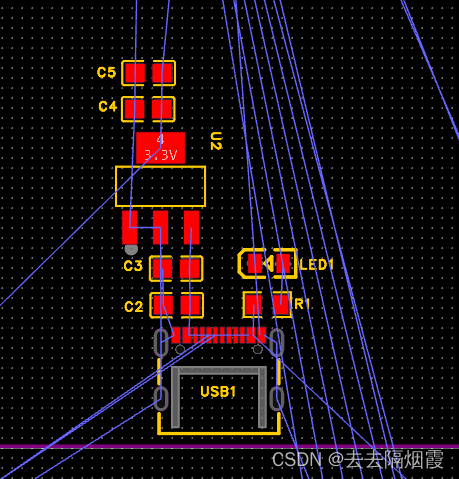

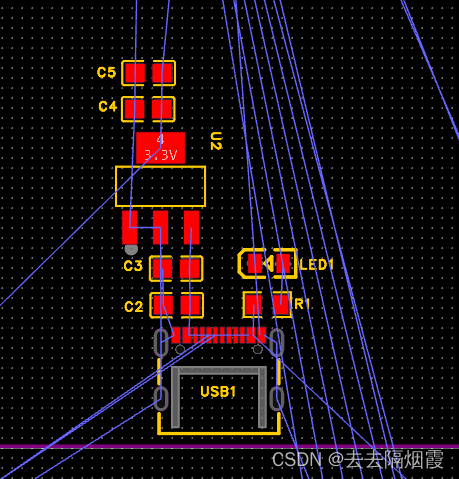

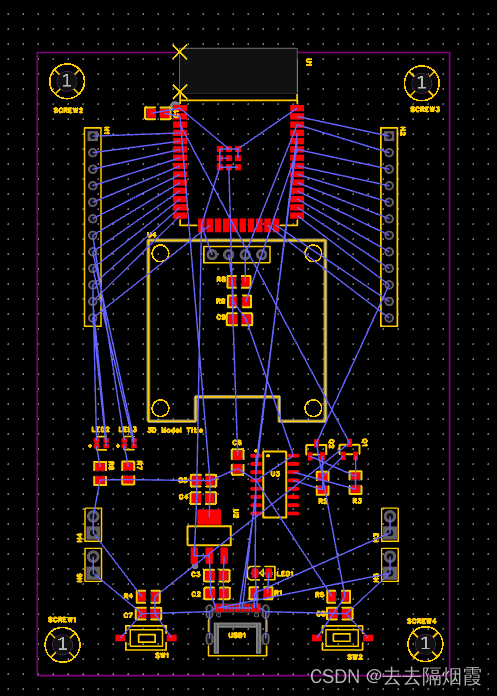

PCB画好之后裁剪板框

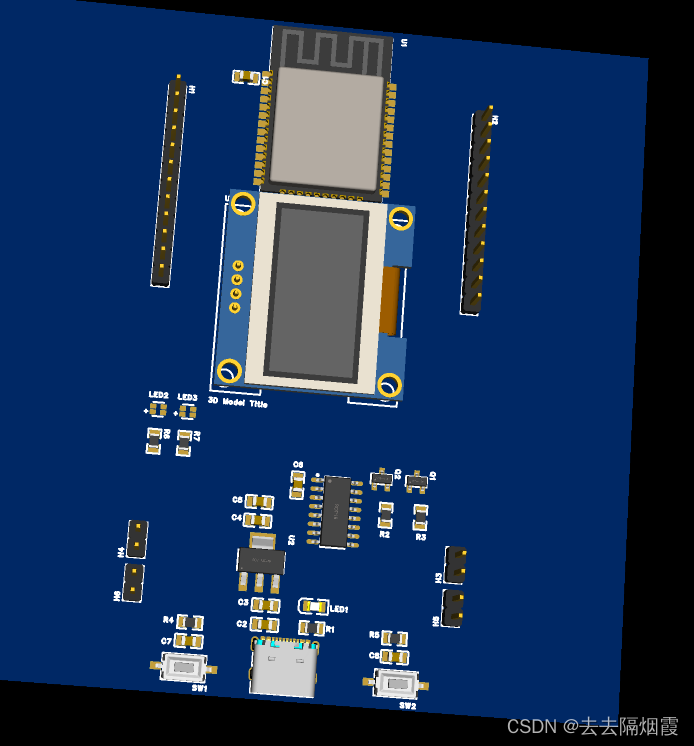

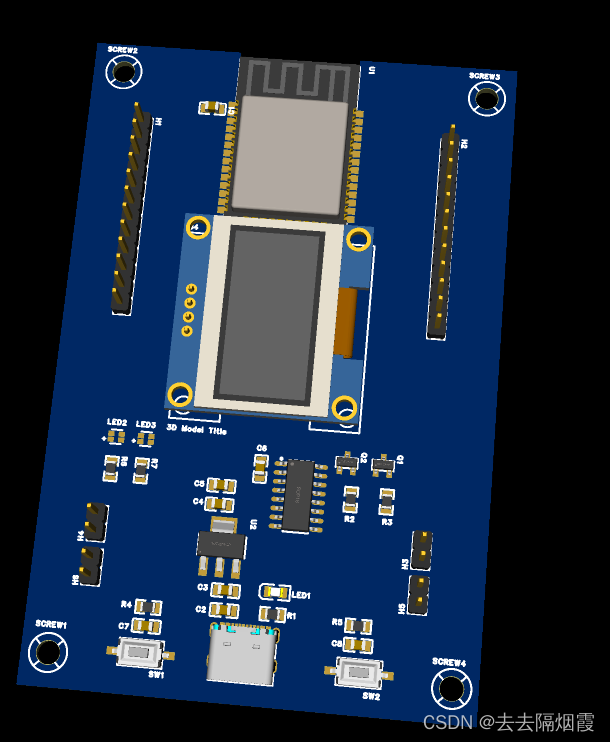

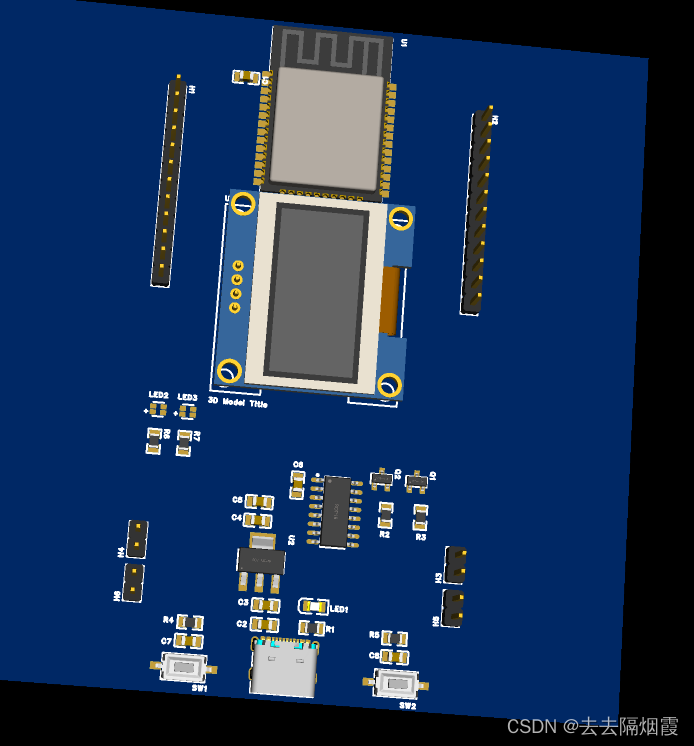

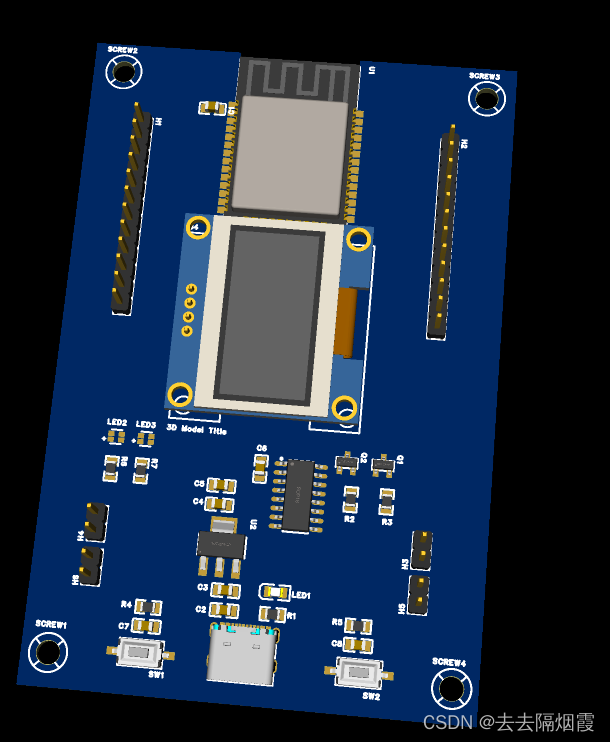

最终结果图

1 将已经画好的原理图更新到PCB中(点击应用修改)

2 一开始PCB是杂乱的,需要回到原理图,框选各个模块,然后按住Ctrl+Shift+X会自动在PCB显示这个部分,然后把各个部分分开

3 PCB画板需要有板框(嘉立创每个月都i有100X100mm免费打板)

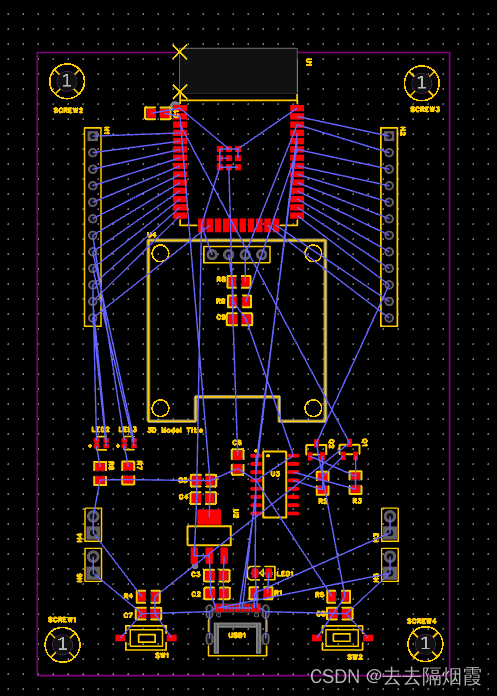

4进行布局

一般情况下优先考虑主控芯片,大器件以及供电接口

移动芯片更改栅格位置

滤波电容一般都是靠近主控芯片摆放

typ-c建议放置在下面

画PCB也要按照原理图来画(元器件摆放位置)

PCB画好之后裁剪板框

最终结果图

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?