1. 实验介绍

本次课程设计旨在培养学生的软硬件系统能力,通过基于开源的 RISCV 核 piRV32,搭建一个完整的片上系统(SOC)。学生需要进行硬件设计、软件编程,并验证系统的正确性。在本实验报告中,将详细介绍实验的设计流程、实验环境以及实验原理。

2. 实验流程

本次课程设计分为三个实验阶段:

实验一:设计最小IP核

在这个实验阶段,学生需要设计一个最小的IP核,该IP核将作为SOC系统的基础组件。学生需要学习使用Xilinx Vivado工具,进行IP核设计和生成。

实验二:搭建SoC小系统

在这个实验阶段,学生将使用实验一中设计的最小IP核,搭建一个小型的SoC系统。学生需要将各个组件连接起来,并进行配置和编程。

实验三:验证搭建的系统

在这个实验阶段,学生需要将实验二中搭建的小型SoC系统生成比特流,并上传到云平台进行验证。并需要编写相应的验证算法,以验证系统是否能正常运行并得到正确的结果。PYNQ云平台将用于验证和测试。

2.2考查点:

a) 学习Xilinx yivado工具的使用

b) 会基于CPU核搭建完整的SoC系统

c)能运用RISCV工具链

d)能基于所设计的硬件编写相应程序。

三:开发环境

本次课程设计的开发环境如下:

Vivado 2018.3:用于IP核设计和生成SOC系统。

PYNQ云平台:用于上传比特流并进行验证测试。

四实验原理

4.1RISCV指令集体系结构

RISCV(英文发音为"riskfive")架构主要由美国加州伯克利分校(简称伯克利)的Krste Asanovic教授和Yunsup Lee等开发人员于2010年发明。经过几年的发展,伯克利为RISCV架构开发了完整的软件工具链以及若干开源的处理器实例(例如Pocket Core和BOOM Core),并且得到了计算机体系结构领域的泰斗David Patterson的大力支持。

与大多数指令集架构相反,RISCV指令集架构最大的特点就是开放,无论学术机构还是商业组织都可以免费地用于所有需要的设备中,允许任何人设计、制造和销售RISCV芯片和软件。

RISCV指令分类:

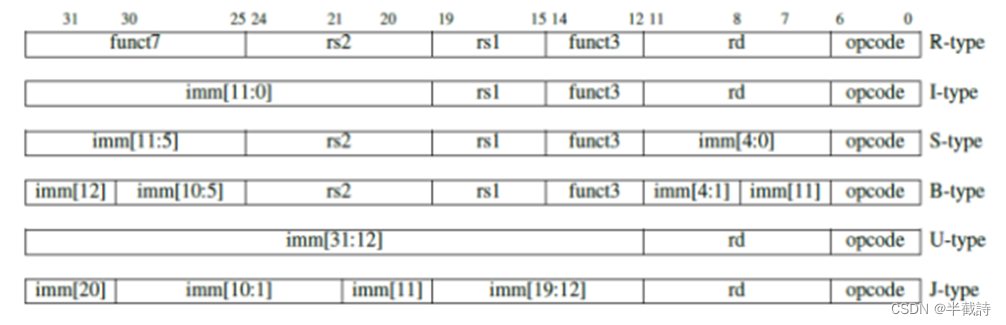

根据RISCV指令集之间的共性,其主要可分为以下6种指令格式(R、I、S、B、U、J)。

R型指令——用于寄存器与寄存器之间算术运算操作;

I 型指令——用于寄存器与立即数之间算术运算和读存储器操作;

S型指令——用于写存储器;

B型指令——用于分支转移操作(属于S型指令的变体,之前也叫SB型指令);

U型指令——用于高20比特位立即数操作;

J型指令——用于直接跳转(属于U型指令的变体,之前也叫UJ型指令)

下图是6种指令结构的格式:

4.2picoRV32处理器架构原理

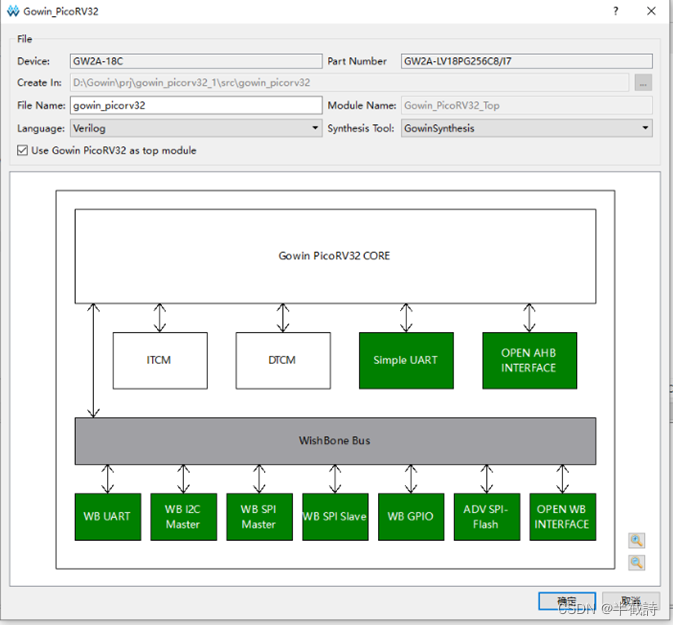

picoRV32 是一个基于 RISCV 指令集架构的开源、小型、可裁剪的 32 位处理器核。它是为了在嵌入式系统和低功耗应用中使用而设计的。目前基于RISCV架构的开源处理器有很多,既有标量处理器Rocket,也有超标量处理器BOOM,还有面向嵌入式领域的Zscale、PicoRV32等。本次实验用到的PicoRV32处理器是实现RISCV RV32IMC 指令集的 CPU 内核。它可以配置为 RV32E、RV32I、RV32IC、RV32IM 或 RV32IMC 内核,并可选择包含内置中断控制器。

(PicoRV32模块图)

他的特点是:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4019

4019

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?