调试原理

原理简析

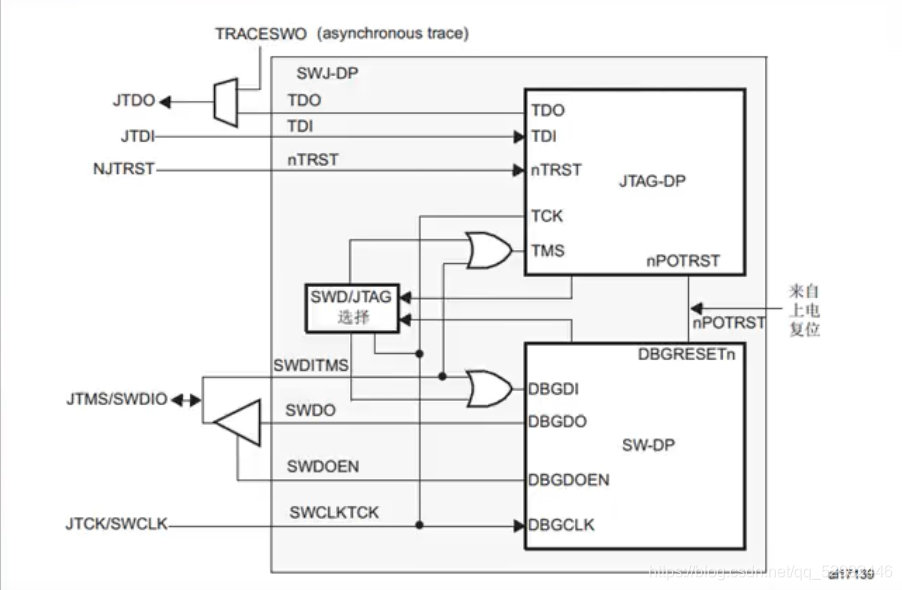

STM32F4xx的内核是Cortex(TM)-M4F,该内核包含用于高级调试功能的硬件。利用这些调试功能,可以在取指(指令端点)或访问数据(数据端点)时停止内核。内核停止时,可以查询内核的内部状态和系统的外部状态。查询完成后,恢复内核和系统并恢复程序执行。

调试接口

1、串行接口(SWD)

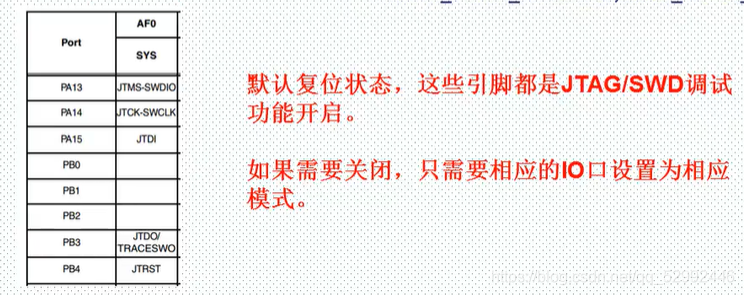

提供连接AHP-AP端口的5引脚标准JTAG接口,图右侧五个引脚

代码中为:PA13 PA14 PA15 PB3 PB4

2、JTAG调试接口

提供用于连接AHP-AP端口的2引脚(时钟+数据)接口,图中的SWDIO和SWCLK两个引脚,代码中即PA13 PA14

调试工具

JLINK

usb口连接电脑,排线连接开发板。

调试方法

设置方法(了解)

void GPIO_PinAFConfig(GPIO_TypeDef*GPIOx,uint16_tGPIO_PinSource,unit8_t,gpio_AF);

系统复位默认为AF0;各端口默认连接JLINK相应的引脚。

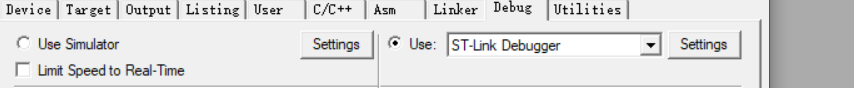

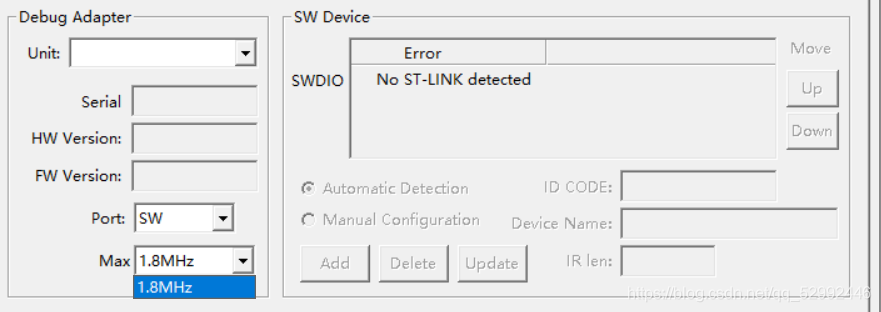

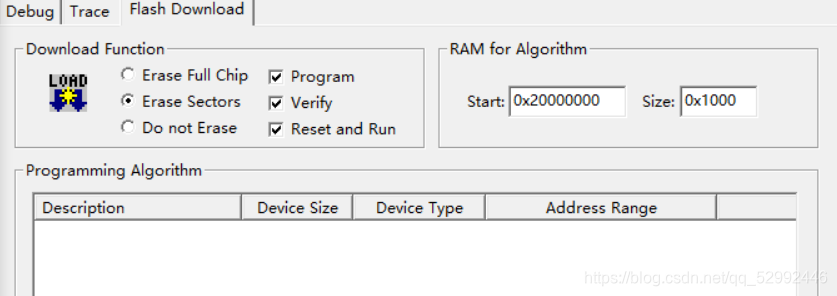

配置JLINK(回顾)

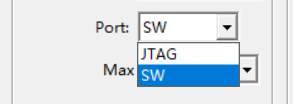

选择两种调试方法:

选择速度:

选择芯片,即可用JLINK下载调试程序

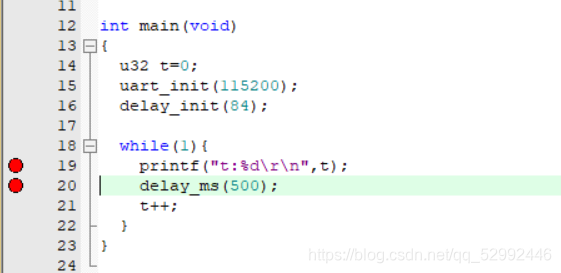

debug

点击按钮

三个按钮分别是:执行函数内部、按行执行代码、跳出函数、代码执行到光标处。

设置断点,即可调试。

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?