作业2

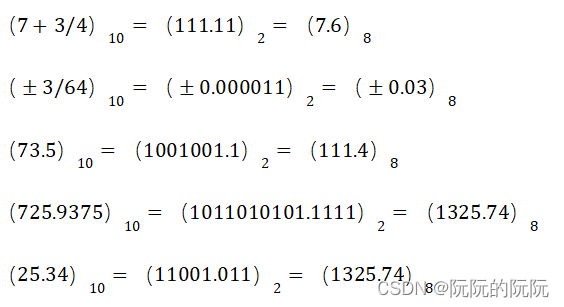

3.1 把下列十进制数化成二进制和八进制数(无法准确表示时,二进制取3位小数,八进制取1位小数):7+3/4,±3/64,73.5,725.9375,25.34

答:

3.2 把下列各数化为十进制数:

答:

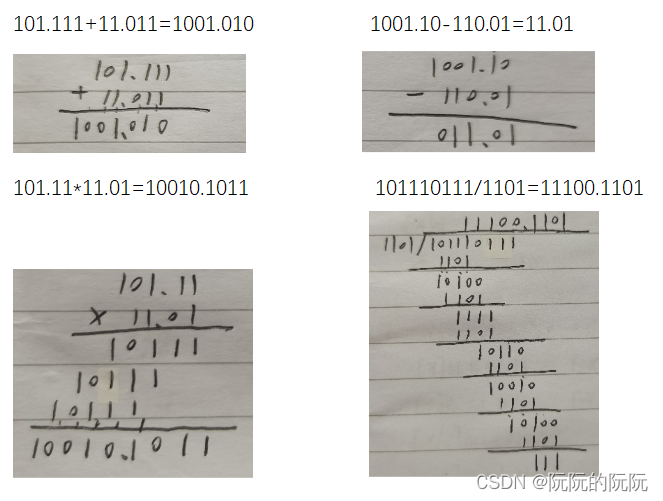

3.3 完成下列二进制运算:101.111+11.011,1001.10-110.01,101.11*11.01,101110111/1101

答:

3.4 写出下列各二进制数的原码、补码和反码:0.1010 , 0 ,-0 ,-0.1010 ,0.1111 ,-0.0100

答:

| X | [X]原 | [X]补 | [X]反 |

| 0.1010 | 0.1010 | 0.1010 | 0.1010 |

| 0 | 0.0000 | 0.0000 | 0.0000 |

| -0 | 1.0000 | 0.0000 | 1.1111 |

| -0.1010 | 1.1010 | 1.0110 | 1.0101 |

| 0.1111 | 0.1111 | 0.1111 | 0.1111 |

| -0.0100 | 1.0100 | 1.1100 | 1.1011 |

3.5 已知[X]原为下述各值,求[X]补:0.10100,1.10111,1.10110

答:

| [X]原 | 0.1110 | 1.10111 | 1.10110 |

| [X]补 | 0.1110 | 1.01001 | 1.01010 |

3.6 已知[X]补为下述各值,求X(真值):0.1110 , 1.1100,0.0001 , 1.1111,1.0001

答:

| [X]补 | 0.1110 | 1.1100 | 0.0001 | 1.1111 | 1.0001 |

| X | 0.1110 | -0.0100 | 0.0001 | -0.0001 | -0.1111 |

3.7 已知X=0.1011,Y=-0.0101,试求:[X]补,[-X]补,[Y]补,[-Y]补,[X/2]补,[X/4]补,[2X]补,[Y/2]补,[Y/4]补,[2Y]补,[-2Y]补

答:

[X]补=0.1011 , [-X]补=1.0101 ,[Y]补=1.1011 ,[-Y]补=0.0101 ,

[X/2]补=0.0101(1) , [X/4]补=0.0010(11) , [2X]补溢出 ,

[Y/2]补=1.1101(1) , [Y/4]补=1.1110(11) , [2Y]补=1.0110 ,[-2Y]补=0.1010

3.8 设十进制数X=(128.75)*2-10

(1)若(Y)2=(X)10,用定点数表示Y值。

![]()

Y=0.001000000011

(2)设用21个二进制位表示浮点数,阶码用5位,其中阶符用1位;尾数用16位,其中符号用1位。阶数的基数为2.写出阶码和尾数均用原码表示的Y的机器数。

| 尾数符号位 | 阶码 | 尾数(除符号位) | |

| 原码 | 0 | 10010 | 100000001100000 |

(3)写出阶码和尾数均用反码表示的Y的机器数。

| 尾数符号位 | 阶码 | 尾数(除符号位) | |

| 反码 | 0 | 11101 | 100000001100000 |

(4)写出阶码和尾数均用补码表示的Y的机器数。

| 尾数符号位 | 阶码 | 尾数(除符号位) | |

| 补码 | 0 | 11110 | 100000001100000 |

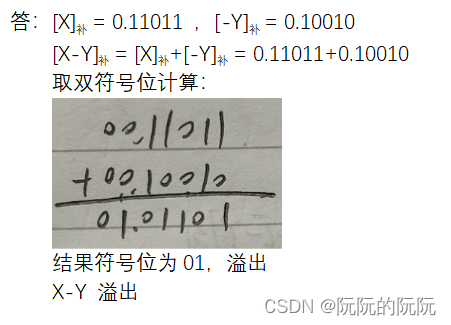

3.15 用补码运算计算下列各组数的差 (X-Y)

(1)X=-0.10110 Y=0.11111

(2)X=0.11011 Y=-0.10010

3.18 用补码一位乘计算X=0.1010和Y=-0.0110的积X*Y

答:[X]补 = 00.1010 ,[Y]补 = 1.1010 ,[-X]补 = 11.0110

[X*Y]补 = 11.11000100

X*Y = -0.00111100

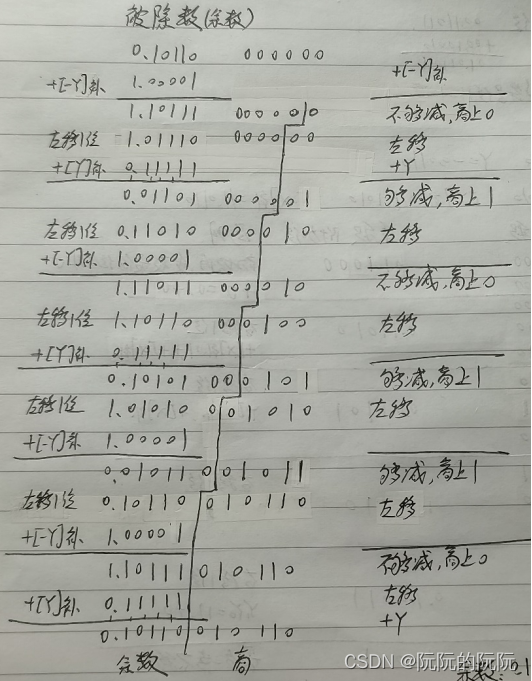

3.19 X=-0.10110,Y=0.11111,用加减交替法原码一位除计算X/Y的商及余数

答:[X]原 = 1.10110 ,[Y]原 = 0.11111 , [Y]补 = 0.11111 ,[-Y]补 = 1.00001

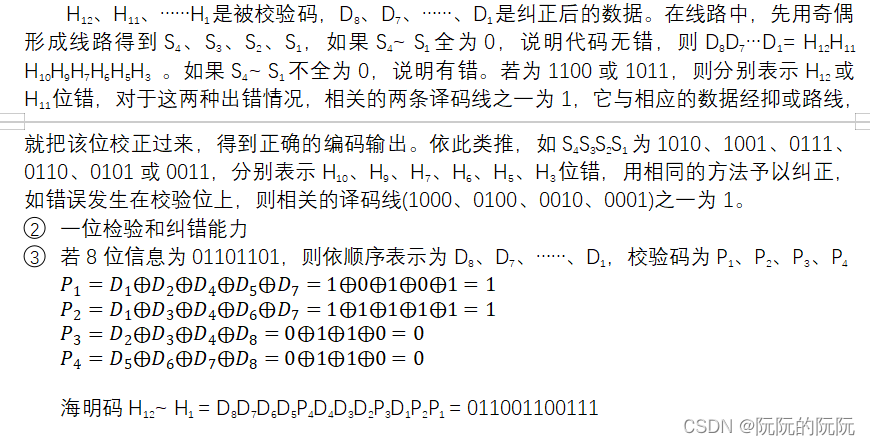

3.27 设有8位有效信息,试为之编制海明校验线路。说明编码方法,并分析所选方案具有怎样的检错与纠错能力。若8位信息为01101101,海明码是何值?

答:

编码方法:(12, 8) 分组码海明校验线路如下图所示:

4.1 在计算机的主存中,常常设置一定的ROM区。试说明设置ROM区域的目的。

答:计算机加电时,需要执行一段程序和设置一些初始数据,如果这些程序和数据放在RAM区,那么断电后会丢失,所以把它放在ROM区,永久的保存下来。至于ROM区的大小则由操作系统决定,可以将操作系统中很小一段程序保存在ROM中,加电启动计算机后依靠这段程序将操作系统由磁盘调入主存。

4.2为什么DRAM芯片的地址一般要分两次接受?

答:

① 减少芯片的地址引出端,使之减少一半,从而减小器件的尺寸。

② 分行列两次输入,可以减小地址译码器的规模。

③ 基于数据访问的局部性,DRAM在页面工作方式下,不改变行地址,只需改变列地

址即可连续访问存储器,地址加载速度快,芯片减少功耗;

④ 可以按行刷新,减小刷新周期。

4.6 某机器中,已知有一个地址空间为0000H~1FFFH的ROM区域

4.7 SRAM和DRAM的主要差别是什么?

答:SRAM,静态随机存储器,一般用于CPU中的高速缓冲存储器,不需要刷新电路即能保存它内部存储的数据。DRAM,动态随机存储器,一般用于内存,需要不断地刷新电路,否则数据就消失了。因此SRAM具有较高的性能,但是SRAM也有它的缺点,即它的集成度较低,功耗比DRAM大,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积。同样面积的硅片可以做出更大容量的DRAM,因此SRAM显得更贵。

2407

2407

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?