提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

希望能在暑假期间多做一些Verilog的题目,弥补实战的不足。

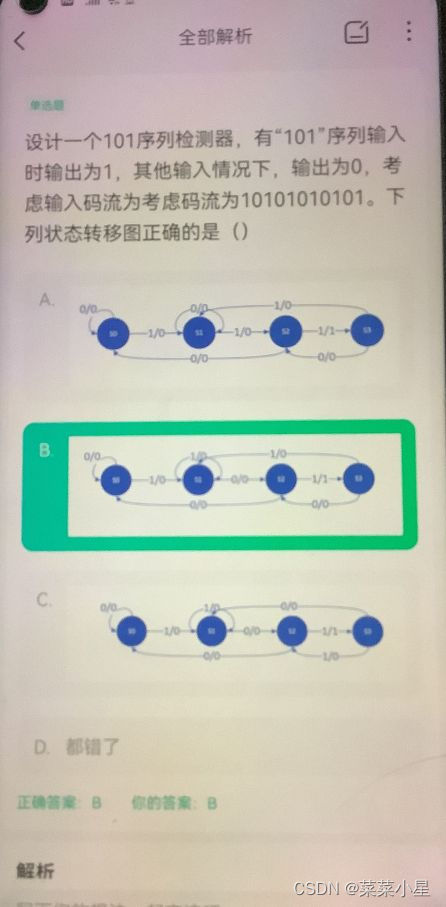

一、

状态转换条件X/Y中,X是当前输入,Y表示输出。

(暂时有疑问,有了解的大佬可以评论解答一下,帮帮孩子)

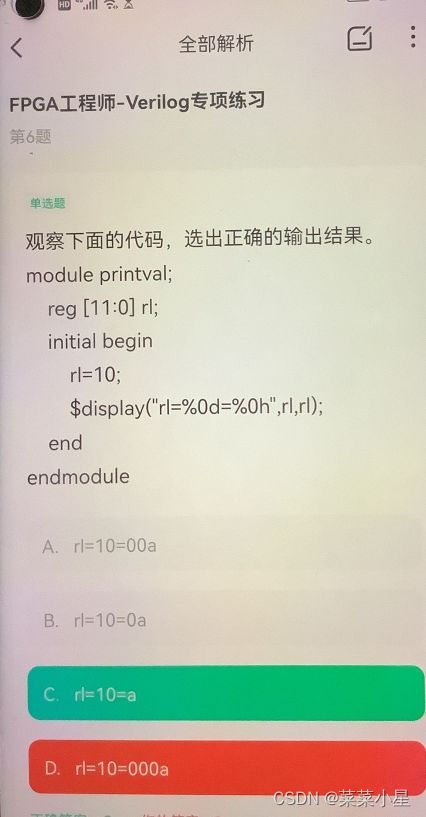

二、

十进制【d】,十六进制【h】,二进制【b】,八进制【o】。

%0是用最短的位数表示,所以只写一个”a“即可。

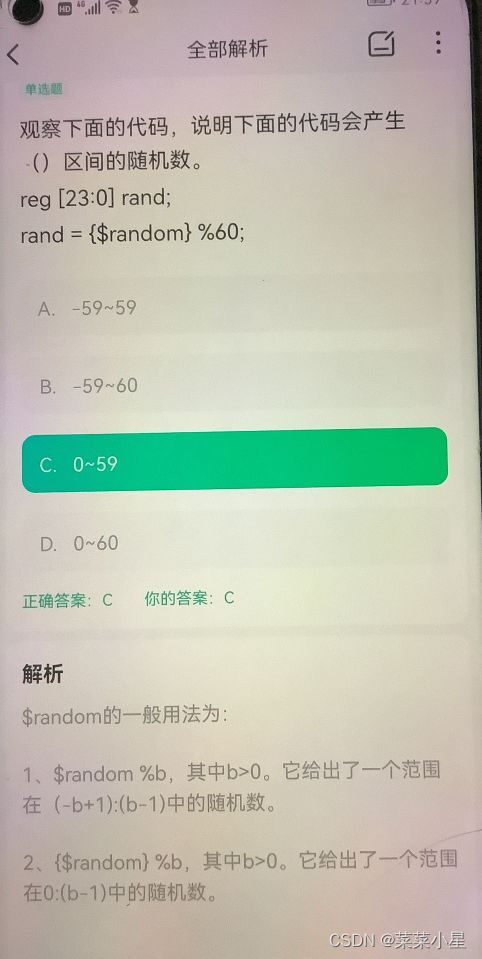

三、

$random%b,其中b>0,范围是(-(b-1)):(b-1)

{$random}%b,其中b>0,范围是0:(b-1)

四、

锁存器对电平敏感,触发器对边沿敏感。

一个锁存器或者一个触发器只能储存一个二进制码,都具有1、0两种状态,一旦状态确定,就可以继续保存。两者都是逻辑电路的基本单元。

五、

任务内不能出现过程块语句【always和initial】。

六、

always块里不能同时出现上升沿和下降沿敏感信号,不然区分混乱。

七、

$time用来查看当前仿真时刻,返回一个64bit的整数来表示当前仿真时刻。

$realtime和$time作用一样,但返回的时刻值是一个实型数。

$readmemb从文件中读取数据到存储器中。

八、

904

904

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?