(1)采用全软件仿真方法,设计一个周期可变、信号类型可选的信号发生器。

(2)初始状态为正弦波,周期为64个时钟周期。

(3)信号类型正弦波(0)、方波(1)可选;周期64(00)、96(01)、128(10)、160(11)个时钟周期可选。

(4)八种波形,根据信号类型、信号周期选择,通过八选一开关,输出所要求的波形。

(5)使用Matlab生成波形数据(.mif格式)。

(6)信号持续。

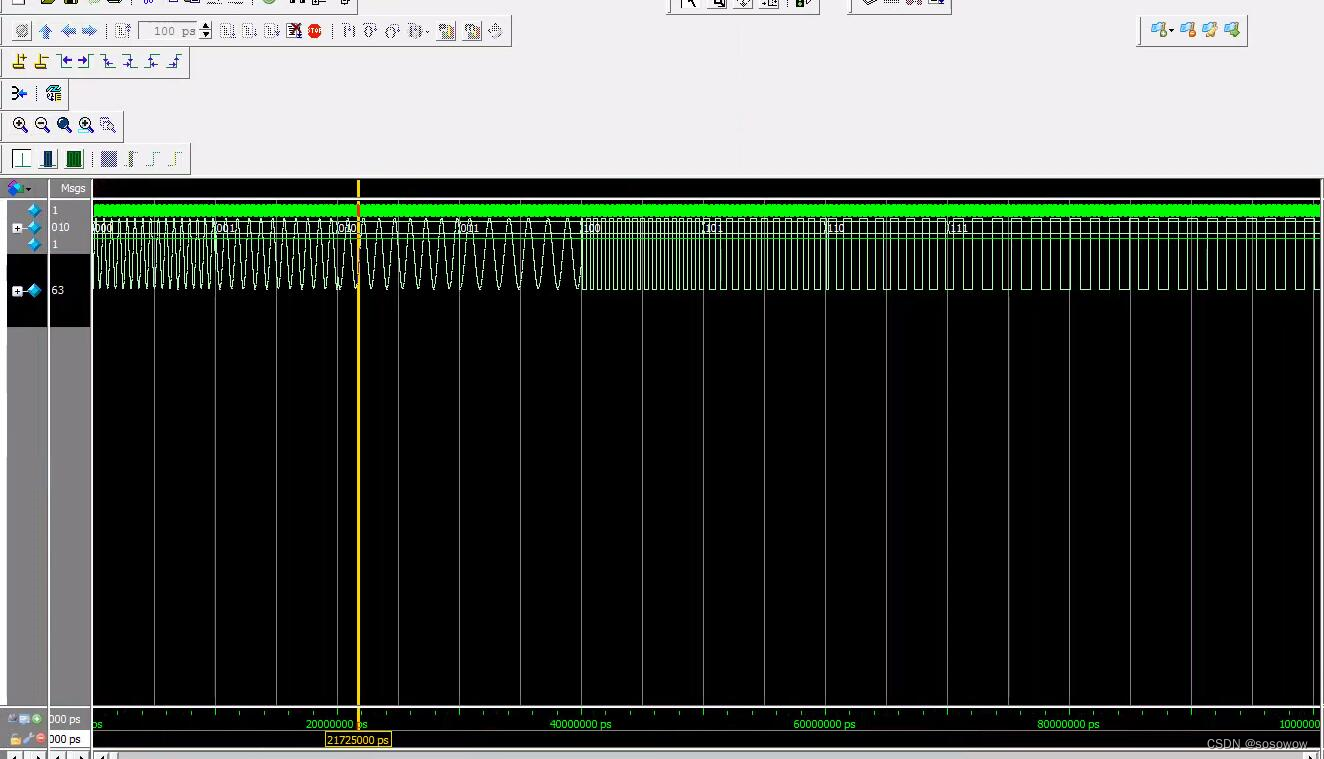

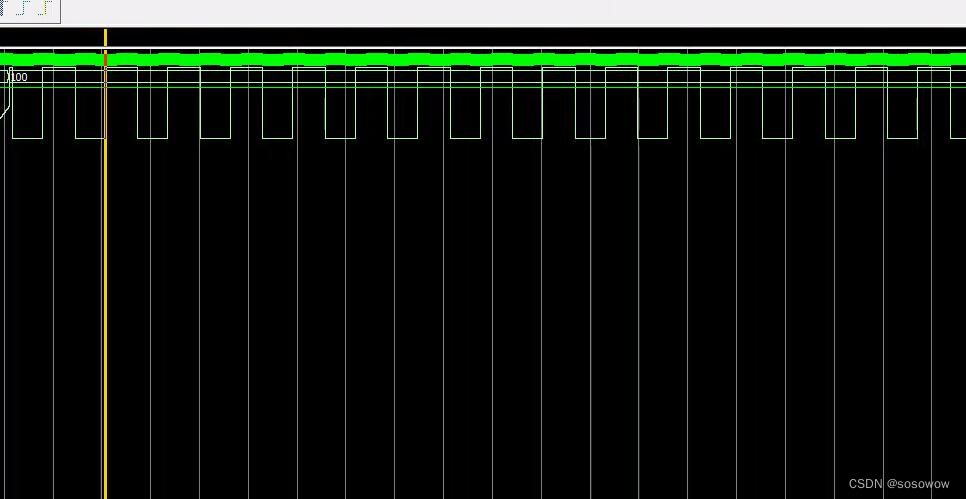

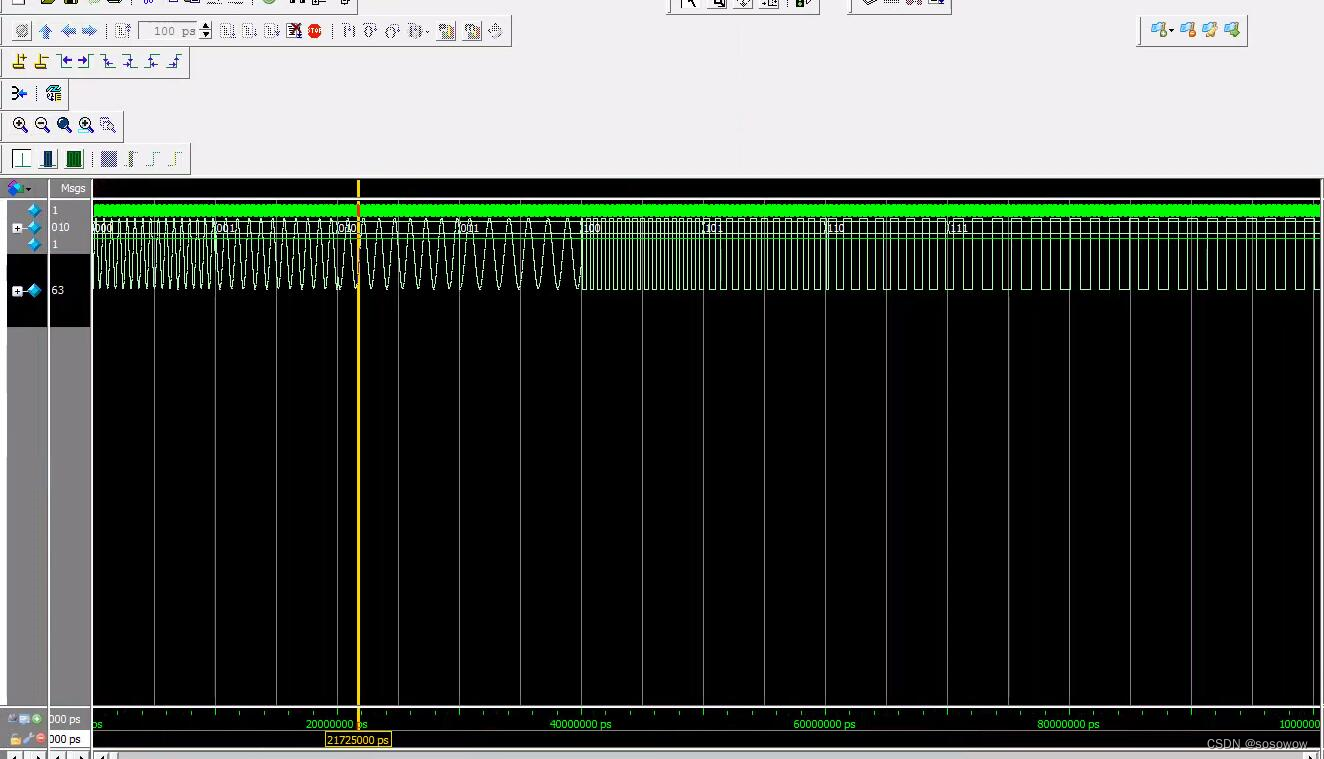

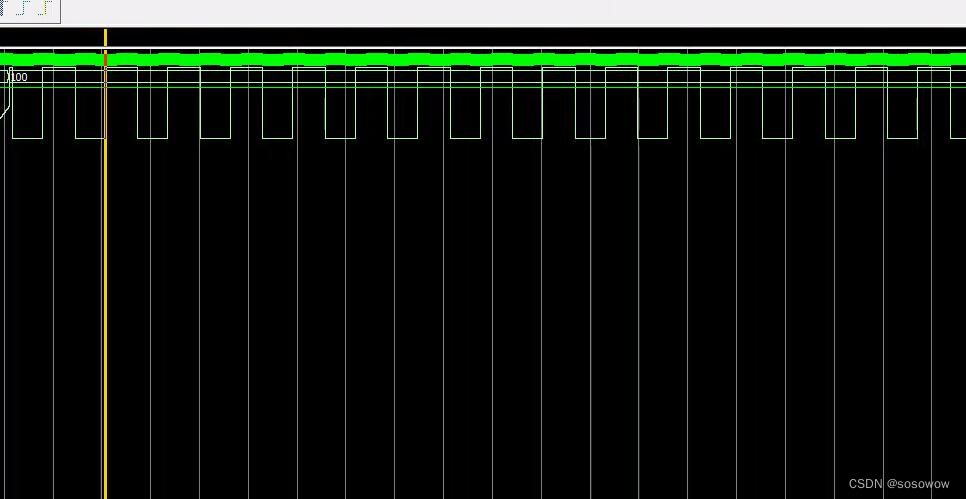

(7)采用波形仿真、Testbench仿 真两种方式进行功能仿真和时序仿真。

真两种方式进行功能仿真和时序仿真。

(1)采用全软件仿真方法,设计一个周期可变、信号类型可选的信号发生器。

(2)初始状态为正弦波,周期为64个时钟周期。

(3)信号类型正弦波(0)、方波(1)可选;周期64(00)、96(01)、128(10)、160(11)个时钟周期可选。

(4)八种波形,根据信号类型、信号周期选择,通过八选一开关,输出所要求的波形。

(5)使用Matlab生成波形数据(.mif格式)。

(6)信号持续。

(7)采用波形仿真、Testbench仿 真两种方式进行功能仿真和时序仿真。

真两种方式进行功能仿真和时序仿真。

2556

2556

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?