百度网盘:实验2-ALU 实验2-指令译码器

提取码:0928

实验二 模型机组合部件的实现(一)

班级 姓名 学号

一、实验目的

- 了解简易模型机的内部结构和工作原理。

- 熟悉译码器、运算器的工作原理。

- 分析模型机的功能,设计指令译码器。

- 分析模型机的功能,设计 ALU。

二、实验内容

- 用 VERILOG 语言设计指令译码器;

- 用 VERILOG 语言设计 ALU。

三、实验过程

1、指令译码器

A)创建工程

(选择的芯片为family=Cyclone II;name=EP2C5T144C8)

B) 编写源代码

module ins_decode(en,ir,mova,movb,movc,add,sub,and1,not1,rsr,rsl,jmp,jz,jc,in1,out1,nop,halt);

input en;

input [7:0] ir;

output mova,movb,movc,add,sub,and1,not1,rsr,rsl,jmp,jz,jc,in1,out1,nop,halt;

reg mova,movb,movc,add,sub,and1,not1,rsr,rsl,jmp,jz,jc,in1,out1,nop,halt;

always@(en or ir)

begin

//chu shi hua

mova=0; movb=0; movc=0; add=0; sub=0; and1=0; not1=0; rsr=0; rsl=0; jmp=0; jz=0; jc=0; in1=0;

out1=0; nop=0; halt=0;

//1100 11xx movb

if(en==1'b1 & ir[7]==1'b1 & ir[6]==1'b1 & ir[5]==1'b0 & ir[4]==1'b0 & ir[3]==1'b1 & ir[2]==1'b1)

begin movb=1; end

//1100 xx11 movc

else if(en==1'b1 & ir[7]==1'b1 & ir[6]==1'b1 & ir[5]==1'b0 & ir[4]==1'b0 & ir[1]==1'b1 & ir[0]==1'd1)

begin movc=1; end

//1100 mova

else if(en==1'b1 & ir[7]==1'b1 & ir[6]==1'b1 & ir[5]==1'b0 & ir[4]==1'b0)

begin mova=1; end

//1001 xxxx add

else if(en==1'b1 & ir[7]==1'b1 & ir[6]==1'b0 & ir[5]==1'b0 & ir[4]==1'b1)

begin add=1; end

//0110 xxxx sub

else if(en==1'b1 & ir[7]==1'b0 & ir[6]==1'b1 & ir[5]==1'b1 & ir[4]==1'b0)

begin sub=1; end

//1011 xxxx and

else if(en==1'b1 & ir[7]==1'b1 & ir[6]==1'b0 & ir[5]==1'b1 & ir[4]==1'b1)

begin and1=1; end

//0101 xxxx not

else if(en==1'b1 & ir[7]==1'b0 & ir[6]==1'b1 & ir[5]==1'b0 & ir[4]==1'b1)

begin not1=1; end

//1010 xx00 RSR

else if(en==1'b1 & ir[7]==1'b1 & ir[6]==1'b0 & ir[5]==1'b1 & ir[4]==1'b0 & ir[1]==1'b0 & ir[0]==1'd0)

begin rsr=1; end

//1010 xx11 RSL

else if(en==1'b1 & ir[7]==1'b1 & ir[6]==1'b0 & ir[5]==1'b1 & ir[4]==1'b0 & ir[1]==1'b1 & ir[0]==1'd1)

begin rsl=1; end

//0011 0000 address JMP add

else if(en==1'b1 & ir[7]==1'b0 & ir[6]==1'b0 & ir[5]==1'b1 & ir[4]==1'b1 & ir[3]==1'b0 & ir[2]==1'b0 & ir[1]==1'b0 & ir[0]==1'd0)

begin jmp=1; end

//0011 0001 address JZ add

else if(en==1'b1 & ir[7]==1'b0 & ir[6]==1'b0 & ir[5]==1'b1 & ir[4]==1'b1 & ir[3]==1'b0 & ir[2]==1'b0 & ir[1]==1'b0 & ir[0]==1'd1)

begin jz=1; end

//0011 0010 address JC add

else if(en==1'b1 & ir[7]==1'b0 & ir[6]==1'b0 & ir[5]==1'b1 & ir[4]==1'b1 & ir[3]==1'b0 & ir[2]==1'b0 & ir[1]==1'b1 & ir[0]==1'd0)

begin jc=1; end

//0010 xxxx in

else if(en==1'b1 & ir[7]==1'b0 & ir[6]==1'b0 & ir[5]==1'b1 & ir[4]==1'b0)

begin in1=1; end

//0100 xxxx out

else if(en==1'b1 & ir[7]==1'b0 & ir[6]==1'b1 & ir[5]==1'b0 & ir[4]==1'b0)

begin out1=1; end

//0111 0000 nop

else if(en==1'b1 & ir[7]==1'b0 & ir[6]==1'b1 & ir[5]==1'b1 & ir[4]==1'b1 & ir[3]==1'b0 & ir[2]==1'b0 & ir[1]==1'b0 & ir[0]==1'd0)

begin nop=1; end

//1000 0000 halt

else halt=1;

end

endmodule

/*module ins_decode(EN,ir,MOVA,MOVB,MOVC,ADD,SUB,AND1,NOT1,RSR,RSL,JMP,JZ,JC, IN1,OUT1,NOP,HALT);

input [7:0] ir;

input EN;

output MOVA,MOVB,MOVC,ADD,SUB,AND1,NOT1,RSR,RSL,JMP,JZ,JC,IN1,OUT1,NOP,HALT;

reg MOVA,MOVB,MOVC,ADD,SUB,AND1,NOT1,RSR,RSL,JMP,JZ,JC,IN1,OUT1,NOP,HALT;

always@(ir,EN)

begin

MOVA=0;MOVB=0;MOVC=0;ADD=0;SUB=0;AND1=0;NOT1=0;RSR=0;RSL=0;JMP=0;JZ=0;JC=0;IN1=0; OUT1=0;NOP=0;HALT=0;

if (EN)

begin

if(ir[7:4]==4'b1100)

begin

if(ir[3]&ir[2]) MOVB=1;

else if(ir[1]&ir[0]) MOVC=1;

else MOVA=1'b1;

end

else if(ir[7:4]==4'b1001) ADD=1;

else if(ir[7:4]==4'b0110) SUB=1;

else if(ir[7:4]==4'b1011) AND1=1;

else if(ir[7:4]==4'b0101) NOT1=1;

else if(ir[7:4]==4'b1010)

begin

if(~ir[1]&~ir[0]) RSR=1;

else RSL=1;

end

else if(ir[7:4]==4'b0011)

begin

JC=ir[1];

JZ=ir[0];

JMP=!ir[1]&&!ir[0];

end

else if(ir[7:4]==4'b0010)IN1=1;

else if(ir[7:4]==4'b0100)OUT1=1;

else if(ir[7:4]==4'b0111)NOP=1;

else if(ir[7:4]==4'b1000) HALT=1;

else ;

end

else ;

end

endmodule

*/C)编译与调试

(包含编译调试过程中的错误、警告信息以及资源消耗)

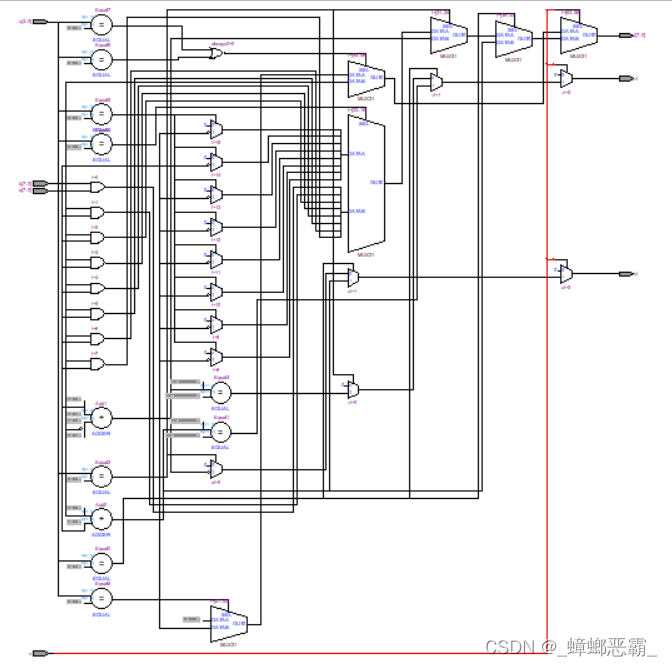

D)RTL视图

D)RTL视图

E)功能仿真波形

a)指令译码器

结果分析及结论:

因为8位进制数的输入有256个,不便于判断,于是前面几个自己手动输入想要的输入并观测功能仿真的结果。

通过设置需要的输入,功能仿真后的结果与预想的结果一样,满足组合逻辑电路的真值表。

所以本程序通过了功能仿真。

F)时序仿真波形

结果分析及结论:

在Assignment的Setting中将仿真选项改为Timing,得到上面的结果。与功能仿真相比,时序仿真不符合满足组合逻辑电路的真值表。因而也证明了Timing时序仿真体现了门电路的延迟效果。

输出和功能仿真相比,集体都有一定的延时,除此之外,在一些本该低电平的地方突然出现了高电平,本该高电平的地方突然出现了低电平,这是时序仿真的过程中出现了冒险现象。

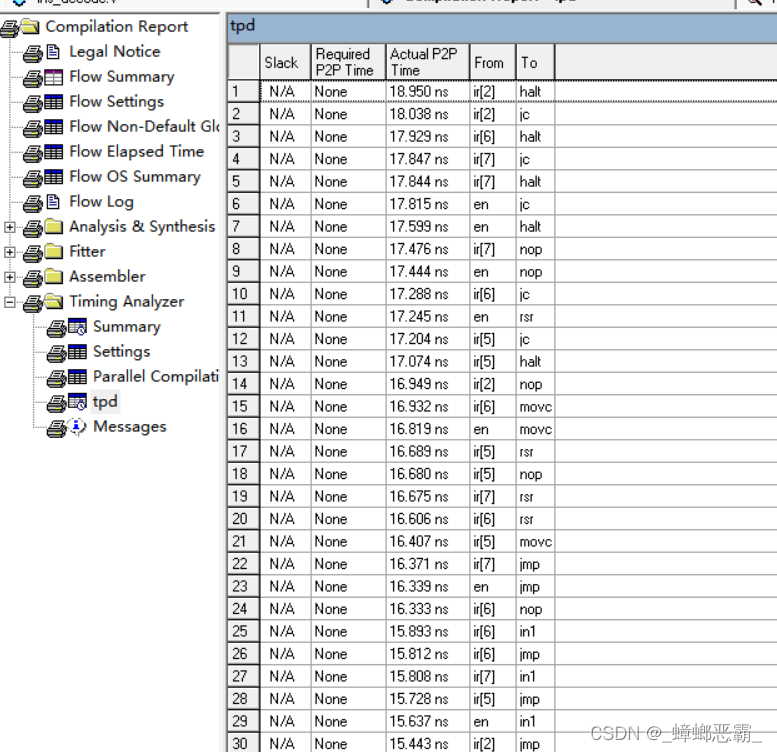

G)时序分析

结果分析及结论:

延迟从7.277-18.950ns,大多为13ns。

结果由耗时最长的那个决定,故整体耗时为18.95ns;

没有failed path。

2.算术逻辑单元ALU

A)创建工程

(选择的芯片为family=FLEX10K;name=EPF10K20TI144-4)

B)编写源代码

C) 编译与调试

(包含编译调试过程中的错误、警告信息以及资源消耗)

D) RTL视图

结果分析及结论:

电路图中除了基本的逻辑门外,还包含了多路复用器、加法器、加法器等,来执行选择、加法、减法、赋值等操作。

视图较为复杂,通过视图来判断逻辑是否正确难度较大,所以逻辑的正确性将通过后续的波形图来验证。

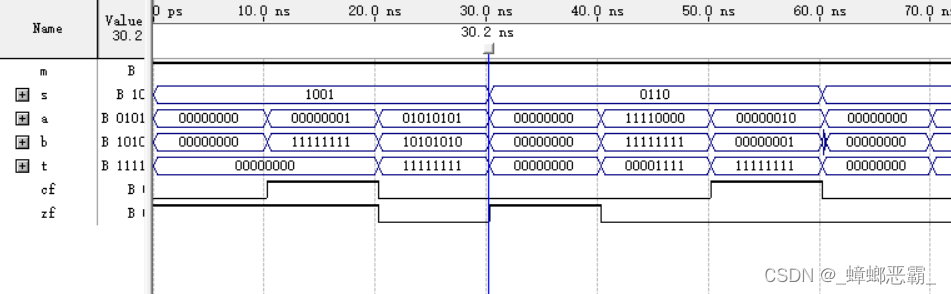

E) 功能仿真波形

结果分析及结论:

因为8位进制数的输入有256个,不便于判断,于是前面几个自己手动输入想要的输入并观测功能仿真的结果。

通过设置需要的输入,功能仿真后的结果与预想的结果一样,满足组合逻辑电路的真值表。

所以本程序通过了功能仿真。

F) 时序仿真波形

结果分析及结论:

在Assignment的Setting中将仿真选项改为Timing,得到上面的结果。与功能仿真相比,时序仿真不符合满足组合逻辑电路的真值表。因而也证明了Timing时序仿真体现了门电路的延迟效果。

输出和功能仿真相比,集体都有一定的延时,除此之外,在一些本该低电平的地方突然出现了高电平,本该高电平的地方突然出现了低电平,这是时序仿真的过程中出现了冒险现象

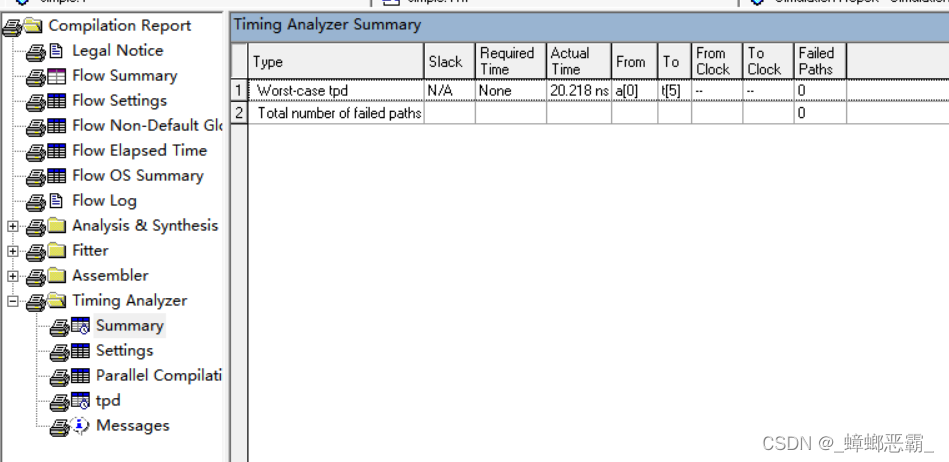

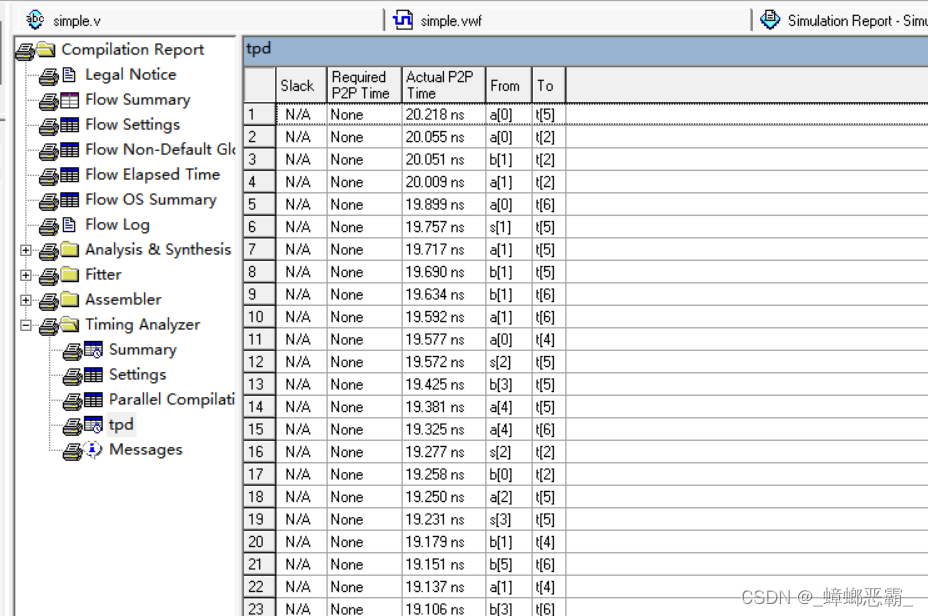

G) 时序分析

结果分析及结论:

延迟从12.421-20.218ns,大多为18ns。

结果由耗时最长的那个决定,故整体耗时为为20.218ns;

没有failed path。

四、思考题

1.指令译码器必须要16个输出吗?可否将一些输出合并,哪些可以合并,为什么?

不是必须16个输出。

可以将MOVA、MOVB、MOVC合并,因为其指令编码的前4位数相同,只有后面4位表示寄存器的不同,但是实现都是寄存器的之间的赋值。

2.ALU中的S[3..0]控制信号是来自哪里或者说与什么信息相同?

ALU中的S[3..0]控制信号是来自8位二进制数的指令编码的前4位。

由R2、R1 在 S3~S0 和 M 的控制下,实现运算,经移位逻辑送入总线 BUS;由/WE 控制和 R1 的编码选择 RWBA1、RWBA0,将 BUS 上的数据写入通用寄存器 R1。

3、为何S[3..0]等于1100或0100时将输入a传给t,S[3..0]等于1010时将输入b传给t?

有些逻辑表达式不需要进行加减与非等运算,但是仍需通过ALU、至移位逻辑后进入总线BUS。

而ALU有2个输入端口,通用寄存器组的两个端口一个为源寄存器、一个为目的寄存器,所以ALU须有两个分别输出t=a和t=b的运算。

故S[3..0]等于1100或0100时将输入a传给t,S[3..0]等于1010时将输入b传给t

五、实验总结、必得体会及建议

1、从需要掌握的理论、遇到的困难、解决的办法以及经验教训等方面进行总结。

正像第二个工程的名字simple一样,本次实验难度不算大,代码也比较好理解。

但是代码程序的规则,尤其前面几行的input、output,reg,always等的使用还不是很熟悉。所以虽然代码很好理解,但是自己完整写出来并成功运行还是费了一些功夫。

接下来,还是尽量熟悉 Quartus II 软件的基本操作,学习Verilog语言编写程序。

心得:实践是最好的学习方法。尽管之前老师在课堂上对Verilog语言讲授了很多,但具体的设计和编写步骤经常忘记。这次实验让我快速熟悉了Verilog语言,理解也比之前单纯听老师授课深入了很多。

2、对本实验内容、过程和方法的改进建议(可选项)。

题目可以给出几个样例与正确结果,用于学生自己验证,功能仿真时的正确性。同时也可作为作业要求提交输入该样例得到的正确结果。

2033

2033

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?