百度网盘:模型机-实验五![]() https://pan.baidu.com/s/1D_uD-_YS5JsqDEtK7gUhYw?pwd=0928

https://pan.baidu.com/s/1D_uD-_YS5JsqDEtK7gUhYw?pwd=0928

提取码:0928

模型机设计报告

一、设计目的

完整、连贯地运用《电路与电子学》所学到的数电知识,熟练掌握现代 EDA 工具基本使用方法,为后续课程学习和今后从事相关工作打下良好的基础或做下一些铺垫。

二、设计内容

1、 按照给定的数据通路、数据格式和指令系统,使用 EDA 工具设计一台用硬连线逻辑控制的简易计算机;

(1)数据格式

数据字采用 8 位二进制定点补码表示,其中最高位(第 7 位)为符号位,小数点可视为最左或最右,其数值表示范围分别为:-1≤X<+1 或-128≤X<+127。

(2)寻址方式

指令的高 4 位为操作码,低 4 位分别用 2 位表示目的寄存器和源寄存器的编号,或表示寻址方式。共有 2 种寻址方式。

① 寄存器直接寻址

| 操作码 | R1 | R2 |

当R1和R2均不是“11”时,R1 和 R2 分别表示两个操作数所在寄存器的地址,其中R1为目标寄存器地址,R2为源寄存器地址。

② 寄存器间接寻址

| 操作码 | R1/11 | R2/11 |

当R1 或R2 中有一个为“11”时,表示相应操作数的地址在C寄存器中。

(3)指令系统

指令系统有 16 条。下面采用汇编符号对指令进行描述,其中 R1 和 R2 分别表示“目标”和“源”寄存器,M 表示地址在寄存器 C 中的存贮单元。

| 汇编符号 | 功能 | 编码 |

| MOV R1,R2 | (R2)→ R1 | 1100 R1 R2 |

| MOV M ,R2 | (R2)→ (C) | 1100 11 R2 |

| MOV R1,M | ((C)) → R1 | 1100 R1 11 |

| ADD R1,R2 | (R1)+(R2)→R1 | 1001 R1 R2 |

| SUB R1,R2 | (R1)-(R2)→R1 | 0110 R1 R2 |

| AND R1,R2 | (R1)&(R2)→R1 | 1011 R1 R2 |

| NOT R1 | /(R1)→R1 | 0101 R1 XX |

| RSR R1 | (R1)循环右移一位→R1 | 1010 R1 00 |

| RSL R1 | (R1)循环左移一位→R1 | 1010 R1 11 |

| JMP add | add→PC | 0011 00 00 address |

| JZ add | 结果为0时add→PC | 0011 00 01 address |

| JC add | 结果有进位时add→PC | 0011 00 10 address |

| IN R1 | (开关7-0)→R1 | 0010 R1 XX |

| OUT R2 | (R2)→发光二极管7-0 | 0100 XX R2 |

| NOP | 0111 00 00 | |

| HALT | 停机 | 1000 00 00 |

(4)数据通路

计算机的工作过程可以看作是许多不同的数据流和控制流在机器各部分之间的流动,数据流所经过的路径称作机器的数据通路。

(5)控制器设计

指令寄存器 IR 接收到一条机器指令后,这条指令就被译码执行。指令通过译码产生出的各种控制信号在时钟信号的配合下控制着指令执行的全过程。

| 序号 | 信号 | 功能 |

| 1 | IN PC | 与 LD PC 配合使用,为 1 时 PC 加 1 计数,为 0 时加载 BUS上的数据。 |

| 2 | LD PC | 当 IN PC=1 允许对 PC 加 1 计数,否则允许把 BUS 上的数据打入 PC。 |

| 3 | LD IR | 允许把 BUS 上的数据打入指令寄存器 IR。 |

| 4 | /WE | 允许把 BUS 上的数据打入通用寄存器组,低电平有效。 |

| 5 | F→BUS | ALU 的运算结果通过移位逻辑直接送到总线 BUS 的对应位。 |

| 6 | FRL→BUS | ALU 的运算结果通过移位逻辑循环左移一位送到总线 BUS,且 F7送 Cf。 |

| 7 | FRR→BUS | ALU 的运算结果通过移位逻辑循环右移一位送到总线 BUS,且 F0送 Cf。 |

| 8 | /CS | 允许访问存储器,低电平有效。 |

| 9-10 | MADD | 存储器 RAM 地址来源。0:指令计数器,1:通用寄存器 A 口,2:B 口。 |

| 11 | DL | 读存储器RAM |

| 12 | XL | 写存储器RAM |

| 13 | M | M=1,表示 ALU 进行逻辑运算操作,否则进行算术操作。 |

| 14-17 | S3-S0 | 使 ALU 执行各种运算的控制位。 |

| 18 | HALT | 此位为“1”时停机,下次输入人工操作。 |

| 19 | RAA[1..0],RWBA[1..0] | 分别选择读取寄存器 A,B,C 中的一个值在 S、D 口输出 |

| 20 | WE | WE=0 时,根据 RWBA[1..0] 从 A,B,C 选择一个寄存器写入输入的值。 |

2、 整理出设计报告。

三、详细设计

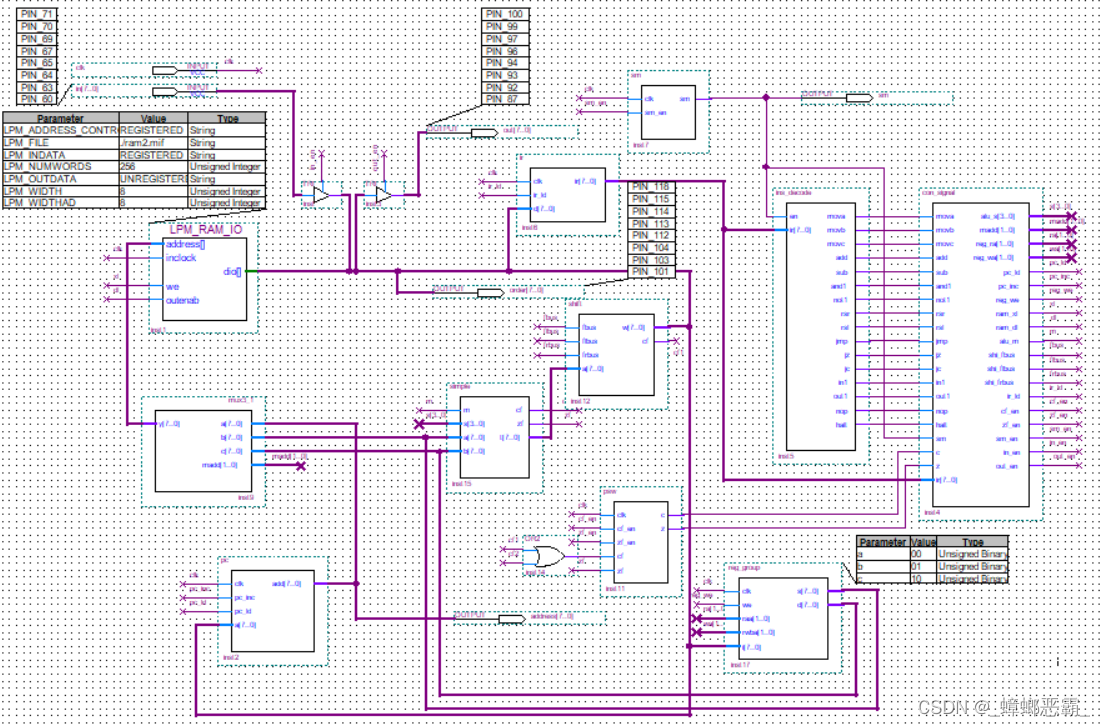

3.1 设计的整体架构

3.2 各模块的具体实现

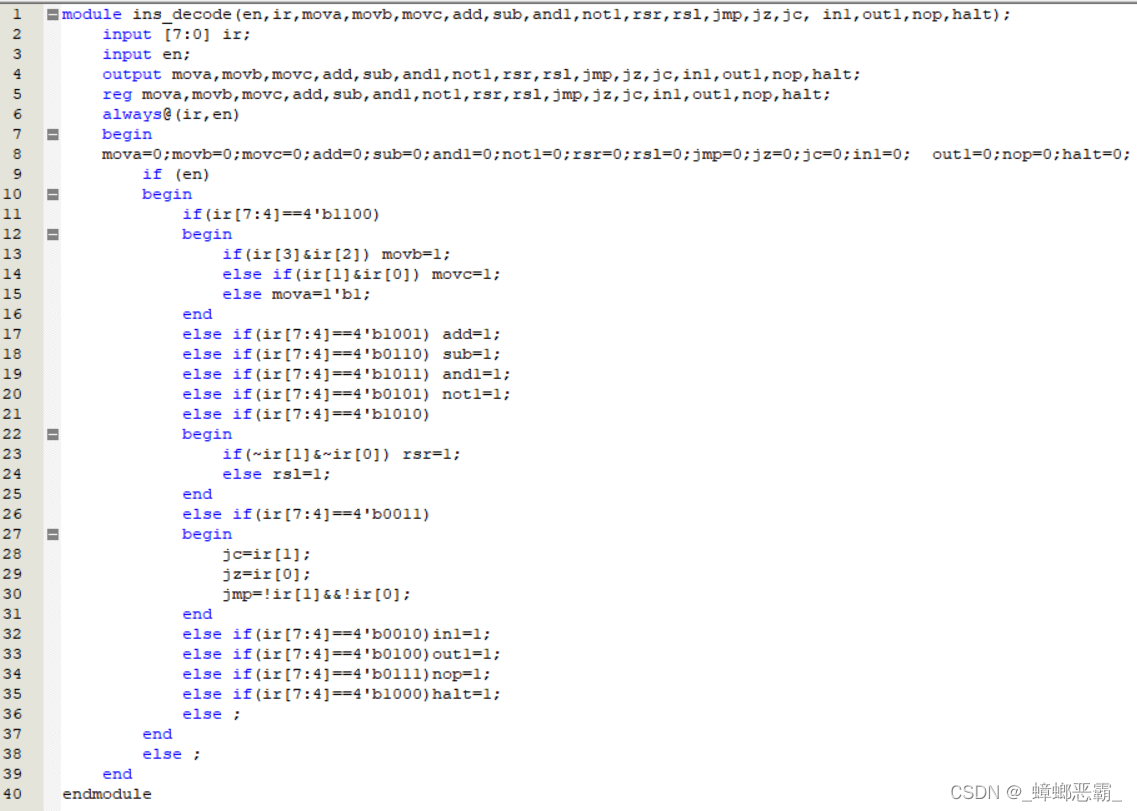

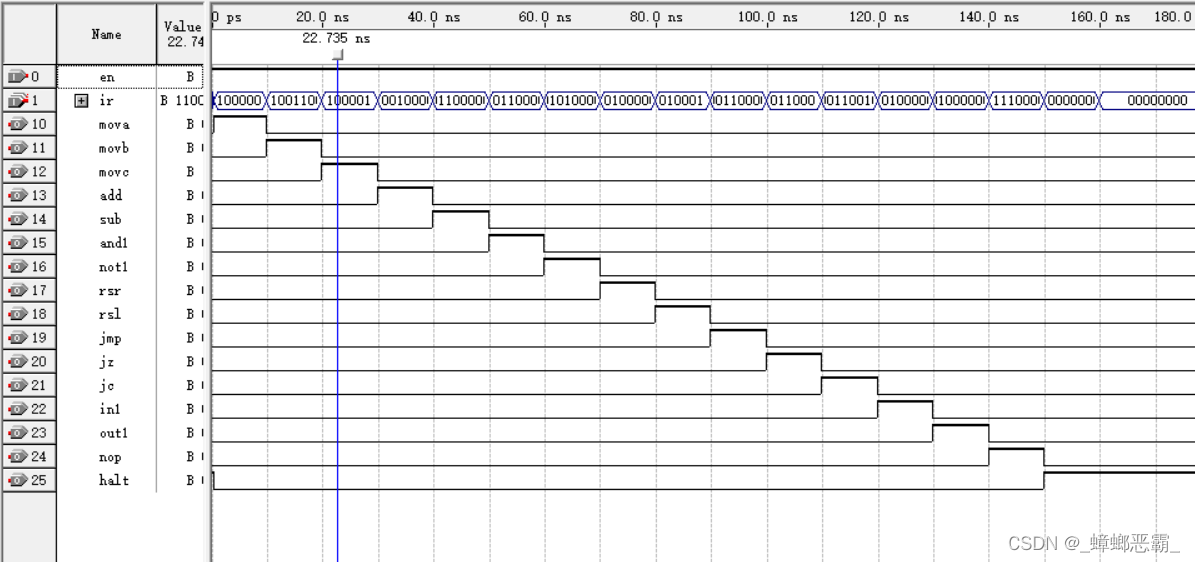

1. 指令译码器

(1)接口设计

指令译码器的输入输出引脚如图所示。en 为使能信号,ir[7..0]是 8 位指令编码,输出是对应的 16 条指令。

(2)功能实现

指令译码器是根据指令系统表中的指令编码,对输入的 8 位指令进行解析,判定是哪条指令,则对应指令的输出为 1,否则输出为 0。

Verilog代码:

(3)功能仿真验证

en为1时,输入相应的指令码ir,各个对应的指令信号输出为1,其余指令输出为0,

所以本程序通过了功能仿真。

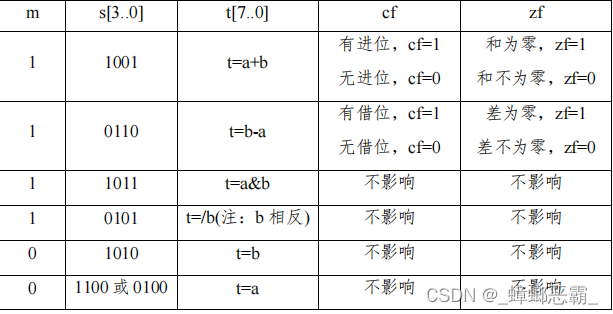

2.算术逻辑单元ALU

(1) 接口设计

m和s[3..0]是控制信号,控制a[7..0]和b[7..0]输入的数据进行什么操作, 并将产生的结果输出到t[7..0]、cf和zf。

(2) 功能实现

在 S3~S0和 M 的控制下,实现运算,经移位逻辑送入总线 BUS;由/WE 控制和 R1 的编码选择 RWBA1、RWBA0,将 BUS 上的数据写入通用寄存器 R1。其中 ADD 和 SUB 指令影响状态位 Cf 和 Zf。

Verilog代码:

(3) 功能仿真验证

0-10ns,m为1,控制信号分别为 1001 时,执行t=a+b操作,无进位,cf=0;

10-20ns,m=1,执行 t=a+b 操作,有进位,结果为0,cf、zf为1。

30-40ns,m=1,执行 t=a-b操作,结果为0,zf为1。

所以,功能仿真正确。

3. 8重3-1多路复用器

(1)接口设计

8 重 3-1 多路复用器有 3 个输入 1 个输出,每个输入和输出都是 8 位,所以称之为 8 重.

MADD 选择将哪个输入传至输出,8 重 3-1 多路复用器的引脚如图所示:

(2)功能实现

多路复用器是一个组合电路,它可以从多个输入中选择一个输入,并将信息直接传输到输出。选择哪一条输入线由一组输入变量控制,它们被称为选择输入。通常, 2^n条输入线要 n 个选择输入,选择输入的位组合决定选择哪个输入线。

Verilog代码:

(3)功能仿真验证

0-10ns, madd=00,输出 y=a。

10-20ns,madd=01,输出 y=b。

20-30ns,madd=10,输出 y=c。

所以,仿真验证正确。

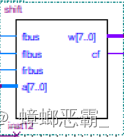

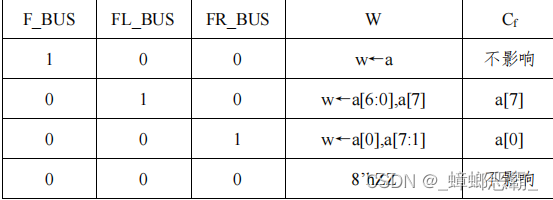

4. 移位逻辑

(1)接口设计

输入端口为来自 ALU 的数据,以及三个控制信号;

输出为通向总线的数据和 C 标志的控制。

(2)功能实现

经移位逻辑循环右移或循环左移后送入总线BUS;

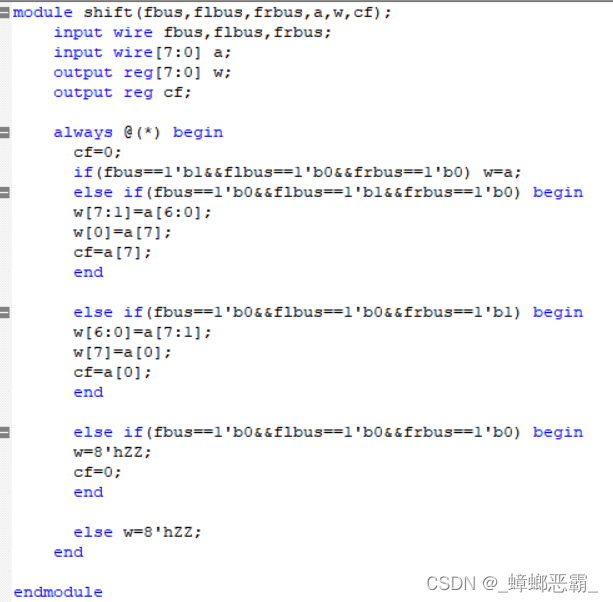

Verilog代码:

(3)功能仿真验证

- 0ns-10ns时, fbus=1。 不进行移位操作,输出w=a=00000100;

- 10ns-20ns时,flbus=1。进行左移位操作,输出w=0000010;

- 20ns-30ns时,frbus=1。进行右移位操作,输出w=00000001。

所以,功能仿真正确

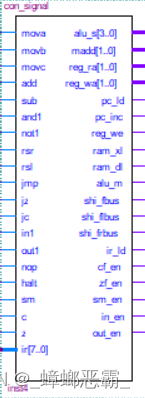

5. 控制信号产生逻辑

(1)接口设计

模块的输入端口是来自指令译码器的 16 个指令信号,以及控制取址和执行周期的 SM 信号,还有指令码的直接输入 IR,以及cf,zf 状态位的输入,输出端口为各个模块的一些控制信号,在图中均已标明。

(2)功能实现

控制信号产生逻辑接收指令译码器的输出,在 SM、IR[7..0]以及状态位 Cf 和 Zf 的配合下产生每个模块所需要的控制信号。

Verilog代码:

(3)功能仿真验证

- 当 add 指令执行时,shi_fbus,alu_en,cf_en,zf_en,sm_en 输出为 1,其他输出为 0,alu_s 为 1001,reg_ra 输出 01,reg_wa 输出 00。

- 当 sub 指令执行时,shi_fbus 和 alu_m,cf_en,zf_en 和 sm_en 输出为 1,其他输出为 0,alu_s 输出 0110,reg_ra 输出 01,reg_wa 输出 00。

- 当 and1 指令执行时,shi_fbus 和 alu_m 和 sm_en 输出 1,其他输出 0,alu_s输出 1011,reg_ra 输出 01,reg_wa 输出 00。

- 当not1 指令执行时,shi_fbus 和 alu_m 和 sm_en 输出 1,其他输出 0,alu_s 输出 0101,reg_ra 输出 00,reg_wa 输出 00。

- 当rsl 指令执行时,shi_flbus 和 alu_m 和 cf_en 和 sm_en 输出 0,其他输出 0,alu_s 输出 1010,reg_ra 和 reg_wa 输出 00。

- 当rsr 指令执行时,shi_frbus 和 alu_m 和 cf_en 和 sm_en 输出 1,其他输出 0,alu_s 输出 1010,reg_ra 输出 11,reg_wa 输出 00。

- 当in1 指令执行时,sm_en 和 in_en 输出 1,其他输出 0。

- 当out1 指令执行时,sm_en 和 out_en 输出 1,其他输出 0。

- 当 mova 指令执行时,shi_fbus 和 sm_en 输出 1,其他输出为 0,madd 输出 00,alu_s 输出为 1100,reg_ra 输出 01,reg_wa 输出 00。

- 当 movb 指令执行时,ram_xl 和 shi_fbus 和 reg_we 和 sm_en 输出为 1,其他输出为 0,madd 输出为 10,alu_s 输出为 1100,reg_ra 输出 01,reg_wa 输出 11。

- 当 movc 指令执行时,ram_dl 和 sm_en 输出为 1,其他输出为 0,madd 输出 01,alu_s 输出 1100,reg_ra 输出 11,reg_wa 输出 01。

- 当jmp 指令执行时,ram_dl,pc_ld,reg_we 和 sm_en 输出 1,其他输出 0,alu_s输出 0001,reg_ra 和 reg_wa 输出 00。

- 当jz 指令为 1 和 jc 指令为 1 时,若 z 和 c 为 1 时,ram_dl 和 pc_ld 和 reg_we和 sm_en 输出为 1,其他输出为 0。若 z 和 c 为 0 时,pc_inc 和 reg_we 和 sm_en 输出 1,其他输出 0,正确

- 当nop 指令执行时,sm_en 输出 1,其他输出为0。

- 当halt指令执行时,输出全为0。

所以,仿真验证正确。

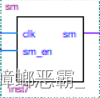

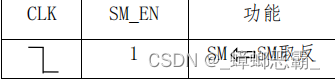

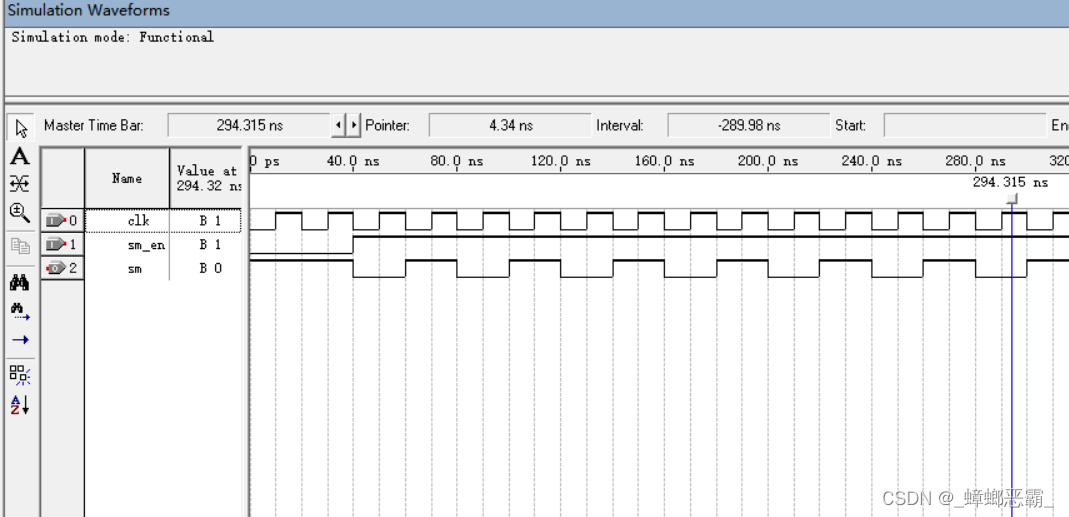

6. SM

(1)接口设计

输入端口包括时钟信号和使能信号,输出为当前是取 指周期还是执行指令周期。

(2)功能实现

SM为0 是取指令周期;SM为1是执行指令周期。

Verilog代码:

(3)功能仿真验证

0-40ns, sm_en 为 0,sm 保持输出不变。

40-280ns,sm_en 为 1,在时钟下降沿,sm 翻转。

所以,功能仿真正确。

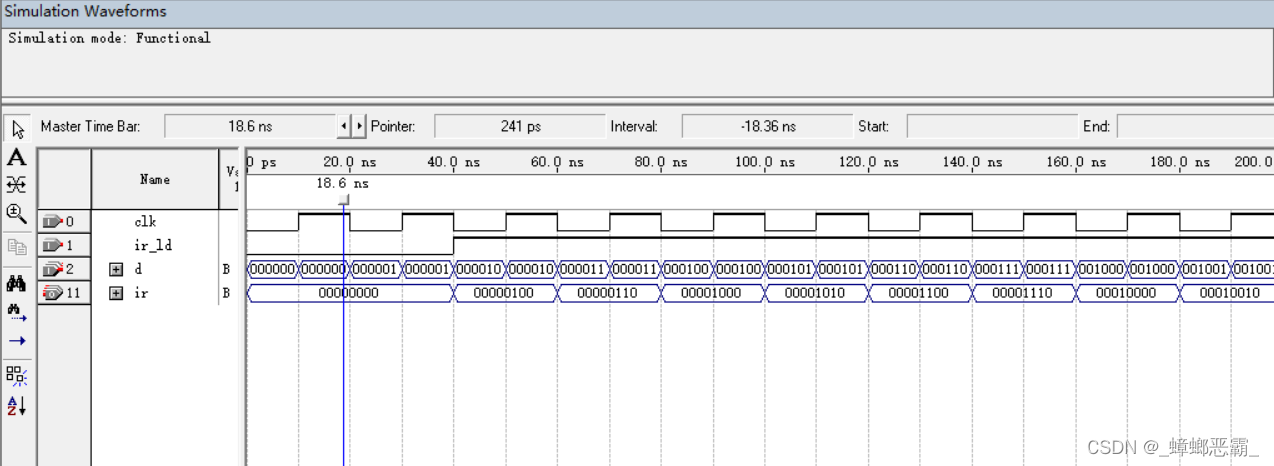

7. 指令寄存器IR

(1)接口设计

输入端口有时钟信号 clk,控制读入信号 ir_ld,来自 总线的信号 d,输出为 ir。

(2)功能实现

指令寄存器用于暂存当前正在执行的指令。

当控制信号IR_LD为1时,指令寄存器在时钟信号CLK的下降沿将总线传输的指令写入寄存器。

指令寄存器IR是一个8位寄存器。

Verilog代码:

(3)功能仿真验证

0-40ns, ir_ld 为 0,则 ir 输出保持不变。

0-40ns, ir_ld 为 0,则 ir 输出保持不变。

40-200ns,ir_ld 为 1,执行写入操作,在时钟的下降沿,将输入d写入输出 ir 。

所以,功能仿真正确。

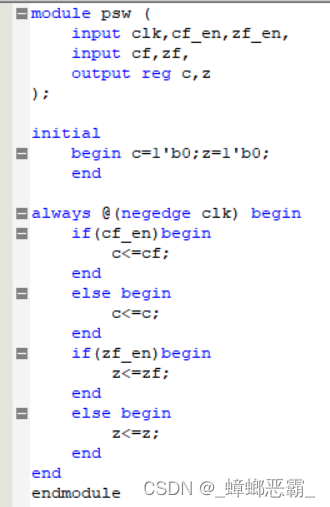

8. 状态寄存器PSW

(1)接口设计

输入端口包括时钟信号,c/z 使能信号和 alu 和移位逻 辑传输过来的 cf,zf 信号。输出为 c,z 信号

(2)功能实现

PSW用来存放ADD、SUB、RSR、RSL指令执行结果的状态标志,如有无借位进位(C)、结果是否为零(Z)。

本模型机PSW是一个2位寄存器。

Verilog代码:

(3)功能仿真验证

cf_en为1 时,clk下降沿将cf写入c。如40ns,120ns,c值均变为cf。

cf_en为1 时,clk下降沿将cf写入c。如40ns,120ns,c值均变为cf。

zf_en为1 时,clk下降沿将zf写入z。如40ns,100ns,c值均变为cf。

cf_en, zf_en为0时,不论clk为上升沿还是下降沿,z,c值均不变。

所以,仿真验证正确。

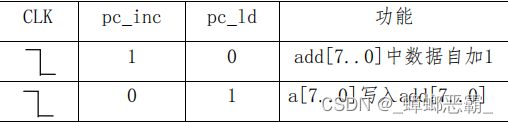

9. 指令计数器PC

(1)接口设计

模块的输入端有来自总线上的数据 a,以及来自控制信号发生逻辑的加载信号 pc_ld,自加信号 pc_inc,时钟信号 clk。输出端口为通向选择器的地址输出 add。

(2)功能实现

CPU执行一条指令,根据PC中存放的指令地址,将指令从RAM读出写入指令寄存器IR中,此过程称为“取指令”。在每条指令读取后,指令计数器PC中的地址自动加1,指向下一条指令在RAM中的存放地址。跳转指令如JMP、JZ、JC让程序跳转至指定地址去执行,这时PC需要装载跳转地址。

Verilog代码:

(3)功能仿真验证

20ns时,时钟下降沿,pc_inc 为 0,pc_ld 为 0,输出地址保持不变。

40ns 处,时钟下降沿,pc_inc 为 0,pc_ld 为 1,输出地址加载为输入的地址。

60ns 时,为时钟下降沿,pc_inc 为 1,pc_ld 为 0,对地址编码加一。

所以,仿真验证正确。

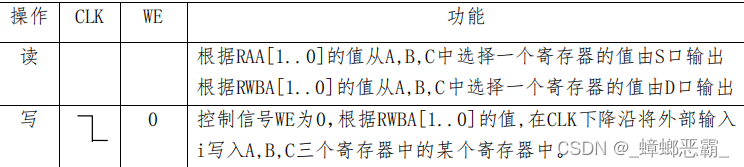

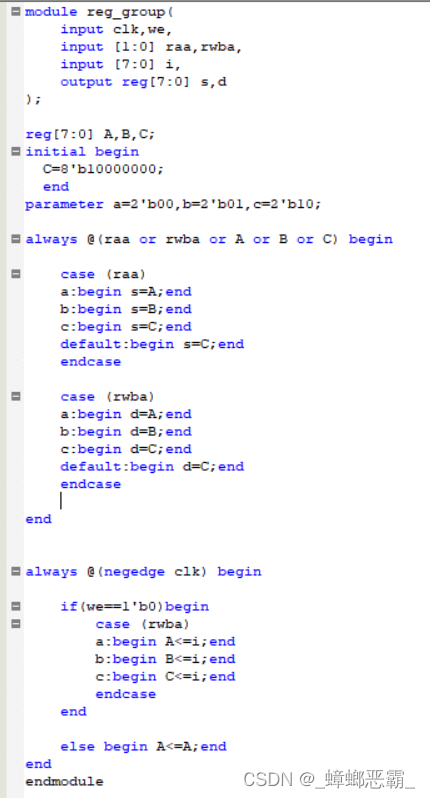

10. 通用寄存器组

(1)接口设计

通用寄存器组模块的输入端口包括来自控制信号发生单元的写使能信号 WE、源寄存器地址 raa,目的寄存器地址 rwba,来自总线上的数据输入 i 和系统时钟信号 clk。输出包括 s 和 d。

(2)功能实现

寄存器主要用来保存操作数和运算结果等信息,从而节省从RAM中读取操作数所需占用总线和访问存储器的时间。

Verilog代码:

(3)功能仿真验证

0-60ns:(写入)we=0,在时钟下降沿根据WA的值对写入哪个寄存器进行选择,00选择A寄存器,01选择B寄存器,10选择C寄存器,分别将00000001写入A,00000010写入B,00000011写入C。

60-120ns:(读)we=1,根据RA的值决定S输出哪个寄存器的值;WA的值决定D输出哪个寄存器的值。看RA和S这两行,RA为00时应输出A寄存器的值为00000001,看S的输出,恰好为00000001;RA为01应输出B寄存器的值为00000010,此时S输出为00000010,符合要求;RA为10应输出C寄存器的值为00000011,此时S输出也为00000011,符合要求。

所以,仿真验证正确。

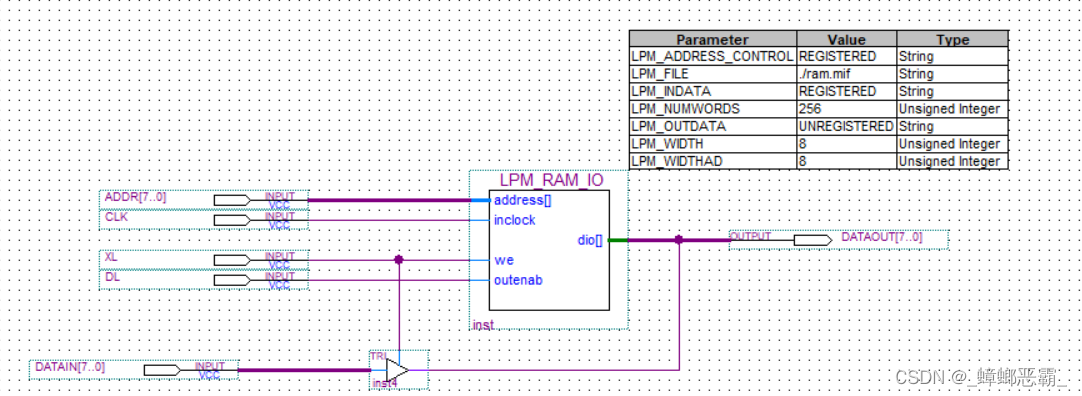

11. RAM的使用

(1)接口设计

ADDR[7..0]指定访问RAM的地址,时钟CLK上升沿,XL为1,将外部输入DATAIN[7..0]写入RAM的对应存储单元。不改变ADDR[7..0]的值,这时DL为1,读取RAM,查看DATAOUT[7..0]中的输出是否跟前面写入的数据是否一致,从而学习对RAM的读写操作。

(2)功能实现

电路图:

(3)功能仿真验证

0-30ns:此时XL=1,DL=0,在时钟上升沿将Dio的数据写入address所指定的存储单元,即将10101010存入01010101的位置。

30-60ns:此时XL=0,DL=1,会在时钟上升沿将address所储存的单元数据输出,此时address所指定的位置为00000011,为了验证读取的正确性,已经提前将MIF文件中的0000011位的数据改为33。观察此时的DATAOUT,恰好为00100001,即为2进制的33,功能正确。

60-90ns:此时address发生改变,变为01010101,验证之前是否成功写入与读出的正确性,观察此时的DATAOUT,恰好为之前读入的10101010,功能正确。之后XLDL均为0时输出高阻态,整个元件符合功能。

所以,仿真验证正确。

四、系统测试

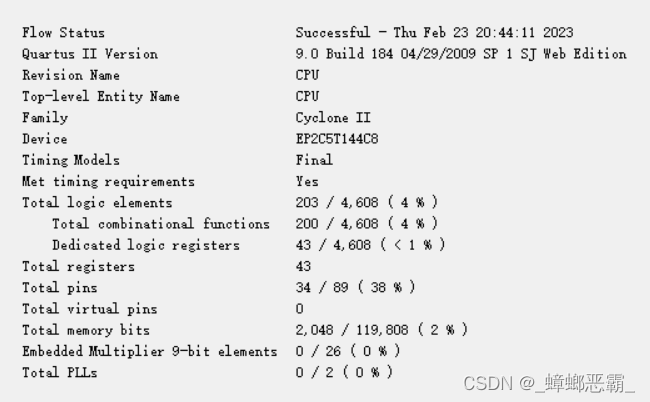

4.1测试环境

FPGA芯片:Cyclone II EP2C5T144C8

开发软件: Quartus II 9.0 Build 184 04/29/2009 SP 1SJ Web Edition

操作系统: Windows 11 家庭中文版

4.2 测试代码

1.仿真的测试程序

| 地址 | 指令码 | 汇编符号 | 作用 | 信号变化 |

| 0 | 00110000 | JMP | 跳转 | |

| 1 | 00000100 | JMP 04H | 跳转到 0000 0100 | |

| 4 | 00100000 | IN A | 输入 1000 0011 | A=1000 0011 |

| 5 | 01000000 | OUT A | 输出 1000 0011 | |

| 6 | 11001100 | MOV M,A | A->M | C=1000 0011 |

| 7 | 11000111 | MOV B M | M->B | B=1000 0011 |

| 8 | 01100001 | SUB A B | (A-B) ->A | A=0000 0000,Z=1 |

| 9 | 00110001 | JZ | 条件跳转(Z==1) | |

| 10 | 00010000 | JZ 10H | 条件跳转到0001 0000 | |

| 16 | 01010000 | NOT A | /A -> A | A=1111 1111 |

| 17 | 10110010 | AND A C | (A&C) ->A | A=1000 0000 |

| 18 | 10010001 | ADD A B | (A+B) ->A | A=0000 0011,C=1 |

| 19 | 00110010 | JC | 条件跳转(C==1) | |

| 20 | 00011000 | JC 18H | 条件跳转到0001 1000 | |

| 24 | 01110000 | NOP | ||

| 25 | 10100000 | RSR A | A循环右移一位 ->A | A=1000 0001 |

| 26 | 01000000 | OUT A | 输出A | |

| 27 | 10100111 | RSL B | B 循环左移一位 ->B | B=0000 0111 |

| 28 | 11000001 | MOV A B | B->A | A=0000 0111 |

| 29 | 01000000 | OUT A | ||

| 30 | 10000000 | HALT | 停机 | |

| 31 | 10010001 | ADD A B | ||

| 32 | 01000000 | OUT A |

Mif文件:

2.下板的测试程序

Mif文件:

4.3测试结果

1.仿真的测试结果

三个out信号,对应的输出结果为83H,81H,07H;

结果与预期一致,故测试成功。

2.下板的测试结果

外部输入为10000011,那么 JZ 和 JC 都跳转成功,执行输出 OUT A,输出为 01111100(7CH)

改变外部输入,使其不为 10000011,那么 JZ 不成功,实现停机 HALT。

将程序下载到FPGA板后,功能成功实现。

4.4 模型机性能分析

模型机工程占用资源数为203,

时钟频率为34.57MHz(28.924ns),在正常范围内。

五、实验总结、必得体会及建议

5.1 从需要掌握的理论、遇到的困难、解决的办法以及经验教训等方面进行总结。

从指令译码器、算术逻辑单元,8重3-1多路复用器、移位逻辑、控制信号产生逻辑、SM、指令寄存器、状态寄存器、指令计数器、通用寄存器组、RAM,到模型机的整体实现验证。当看到最后波形图输出结果83H,81H,07H的时候,虽然其中遇到过诸多困难,但是最后有种搭积木看到最后成果的成就感,也有理论勇于实践的欣喜。

再从模型机到其他的子部件,回过头看,更觉得一步错步步错,只有所有的子部件都能正确实现其功能,最后汇总到一个整体上时,才有可能运行出正确的结果。

不足的是,有些元器件有优化的空间,可以节约耗费的资源、减小延迟。

5.2 对本实验内容、过程和方法的改进建议(可选项)。

无。

1688

1688

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?