目录

实验三 8位算术逻辑运算实验

一、实验目的

1.掌握算术逻辑运算器单元ALU(74LS181)的工作原理。

2.掌握简单运算器的数据传送通路组成原理。

3.验证算术逻辑运算功能发生器74LS181的组合功能。

4.按给定数据,完成实验指导书中的算术/逻辑运算。

二、实验原理

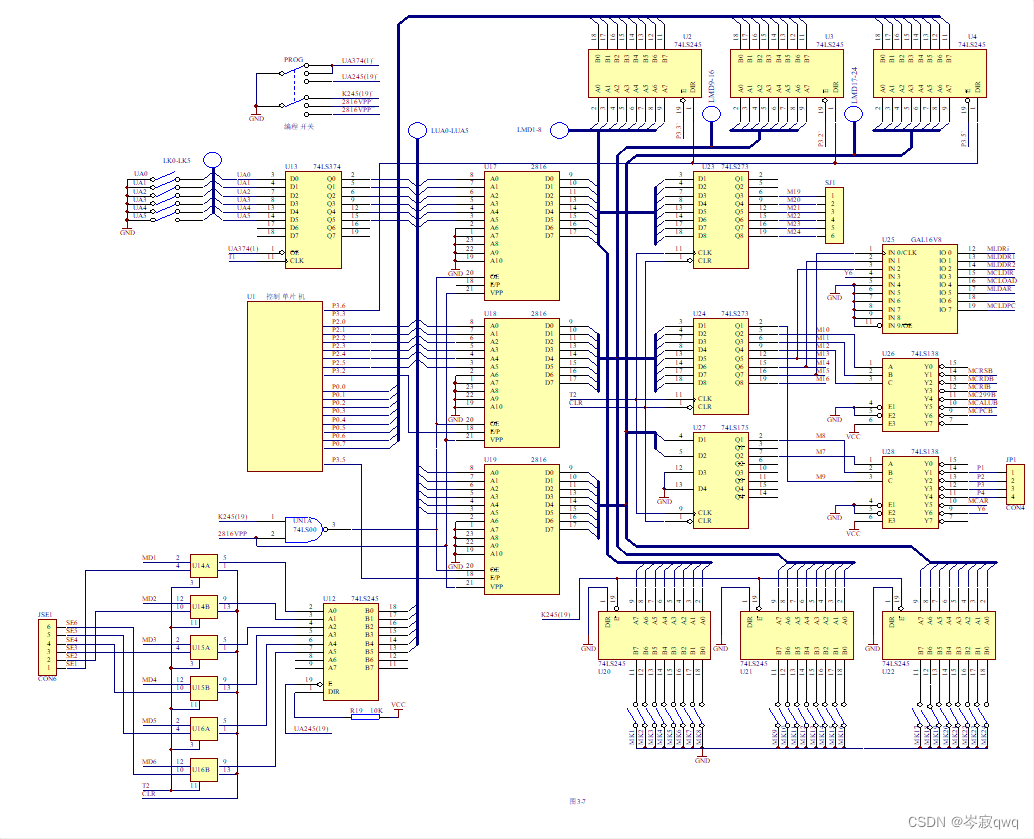

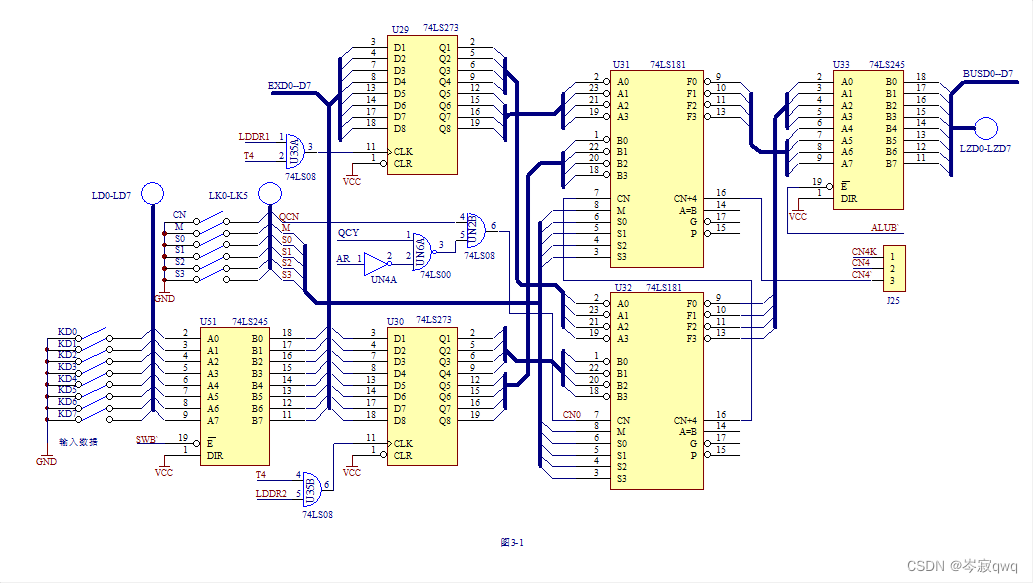

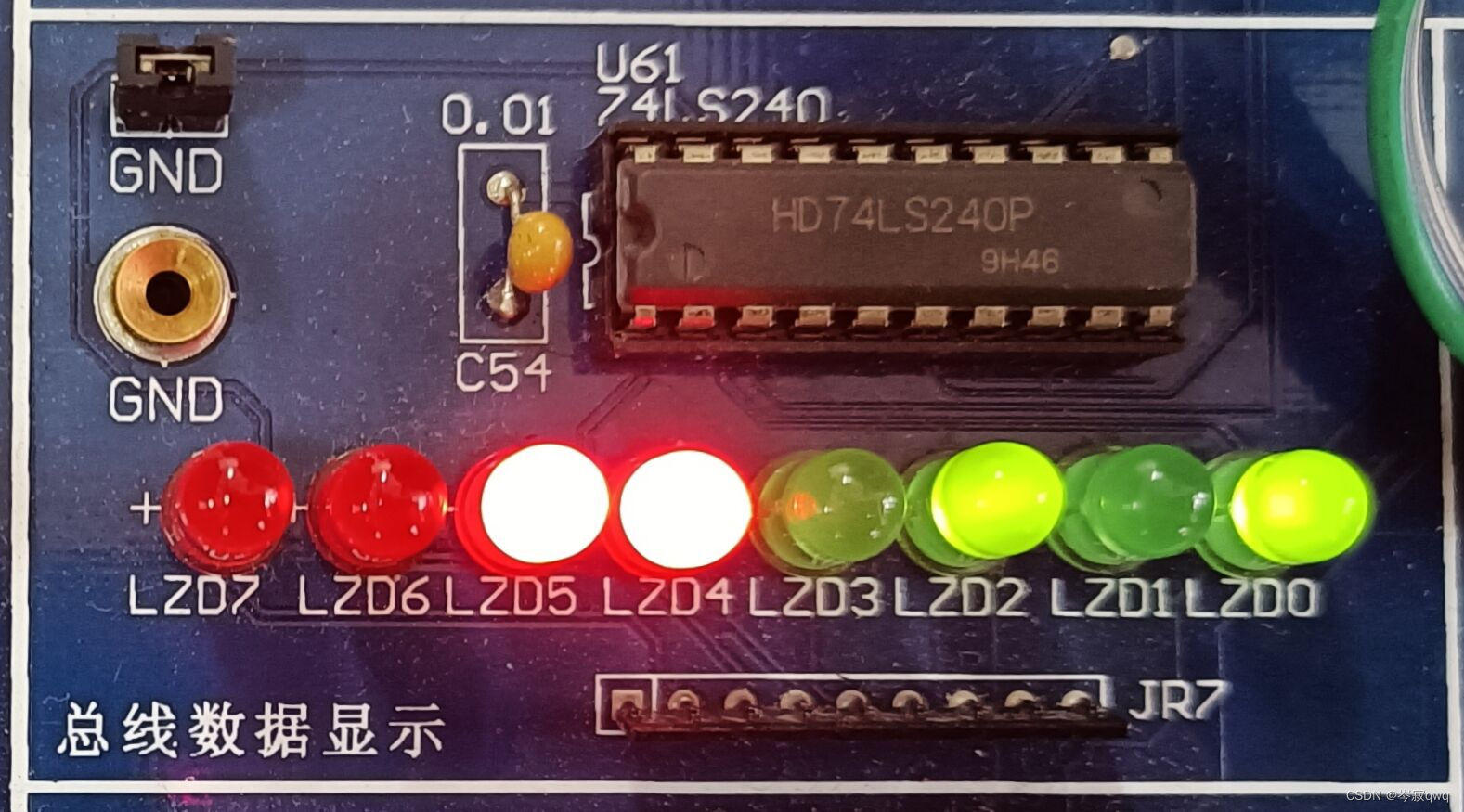

实验中所用的运算器数据通路如图所示。其中运算器由两片74LS181以并/串形成8位字长的ALU构成。运算器的输出经过一个三态门74LS245(U33)到ALUO1插座,实验时用8芯排线和内部数据总线BUSD0~D7插座BUS1~6中的任一个相连,内部数据总线通过LZD0~LZD7显示灯显示;运算器的两个数据输入端分别由二个锁存器74LS273(U29、U30)锁存,两个锁存器的输入并联后连至插座ALUBUS,实验时通过8芯排线连至外部数据总线EXD0~D7插座EXJ1~EXJ3中的任一个;参与运算的数据来自于8位数据开并KD0~KD7,并经过一三态门74LS245(U51)直接连至外部数据总线EXD0~EXD7,通过数据开关输入的数据由LD0~LD7显示。

图中算术逻辑运算功能发生器 74LS181(U31、U32)的功能控制信号S3、S2、S1、S0、CN、M并行相连后连至SJ2插座,实验时通过6芯排线连至6位功能开关插座UJ2,以手动方式用二进制开关S3、S2、S1、S0、CN、M来模拟74LS181(U31、U32)的功能控制信号S3、S2、S1、S0、CN、M;其它电平控制信号LDDR1、LDDR2、ALUB`、SWB`以手动方式用二进制开关LDDR1、LDDR2、ALUB、SWB来模拟,这几个信号有自动和手动两种方式产生,通过跳线器切换,其中ALUB`、SWB`为低电平有效,LDDR1、LDDR2为高电平有效。

另有信号T4为脉冲信号,在手动方式下进行实验时,只需将跳线器J23上T4与手动脉冲发生开关的输出端SD相连,按动手动脉冲开关,即可获得实验所需的单脉冲。

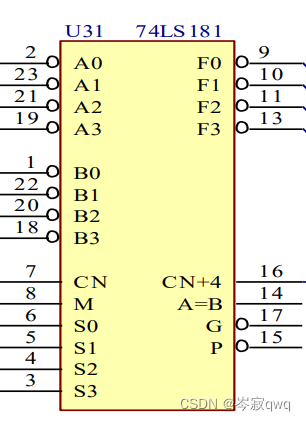

74LS181芯片:

(1)芯片功能:

74LS181是一个2输入4输出的编码器,通过输入0~15输出0000~1111编码的芯片。74ls181芯片总共由22个引脚,其中包括8个数据输入端。这八个都是低电平有效。还包括S0、S1、S2、S3这四个控制端,这四个控制端主要控制两个四位输入数据的运算。

(2)芯片引脚:

A0~A3、B0~B3:数据输入端(低电平有效)。

F0~F3:二进制输出端,以四位二进制形式输出运算结果。

CN:处理进入芯片前进位制。

CN4:记录运算后的进位,

G:先行进位产生端。

P:先行进位传递函数。

S0、S1、S2、S3:四个控制端,控制两个四位输入数据的运算(加、减、与、或)。

M:控制芯片的运算方式,包括算术运算和逻辑运算。

(3)芯片功能表:

| 模式选择 | M=0 算术运算 | M=1 | |

| S3S2S1S0 | Cn=1 无进位 | Cn=0带进位 | 逻辑运算 |

| 0 0 0 0 | F=A | F=A plus 1 | F= |

| 0 0 0 1 | F=A+B | F=(A+B) plus 1 | F= |

| 0 0 1 0 | F=A+ | F=(A+ | F= |

| 0 0 1 1 | F= -1 | F=0 | F=0 |

| 0 1 0 0 | F=A plus (A | F=A plus (A | F= |

| 0 1 0 1 | F=(A+B) plus (A | F=(A+B) plus (A | F= |

| 0 1 1 0 | F=A minus B minus 1 | F=A minus B | F= |

| 0 1 1 1 | F=(A | F=A | F=A |

| 1 0 0 0 | F=A plus AB | F=A plus AB plus 1 | F= |

| 1 0 0 1 | F=A plus B | F=A plus B plus 1 | F= |

| 1 0 1 0 | F=(A+ | F=(A+ | F=B |

| 1 0 1 1 | F=AB minus 1 | F=AB | F=AB |

| 1 1 0 0 | F=A plus A | F=A plus A plus 1 | F=1 |

| 1 1 0 1 | F=(A+B) plus A | F=(A+B) plus A plus 1 | F=A+ |

| 1 1 1 0 | F=(A+ | F=(A+ | F=A+B |

| 1 1 1 1 | F=A minus 1 | F=A | F=A |

三、实验电路

1、实验接线图

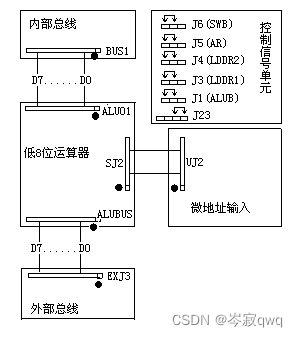

本实验用到4个主要模块:⑴低8位运算器模块,⑵数据输入并显示模块,⑶数据总线显示模块,⑷功能开关模块(借用微地址输入模块)。

根据实验原理详细接线如下:

⑴ ALUBUS连EXJ3;

⑵ ALUO1连BUS1;

⑶ SJ2连UJ2;

⑷ 跳线器J23上T4连SD;

⑸ LDDR1、LDDR2、ALUB、SWB四个跳线器拨在左边(手动方式);

⑹ AR跳线器拨在左边,同时开关AR拨在“1”电平。

2、实验原理图

四、实验步骤

1.连接线路,仔细查线无误后,接通电源。

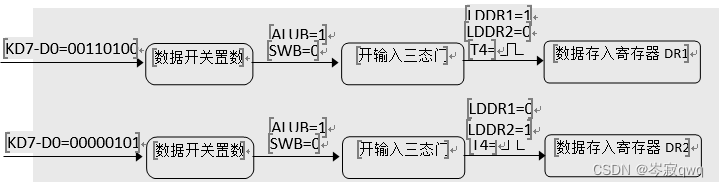

2.用二进制数码开关KD0~KD7向DR1和DR2寄存器置数。方法:关闭ALU输出三态门(ALUB`=1),开启输入三态门(SWB`=0),输入脉冲T4按手动脉冲发生按钮产生。设置数据开关具体操作步骤图示如下:(写入学号的后4位:34H,48H)

说明:LDDR1、LDDR2、ALUB`、SWB`四个信号电平由对应的开关LDDR1、LDDR2、ALUB、SWB给出,拨在上面为“1”,拨在下面为“0”,电平值由对应的显示灯显示,T4由手动脉冲开关给出。

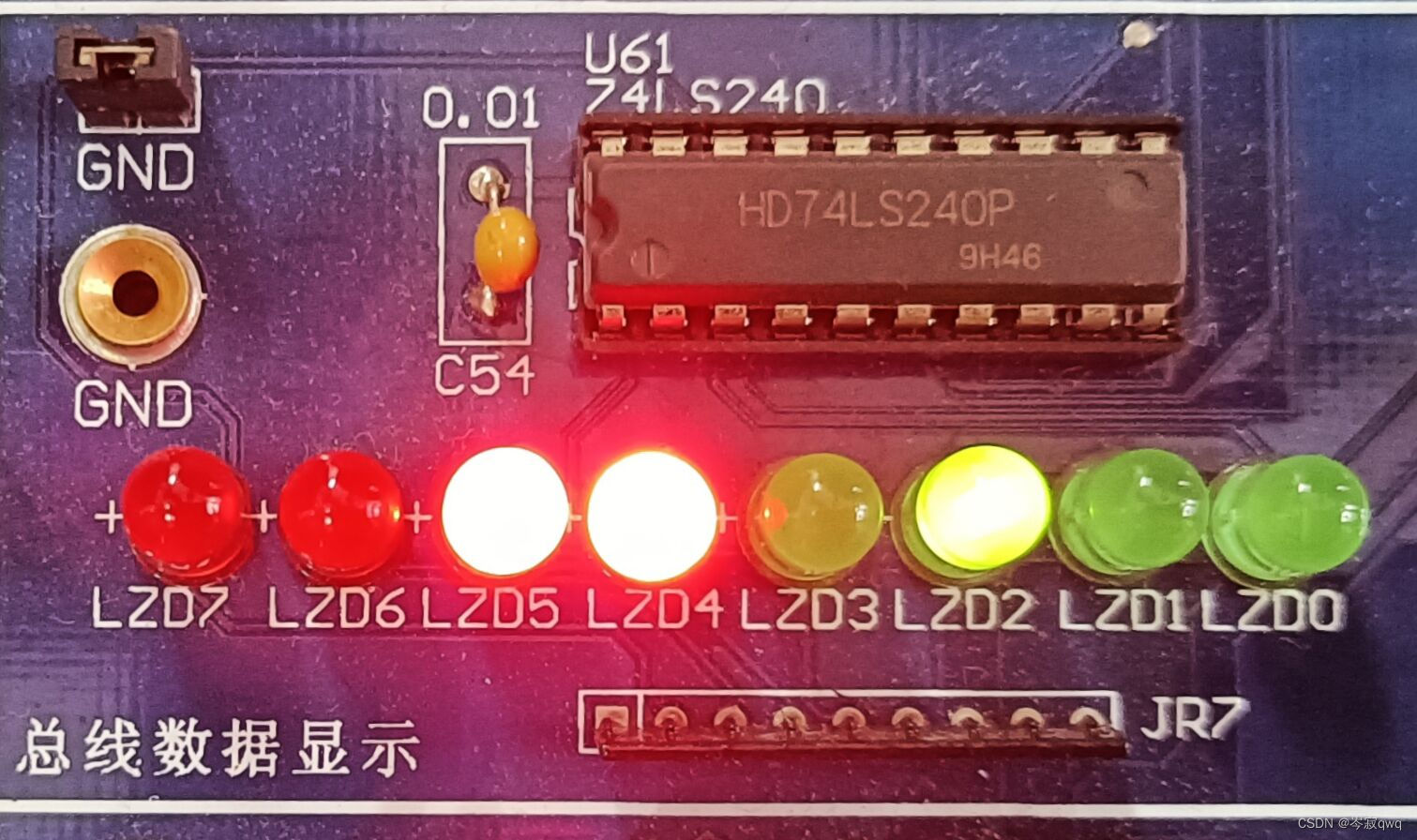

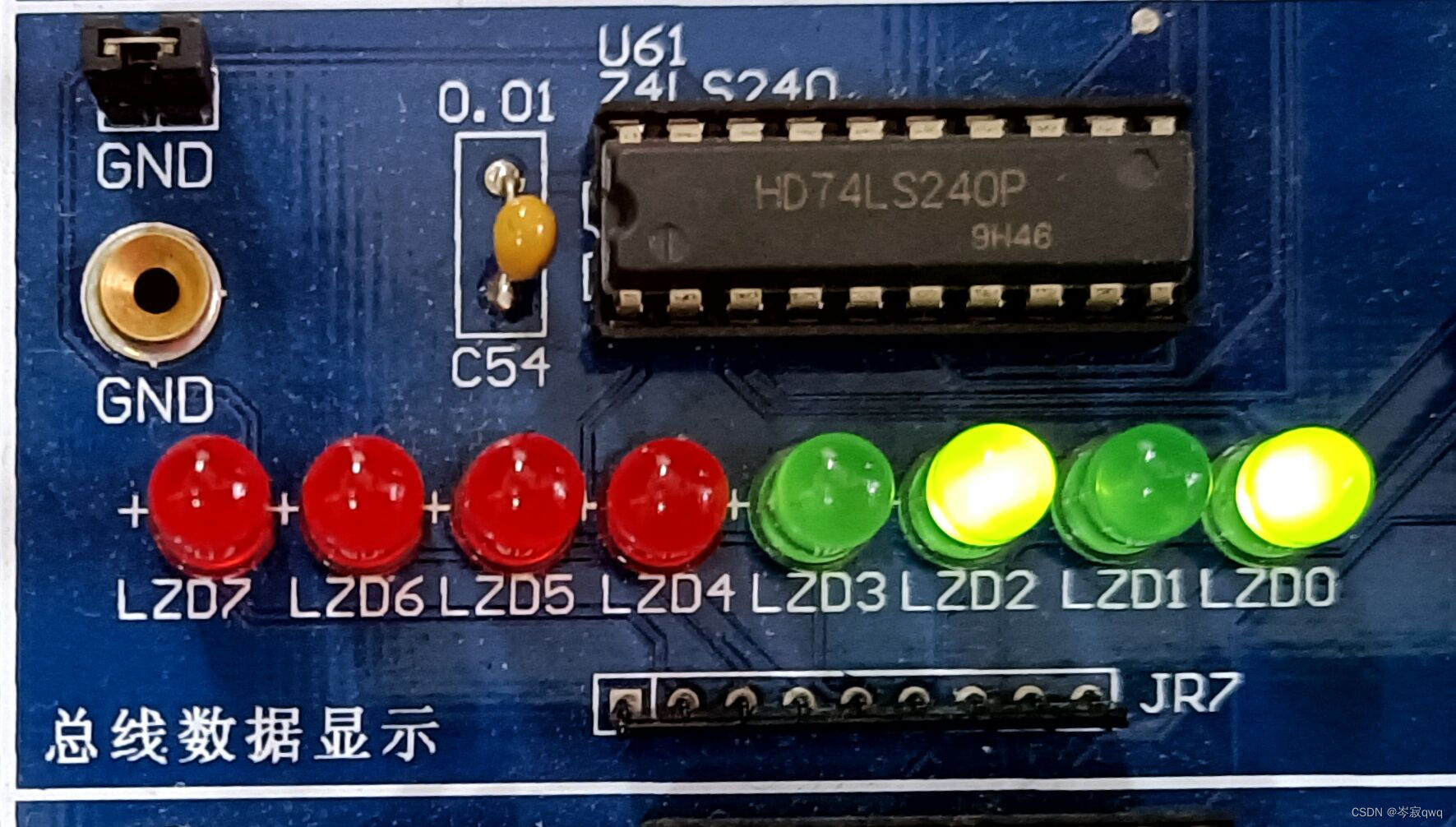

3.检验DR1和DR2中存入的数据是否正确,利用算术逻辑运算功能发生器 74LS181的逻辑功能,即M=1。具体操作为:关闭数据输入三态门SWB`=1,打开ALU输出三态门ALUB`=0,当置S3、S2、S1、S0、M为1 1 1 1 1时,总线指示灯显示DR1中的数,而置成1 0 1 0 1时总线指示灯显示DR2中的数。

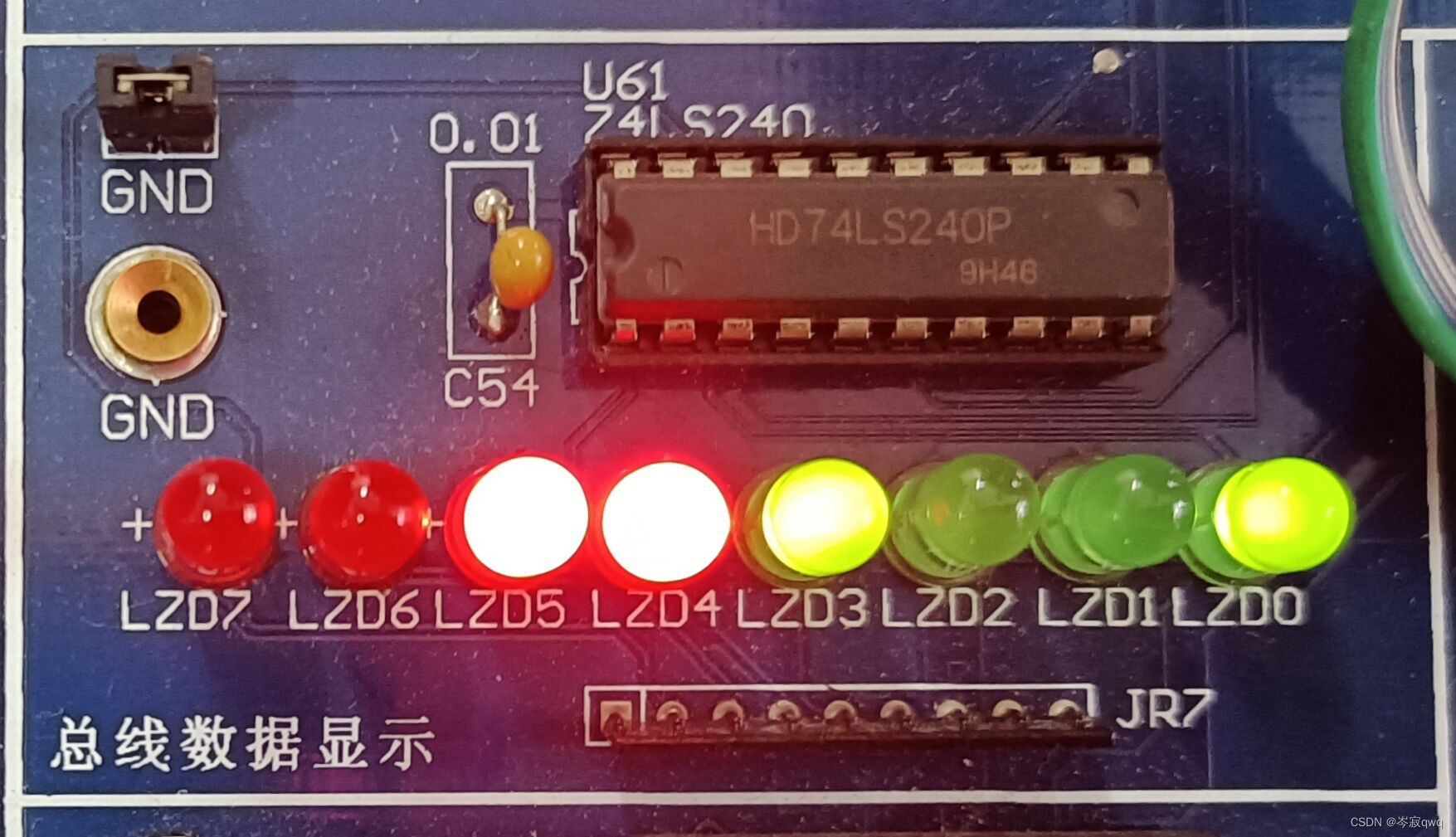

4.验证74LS181的算术运算和逻辑运算功能(采用正逻辑)。在给定DR1=34、DR2=05的情况下,改变算术逻辑运算功能发生器的功能设置,观察运算器的输出,完成实验数据的填写,并和理论分析进行比较、验证。

五、实验数据分析

| 操作数A DR1 | 操作数B DR2 | S3 S2 S1 S0 | M=0(算术运算) Cn=1无进位 | M=1(逻辑运算) |

| 34H

| 05H

| 1 0 0 1 | F=A plus B=39H

| F= |

| 1 1 1 0 | F=(A+ | F=A+B=35H

|

六、思考题

1.如果要实现F=A⨁B操作,S3、S2、S1、S0、M、Cn如何设置?

S3=0、S2=1、S1=1、S0=0、M=1、Cn任意

2.DR1置数完成后,如果不关闭控制端LDDR1会怎样?

LDDR1是寄存器DR1存数控制信号,高电平有效。LDDR2是寄存器DR2存数控制信号,高电平有效。如果不关闭控制端,则数据可能会丢失。

3.如果要实现F=AB操作,S3、S2、S1、S0、M、Cn如何设置?

S3=1、S2=0、S1=1、S0=1、M=0、Cn=0或者S3=1、S2=0、S1=1、S0=1、M=1、Cn任意

2466

2466

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?