目录

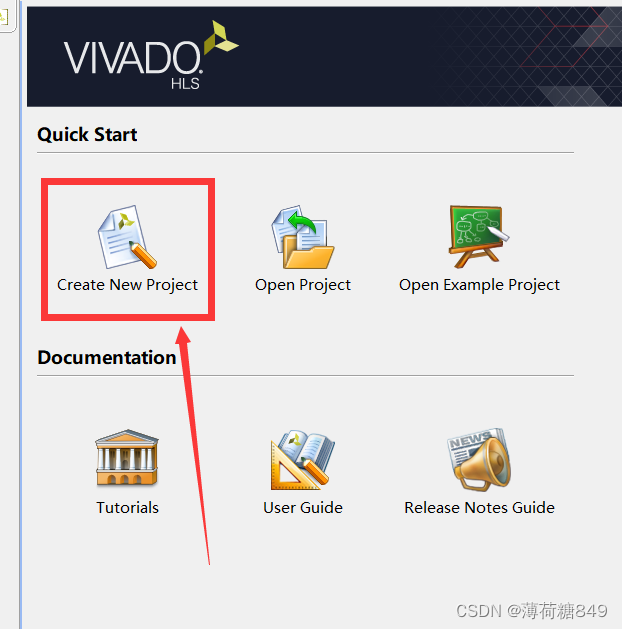

1、点击Vivado HLS 中的Create New Project

一、HLS入门

1. HLS是什么?与VHDL/Verilog编程技术有什么关系?

HLS(High-Level Synthesis,高层综合)是一种将高级语言描述的逻辑结构自动转换成低抽象级语言描述的电路模型的技术。与VHDL/Verilog编程技术的关系主要体现在HLS允许开发者使用C/C++等高级语言来编写可以在FPGA上运行的程序,而无需直接使用VHDL或Verilog这类硬件描述语言。

2. HLS有哪些关键技术问题?目前存在什么技术局限性?

HLS关键技术问题及局限性:

-

设计空间探索的挑战:HLS工具在转换过程中需要处理大量的设计选项和优化参数,如并行性、流水线化级别等。设计者需要对这些参数有深入理解才能做出最佳选择,这增加了设计的复杂性。

-

性能预测不准确:尽管HLS工具提供了性能评估功能,但这些预测往往与实际硬件实现存在差异。这种不准确性可能导致设计迭代,增加开发时间和成本。

-

资源利用效率:由于HLS工具的保守策略,生成的RTL代码可能不是最优的,导致FPGA资源利用率不高。这限制了设计的性能和面积效率。

-

支持的高级语言特性有限:虽然HLS支持C/C++等高级语言,但并非所有语言特性都能有效地转换为硬件描述。这限制了可以使用的编程技巧和算法。

-

调试和验证难度:与传统软件开发相比,HLS生成的硬件代码更难调试。硬件错误可能不会立即显现,且定位和修复错误更加困难。

除了上述内容外,对HLS技术的优化方向分析如下:

-

提高工具链的智能化:通过增强HLS工具的智能分析能力,帮助设计者更好地进行设计空间探索和性能预测,减少迭代次数。

-

扩展支持的语言特性:扩大HLS支持的高级语言特性集,使得更多复杂算法能够被有效转换,从而提升设计的灵活性和表达能力。

-

优化资源利用:通过改进算法和优化技术,提高FPGA资源的利用率,增强设计的性能和面积效率。

-

简化调试和验证过程:开发更加高效的调试工具和验证方法,降低硬件调试的难度,提高开发效率。

二、HLS入门程序编程

创建项目

1、点击Vivado HLS 中的Create New Project

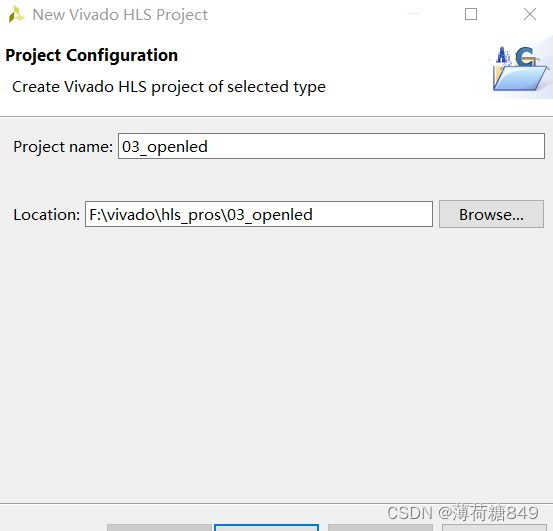

2、设置项目名

3、加入文件

分别新建文件Helloworld.cpp,Helloworld.h与tb_Helloworld.h

Helloworld.h

//helloworld.h

#ifndef _HELLOWORLD_H_

#define _HELLOWORLD_H_

#include "ap_int.h"

typedef ap_int<1> led_t;

void flash_led(led_t *led_o);

#endif

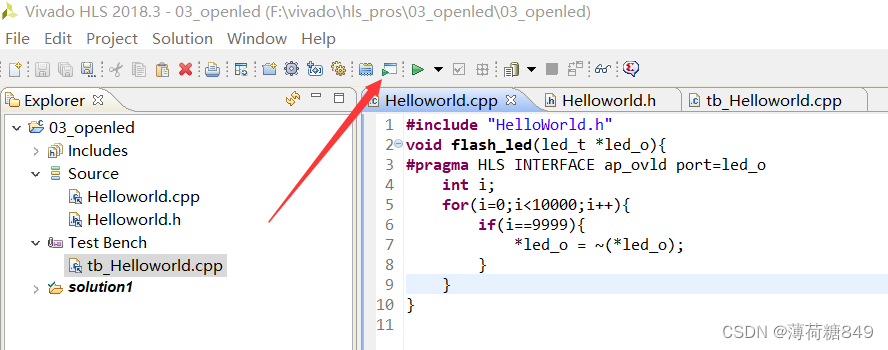

Helloworld.cpp

//Helloworld.cpp

#include "HelloWorld.h"

void flash_led(led_t *led_o){

#pragma HLS INTERFACE ap_ovld port=led_o

int i;

for(i=0;i<10000;i++){

if(i==9999){

*led_o = ~(*led_o);

}

}

}

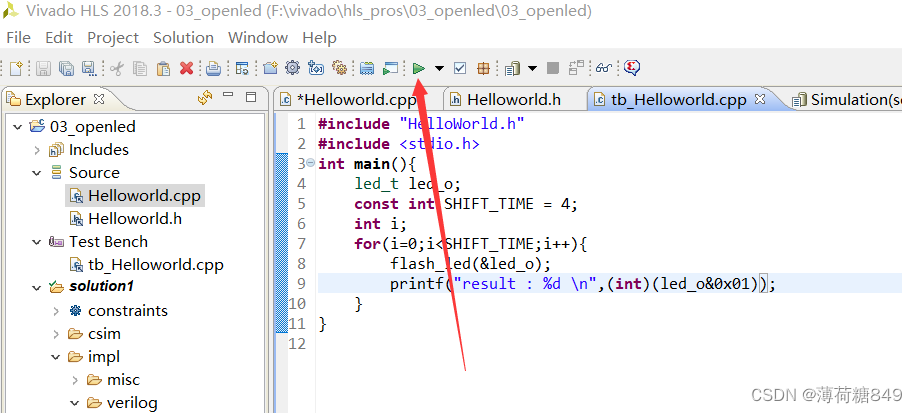

tb_Helloworld.cpp

#include "HelloWorld.h"

#include <stdio.h>

int main(){

led_t led_o;

const int SHIFT_TIME = 4;

int i;

for(i=0;i<SHIFT_TIME;i++){

flash_led(&led_o);

printf("result : %d \n",(int)(led_o&0x01));

}

}

4、仿真

在保存好代码之后,点击图中的这个按钮进行C仿真:

弹出界面后,什么都不用选,默认即可。

运行仿真后,出现下面这个界面就说明仿真成功了:

3、综合

进行综合之前,先选择Top Function。

点击Project -> Project Setting -> Synthesis ,点击Helloworld.cpp,并点击Browse选择函数flash_led。

然后点击c运行

结束后,会有一个总结文件如下:

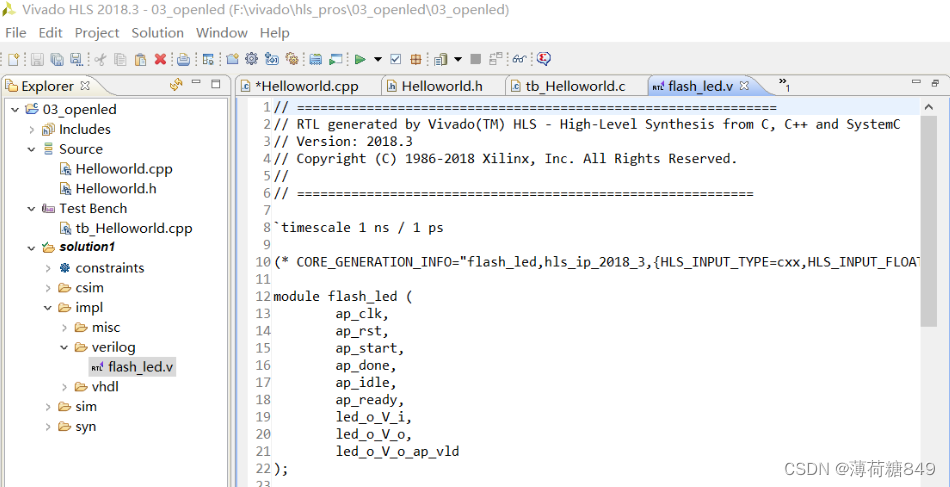

在solution1\impl\verilog中,有已经生成好的.v文件:

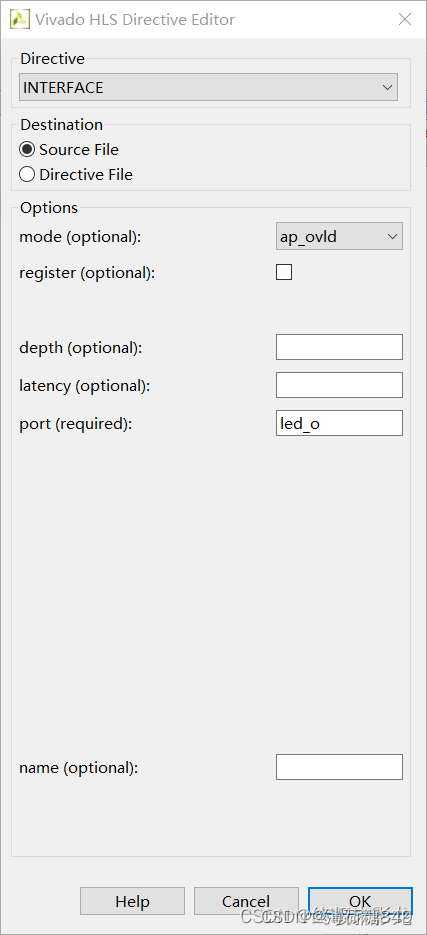

在Helloworld.cpp界面,右边的Drective界面,右键led_o,进入如下界面:

按上图来配置,并点击OK。

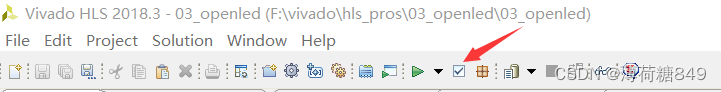

然后点击联合仿真:

仿真结束后,出现下面界面,说明联合仿真成功:

参考

HLS入门-LED闪烁仿真_hls c仿真设置-CSDN博客

379

379

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?