引言

Xilinx FPGA 产品线从经济型的 Spartan、Artix 系列到高性能的 Kintex、Virtex、Versal 系列,可以说涵盖了 FPGA 的绝大部分应用场景,那为什么还要设计 Zynq 系列?为什么不使用纯逻辑的 FPGA 系列?为什么不使用开发效率更高的 CPU、GPU?

设计往往源于实际需求,以生活中常见的路由器为例,其主要包括 路由转发 和 后台管理 两部分功能,路由转发功能我们往往关注其 吞吐量、波动、延迟 等指标,后台管理则更加关注其 灵活性。显然,仅使用纯逻辑 FPGA 或者 CPU 均难以兼顾上述需求,那能否将 FPGA 与 CPU 集成在一块 PCB 上?其中 FPGA 负责核心的 路由转发 功能,CPU 则负责 路由配置、后台管理、OTA 升级 等灵活性更高的功能,二者通过 总线通信,而这正是 Zynq 的设计理念

实际上现实中的路由器更多采用专用转发芯片 + CPU 的方案实现,这里更多是为了阐述 Zynq 的设计理念和开发优势

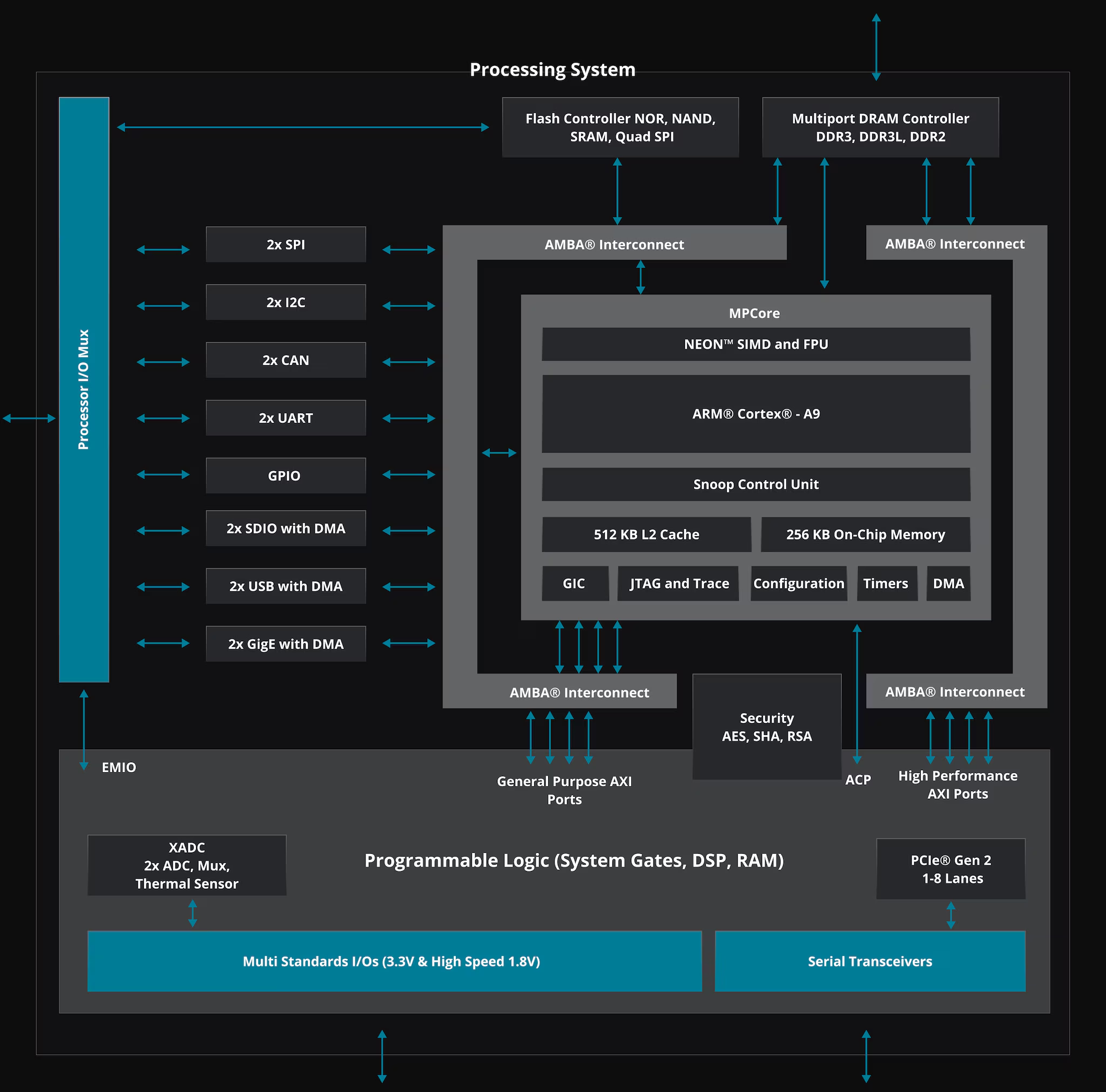

以 Zynq 7000 系列芯片架构为例,其内部分为 Processing System 和 Programmable Logic 两部分

Processing System:处理系统,由 ARM Cortex-A9 和 SPI、UART 等外设组成,通常称为 PS 端Programmable Logic:可编程逻辑,即我们通常所说的 FPGA,内部包括逻辑门阵列、DSP、RAM 等模块,通常称为 PL 端

两者之间通过 EMIO 和 AXI 总线通信,其中 AXI 总线又分为 GP 和 HP 以适应不同应用场景

产品线

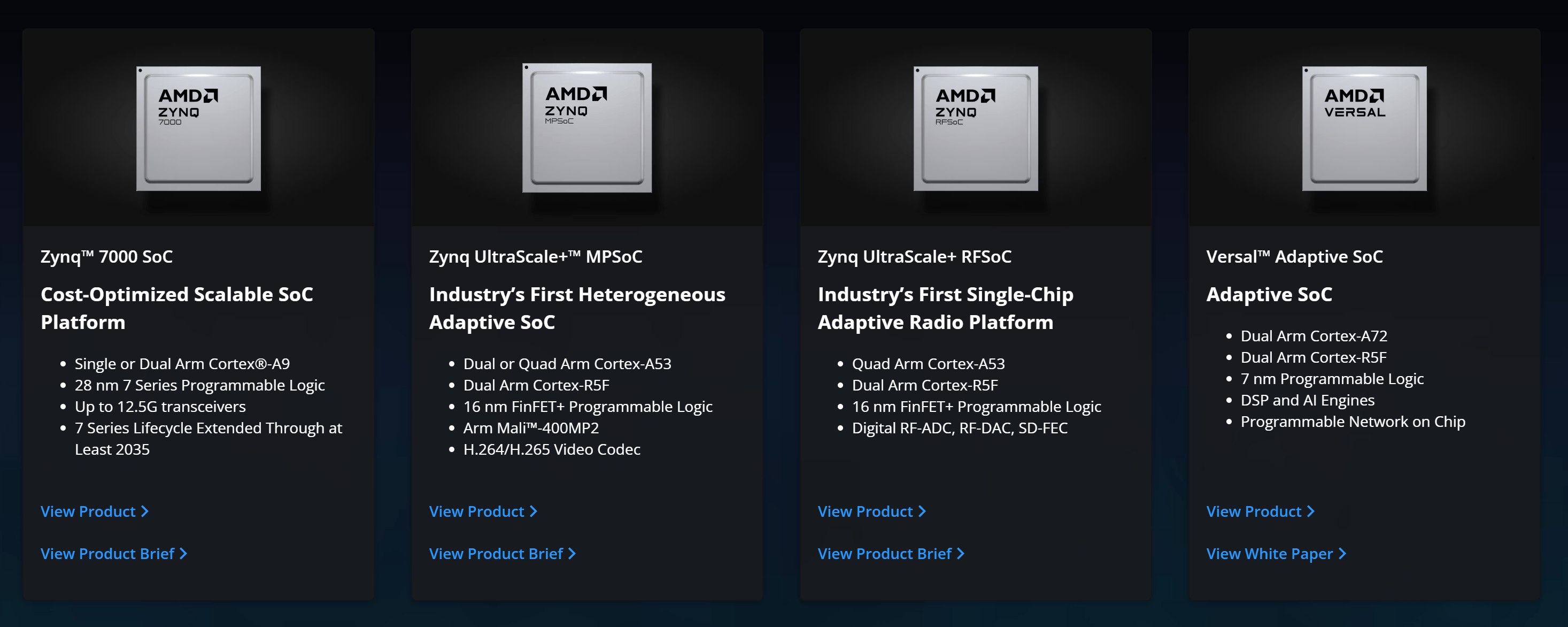

Xilinx Zynq 产品线 包括 Zynq™ 7000 SoC、Zynq UltraScale+™ MPSoC、Zynq UltraScale+ RFSoC 和 Versal™ Adaptive SoC 四个系列,其在 ARM 核心、制程、逻辑资源 和 外设 方面有所不同

Zynq™ 7000 SoC

该系列 PS 端集成 单核/双核 ARM Cortex-A9 核心,最大运行频率 766MHz - 1GHz,支持 DDR3、DDR3L、DDR2 和 LPDDR2,主要面向 成本敏感型设计

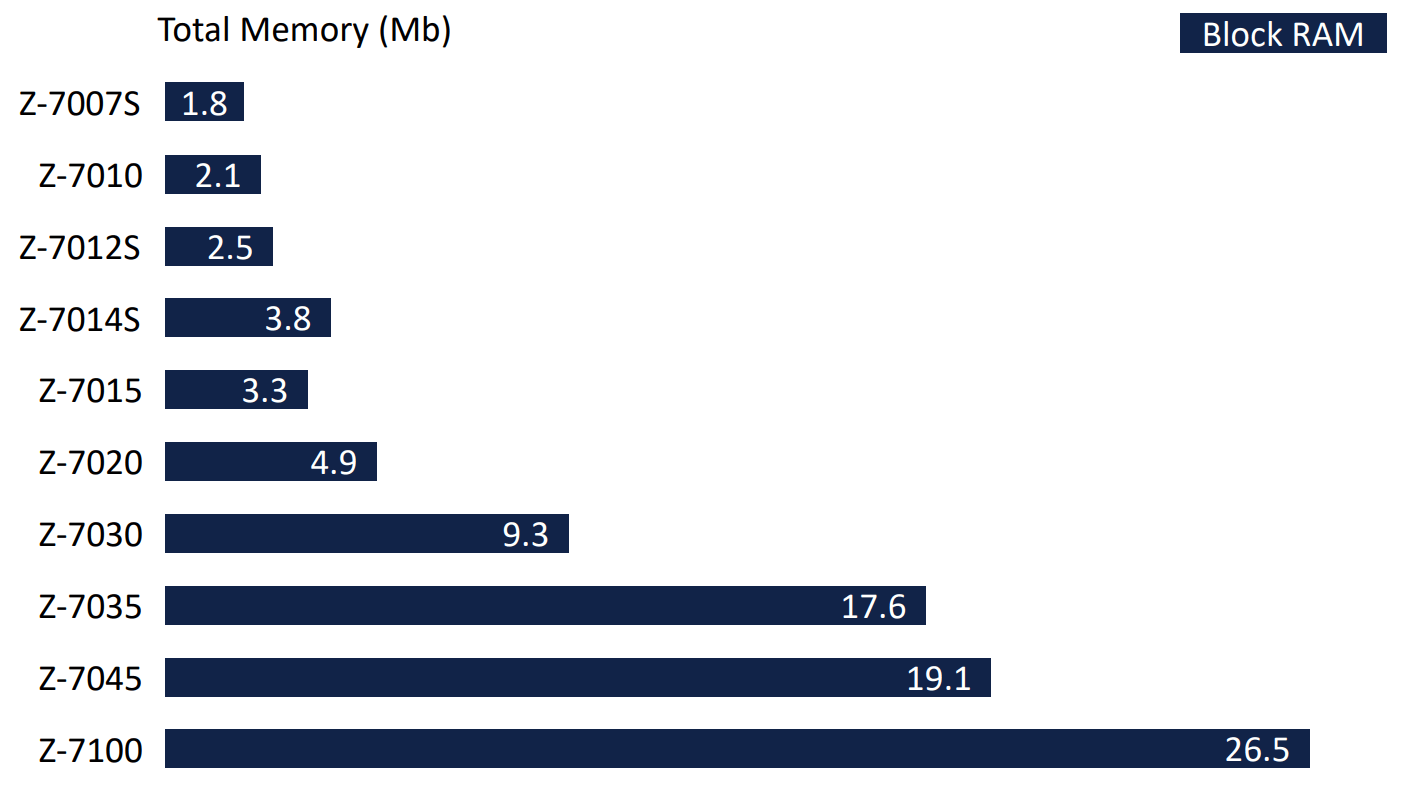

PL 端为 Artix-7 或 Kintex-7 系列,BRAM 大小为 1.8Mb - 26.5Mb

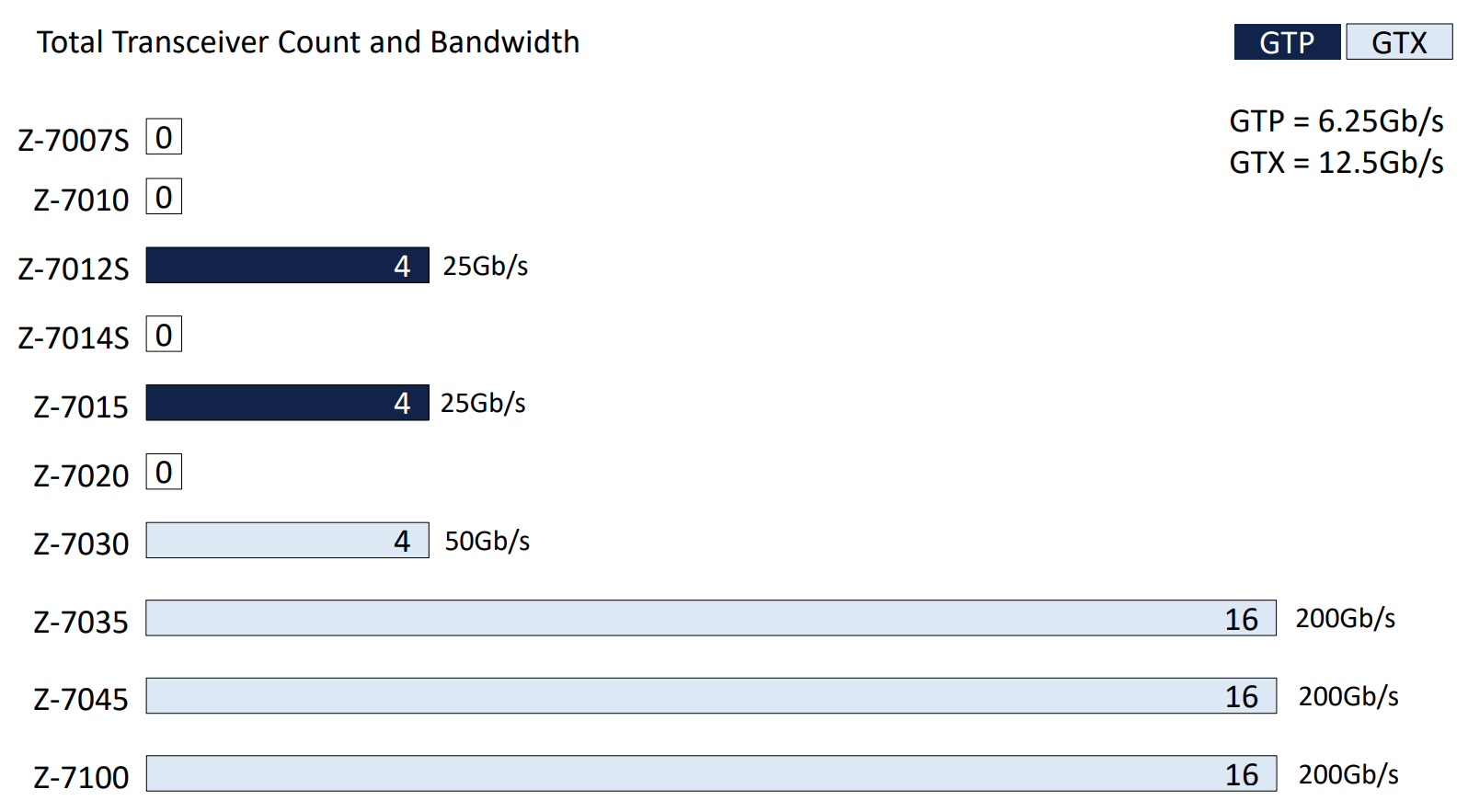

此外 7000 系列还包含了若干 串行收发器 GTP 和 GTX,最高传输速率可达 200Gbps

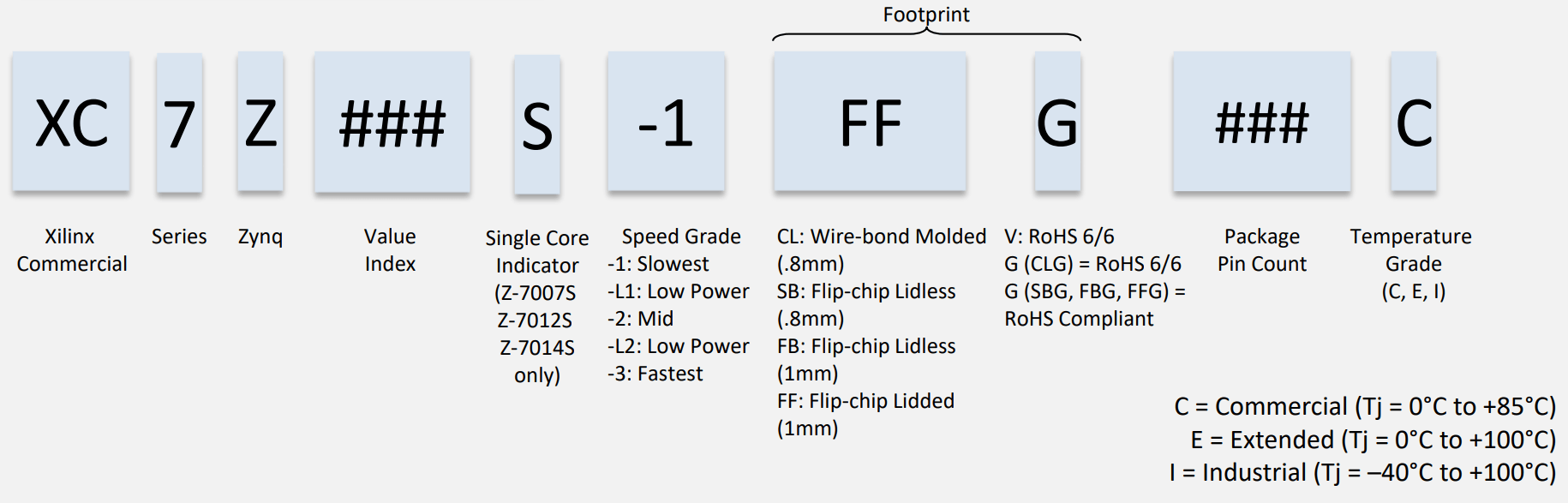

该系列产品的命名格式如下,读者在开发时可快速定位所需平台

以上数据来源于 Xilinx 产品手册

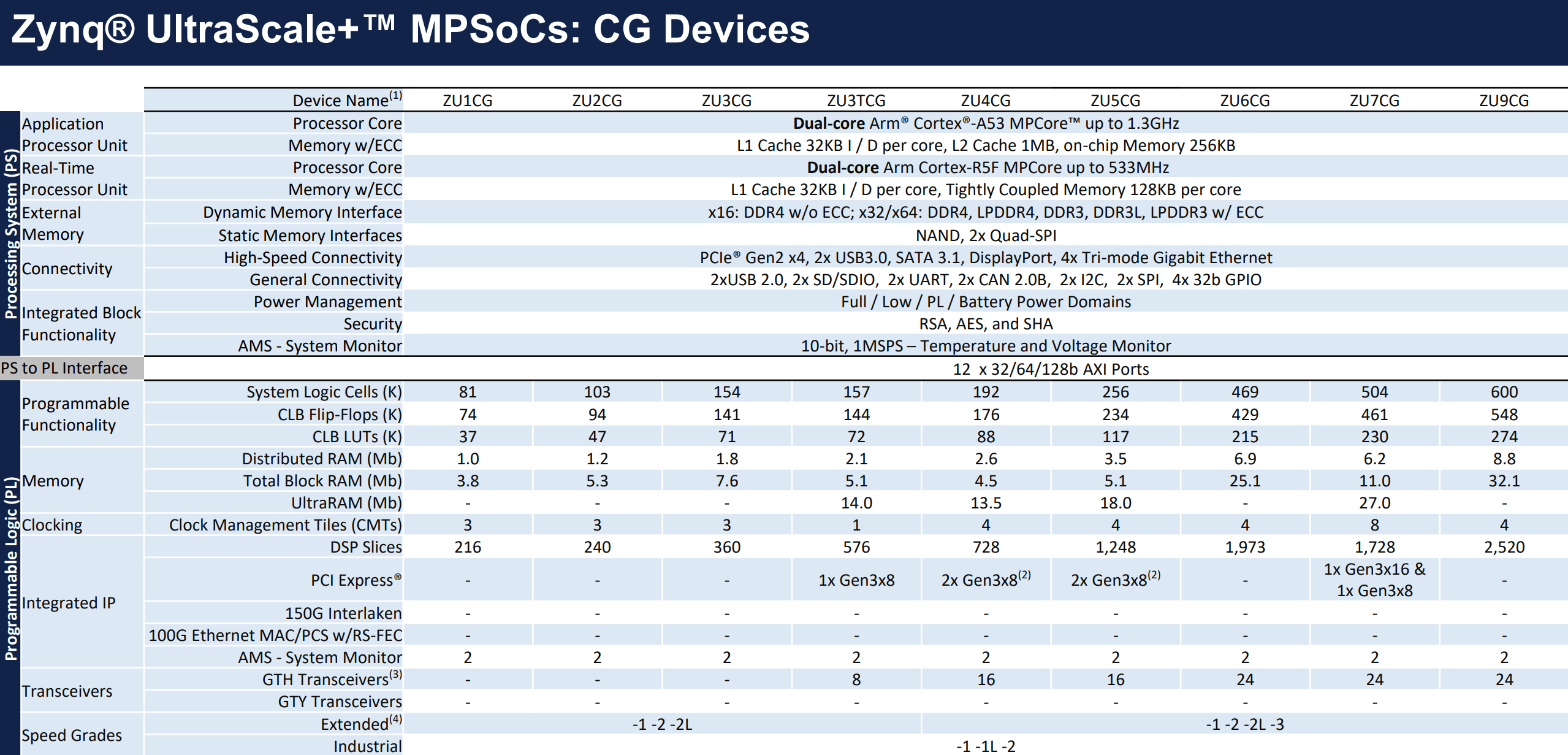

Zynq UltraScale+™ MPSoC

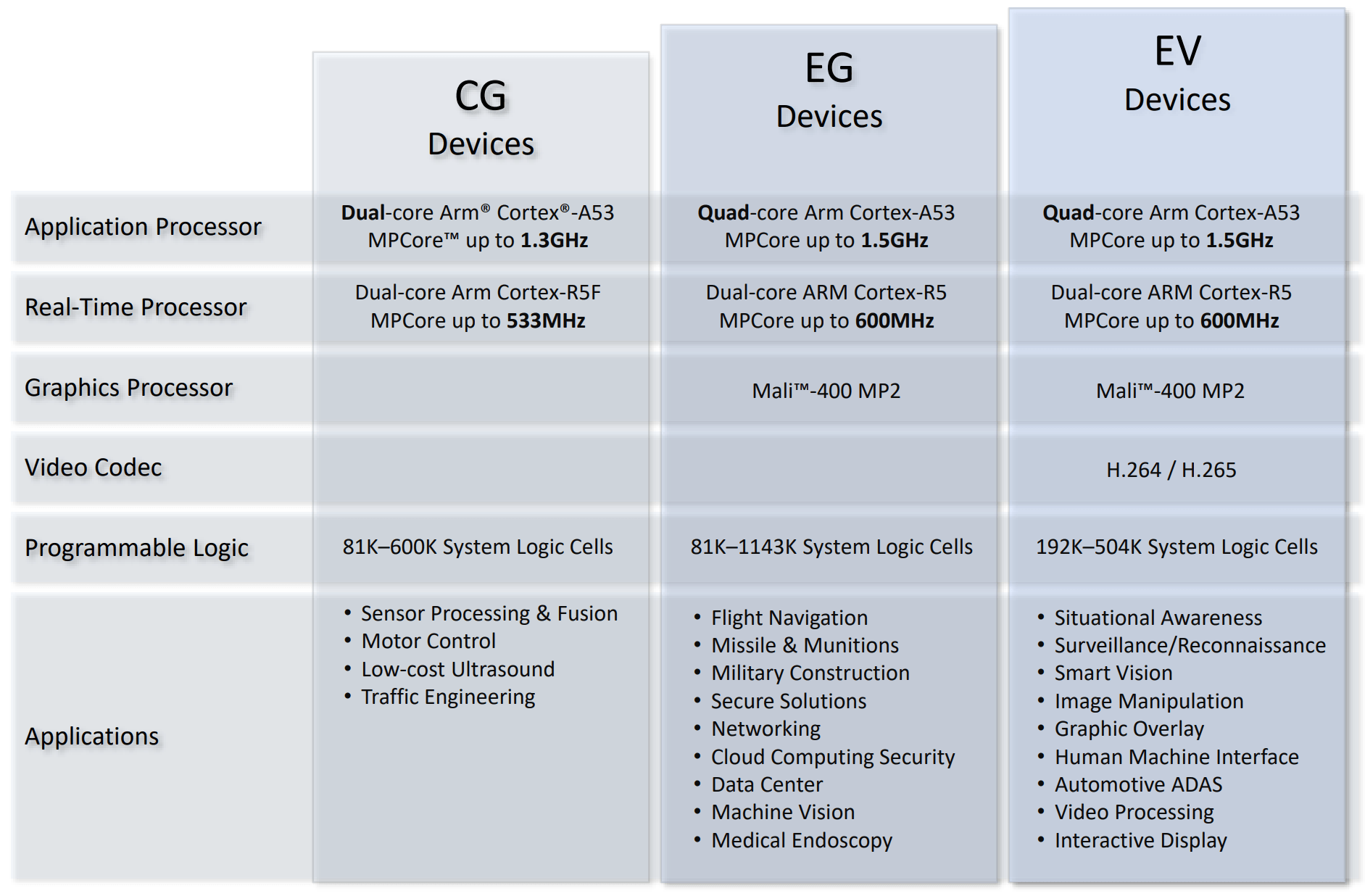

相较于 7000 系列,UltraScale + MPSoC 集成了性能更加强悍的 ARM Cortex-A53 核心,部分产品还集成了 GPU 和 H.264/H.265 视频编码单元,主要面向 图像/视频处理 场景

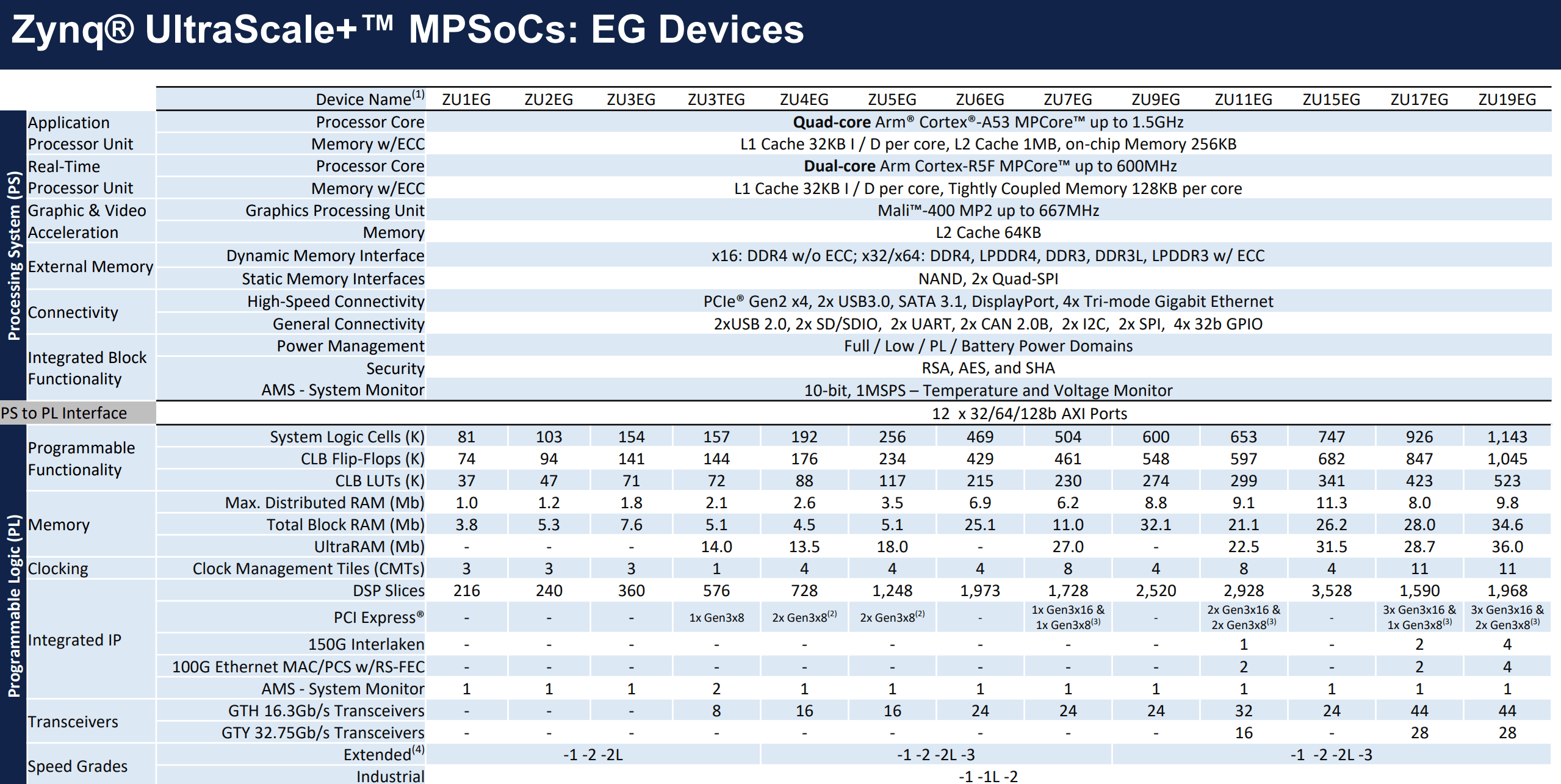

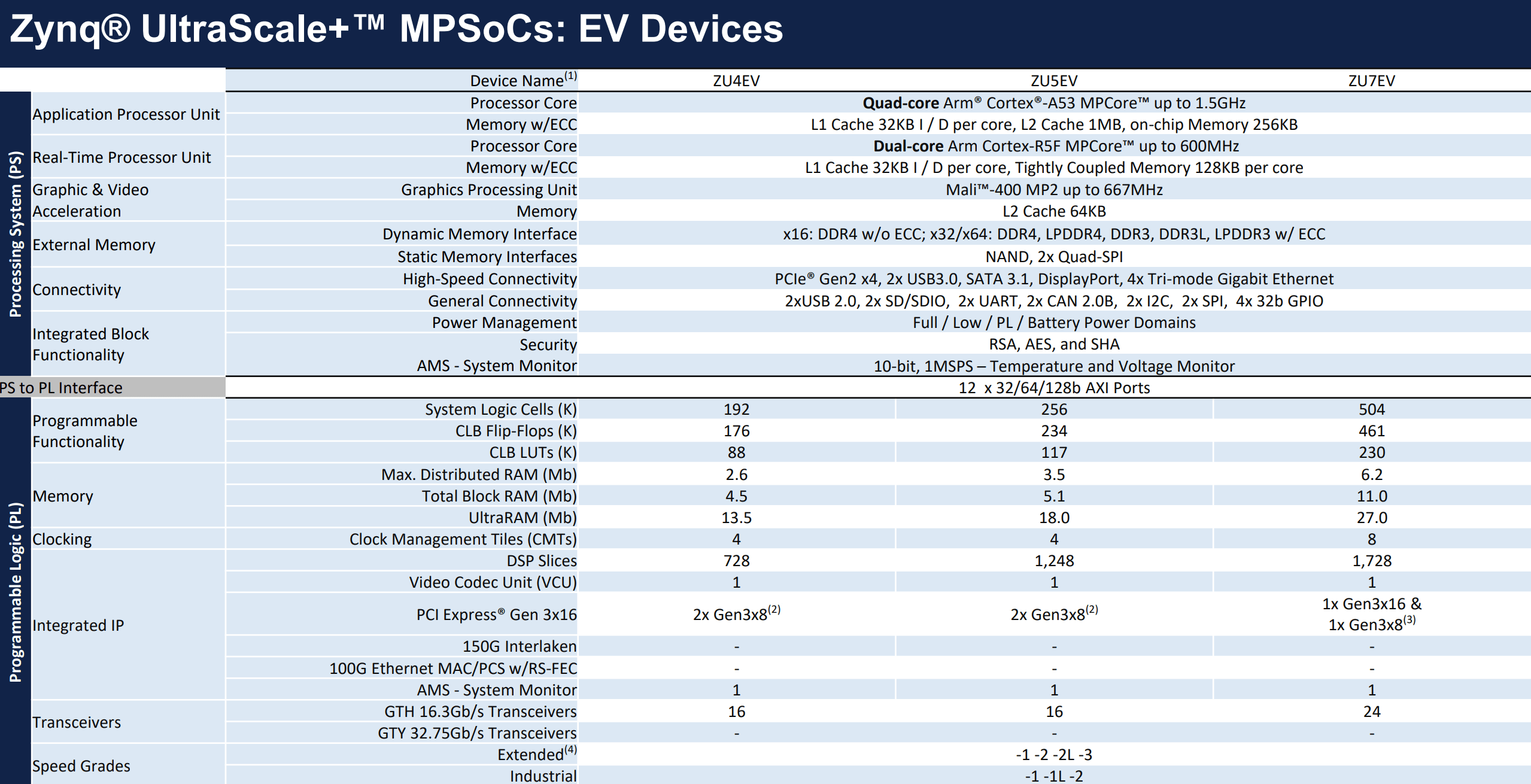

该系列的可编程逻辑部分采用了更加先进的 16nm FinFET+ 工艺制造,提供了更加丰富的可编程逻辑资源,CG、EG 和 EV 系列的详细参数如下,其中 EV 系列集成的 H.264/H.265 编码核心功能非常强大

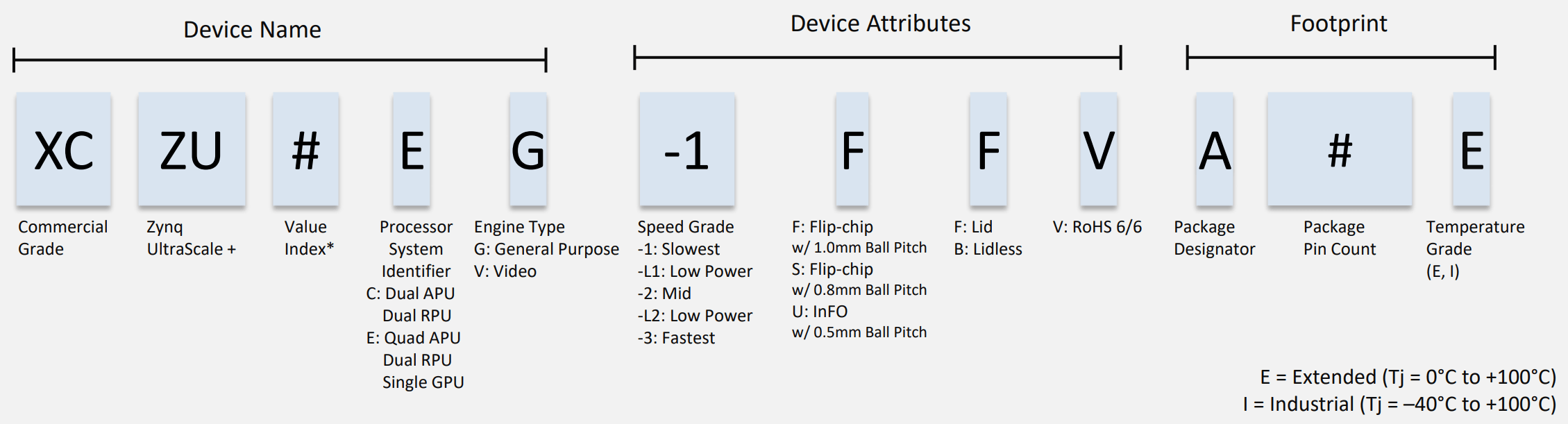

UltraScale + MPSoC 系列的产品命名规则如下

以上数据来源于 Xilinx 产品手册

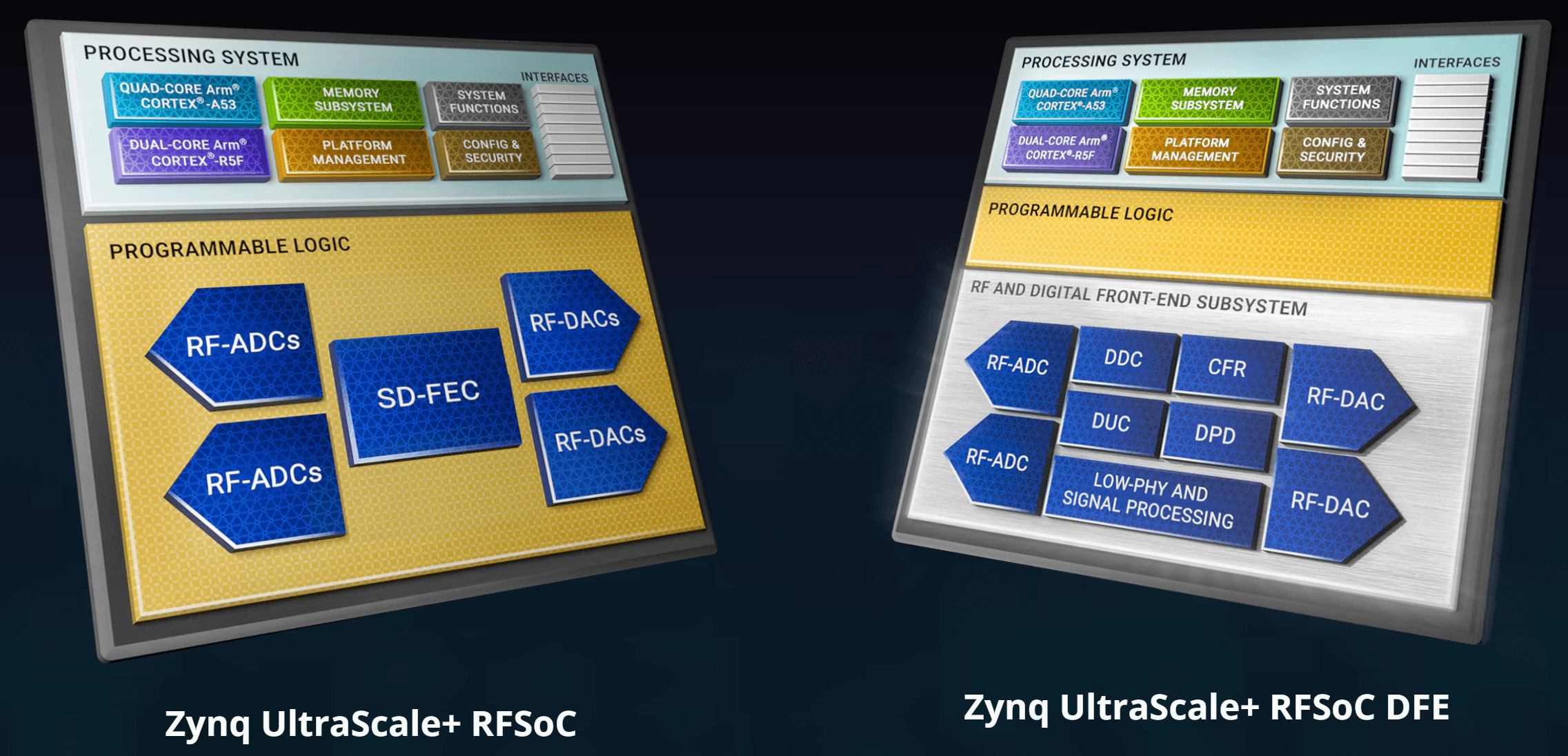

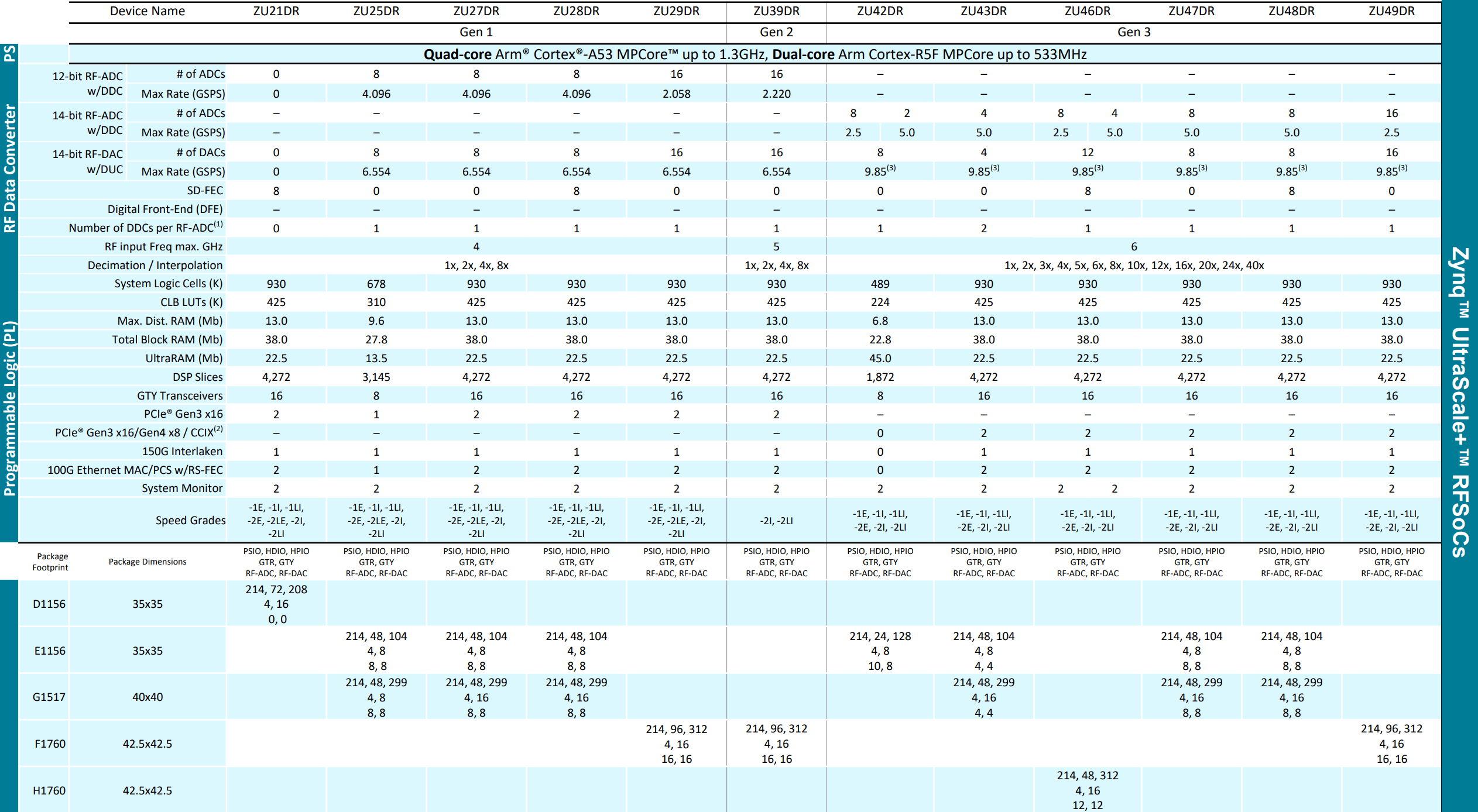

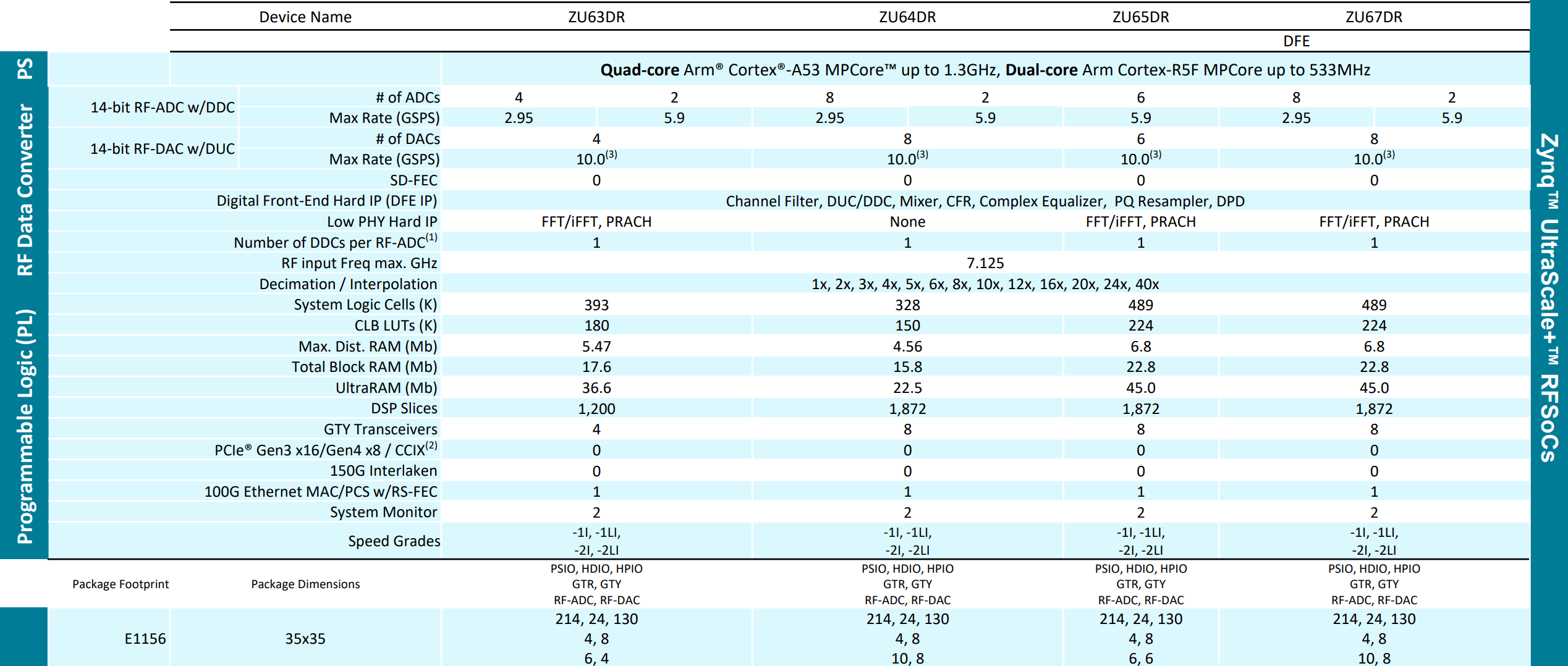

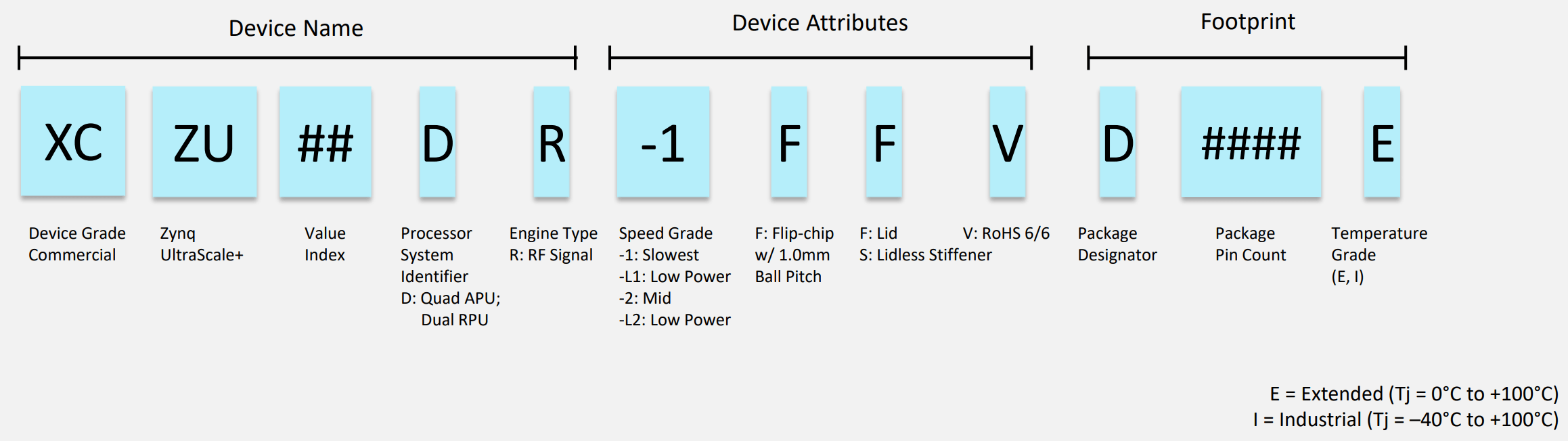

Zynq UltraScale+ RFSoC

UltraScale+ RFSoC 系列集成了高速 ADC、DAC 和 SD-FEC、DDC 等信号处理单元,在射频信号处理、高速通信等领域应用广泛

由于笔者对 RFSoC 系列了解较少,这里仅给出该系列产品性能参数,感兴趣的朋友可前往 官网 查看详细信息

该系列产品命名规则如下

以上数据来源于 Xilinx 产品手册

Versal™ Adaptive SoC

Versal 系列是 Xilinx 产品线中的划时代设计,其采用先进的 7nm 工艺制造,按照产品研发时间可分为 Gen1 和 Gen2 两部分

第二代产品的标量计算能力大约是第一代的 10 倍

由于笔者对 Versal 系列的了解几乎为 0,因此大家感兴趣的还是自行前往 首页 了解吧 [doeg]

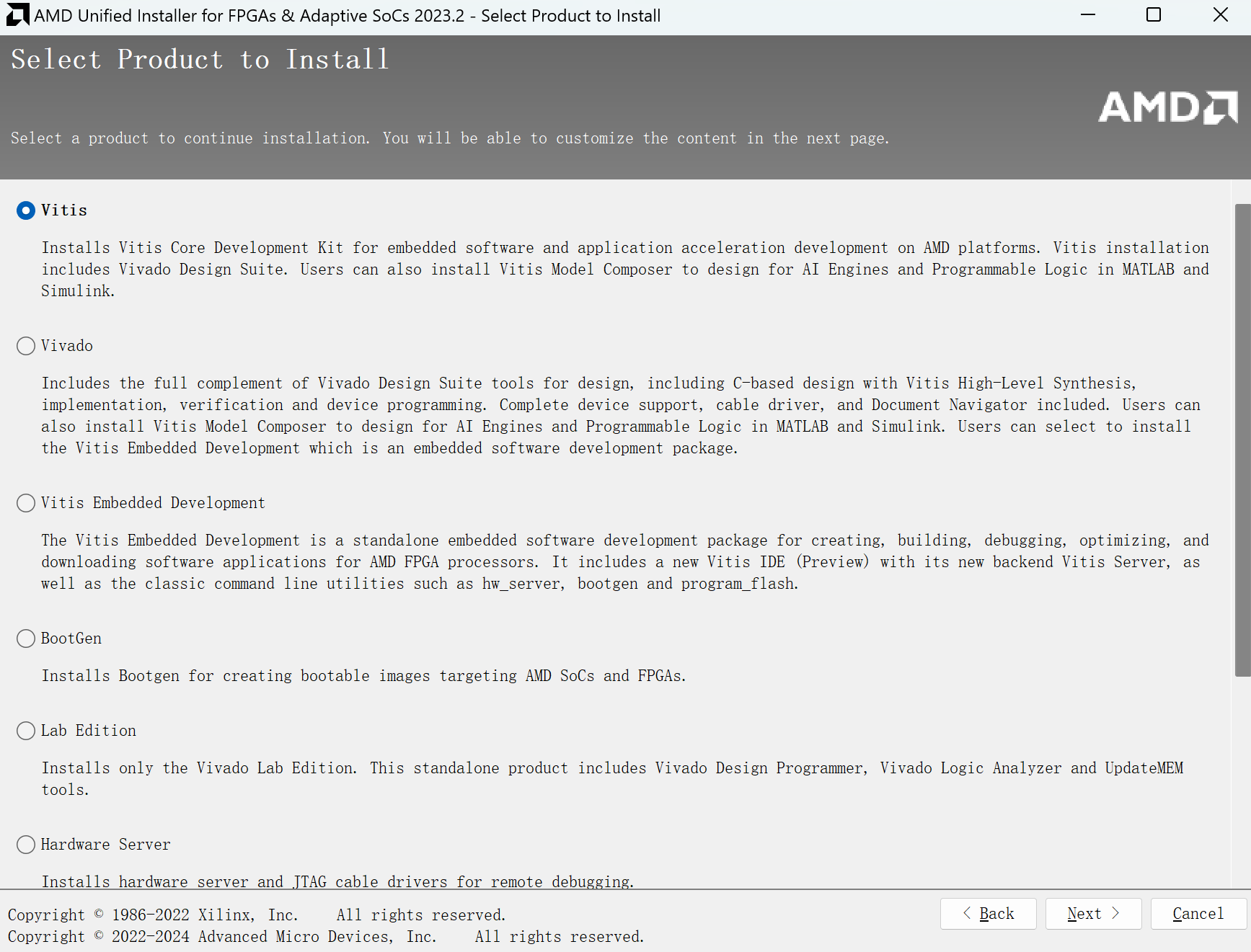

开发环境

Zynq 开发可分为 PS 端和 PL 端,PL 端使用 Vivado 开发,PS 端使用 Vitis 开发,安装时勾选 Vitis 会同时安装 Vivado

Vitis 是 SDK 的升级版本,两者关于 PS 端的开发流程和 API 基本没有变化,但仍然推荐安装 Vitis。其中 2023.1 及之前版本的 SDK / Vitis 基于 Eclipse 开发,2023.2 及之后的版本基于 VSC 开发,外观更加现代

通过上面的产品线介绍大家可以感受到,Zynq 系列包含的产品非常复杂,想要完全讲透各种外设、GPU、VPU 和 AI 加速单元等非常费时费力。因此,本系列笔记的大致路线如下

- 项目搭建流程和联合调试技巧

- PS 端基础外设,如 MIO、I2C、SPI、UART 等

- PL 端拓展外设,如 EMIO、AXI-GPIO、AXI-I2C、BRAM、AXI4-Stream FIFO

- AXI 总线协议,包括 AXI4-Lite、AXI4-Full 和 AXI4-Stream

- PS 与 PL 数据交互,如 BRAM、FIFO、DDR 等

- VPU……

授人以鱼不如授人以渔,Xilinx 官方提供了许多资料帮助我们学习 Zynq

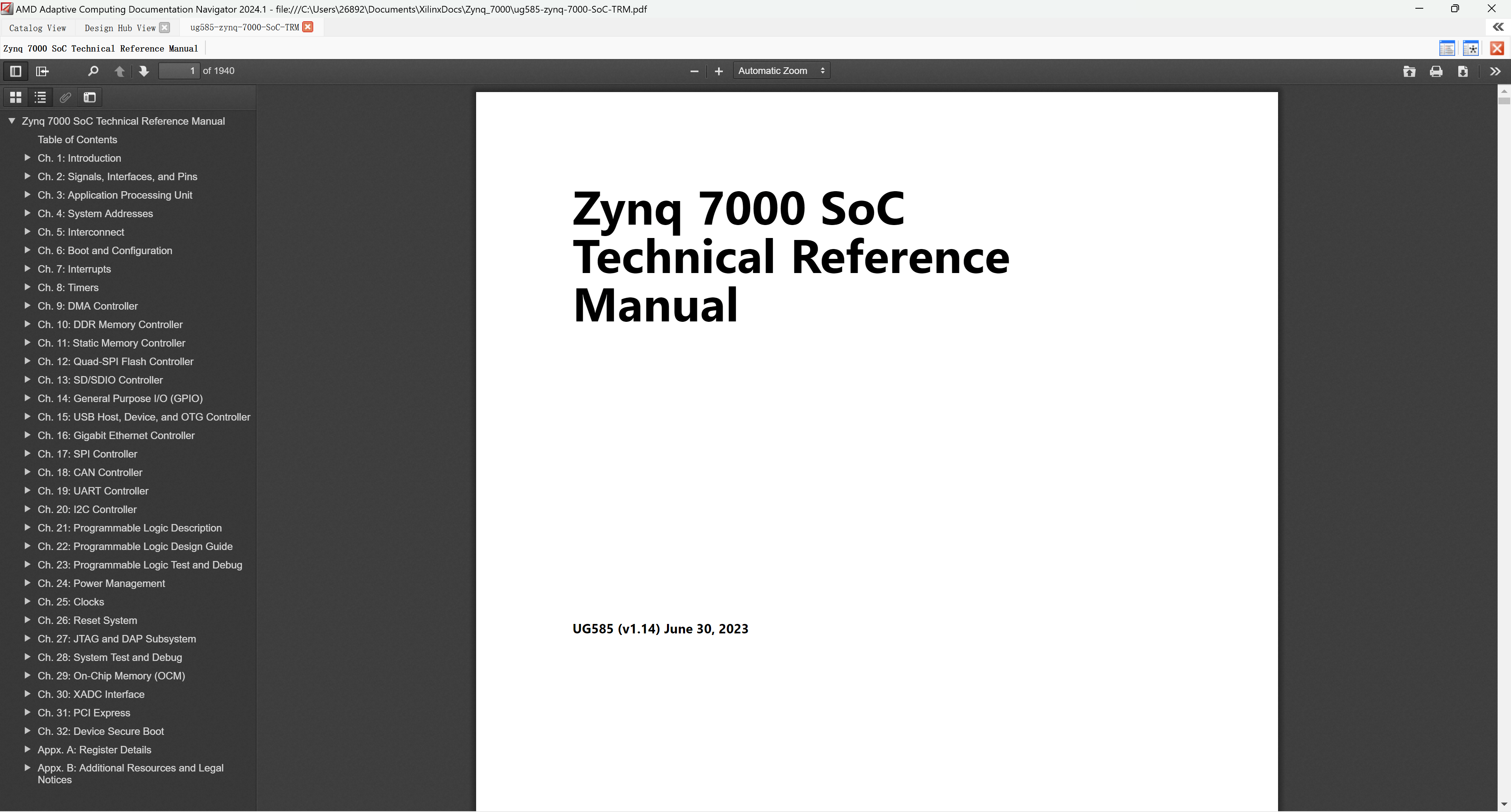

-

安装 Vitis 时一般会附带安装 DocNav 文档浏览器,可以在里面搜索关于 Zynq 相关的文档,里面对 Zynq 及其外设的内部结构、寄存器、基本使用有非常详细的介绍

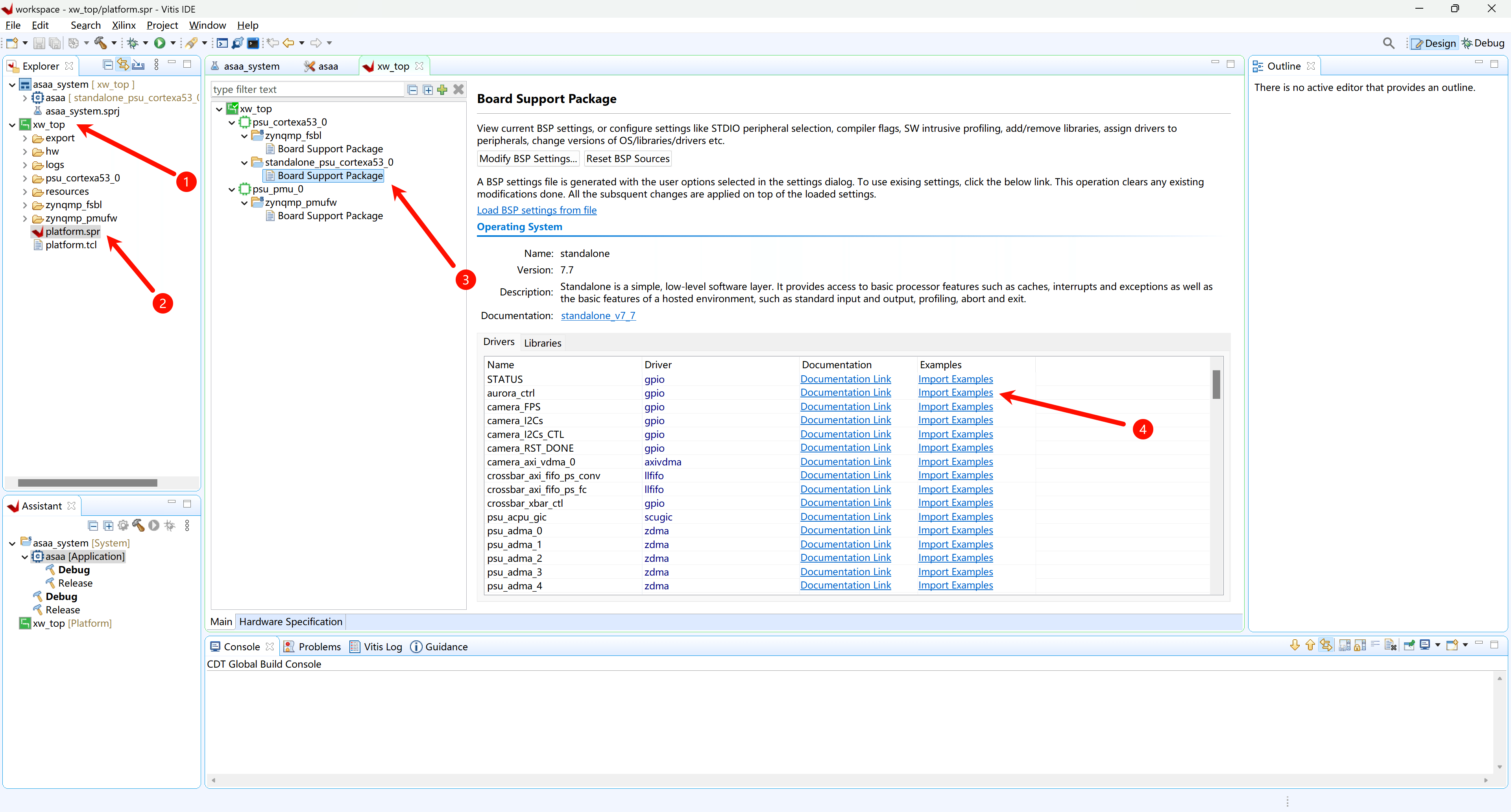

-

在 Vitis 中点击 Platform Project 下的 xpr 文件,然后点击 Board Support Package,在下面的 Drivers 栏就有当前 xsa 文件包含的相关外设的例程

-

米联客、黑金、正点原子等有很多例程可以参考学习,这里 是笔者收集的板卡资料,仅供学习使用

不积跬步,无以至千里。不积小流,无以成江河。

2438

2438

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?