第4关:全相联cache设计

(下载免费)

链接:https://pan.baidu.com/s/1gFwqQ0dQaN6boQ_lDv6avA

提取码:iah3

实验目的

学生掌握 cache 实现的三个关键技术:数据查找,地址映射,替换算法,熟悉译码器,多路选择器,寄存器的使用,能根据不同的映射策略在 Logisim 平台中用数字逻辑电路实现 cache 机制。

实验内容

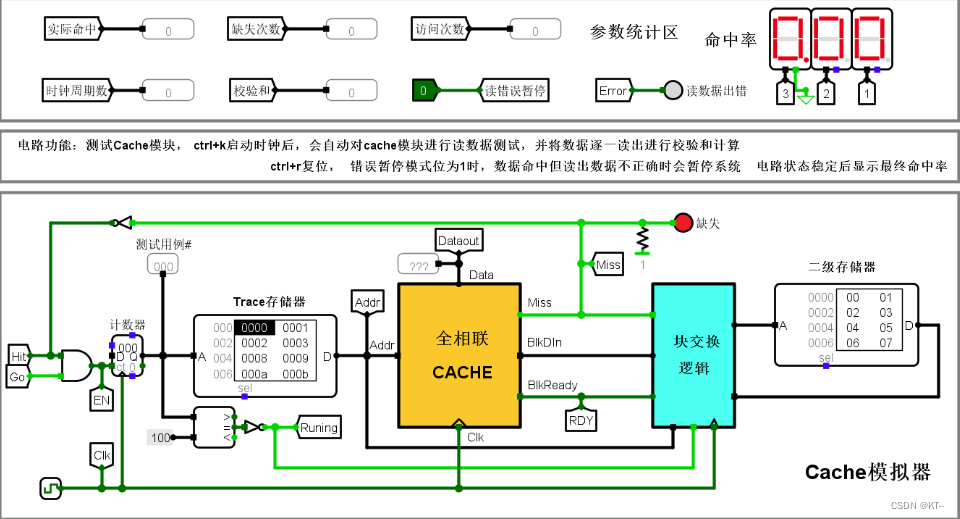

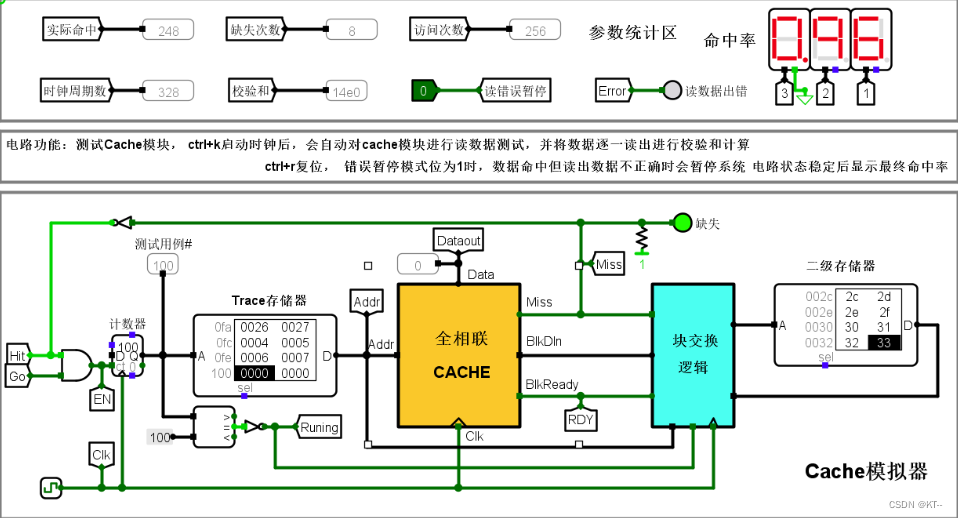

上图给出了一个在 Logisim 中设计完成的 cache 系统自动测试电路,为简化实验设计,这里所有 cache 模块均为只读 cache(类似指令 cache),无写入机制。电路左侧计数器与存储器部分会在时钟驱动下逐一生成地址访问序列给 cache 模块。计数器模块的使能端受命中信号驱动,缺失时使能端无效,计数器不计数,等待系统将待请求数据所在块从二级存储器中调度到 cache 后才能继续计数。cache 与二级存储器之间通过块交换逻辑实现数据块交换,由于二级存储器相比 cache 慢很多,所以一次块交换需要多个时钟周期才能完成,cache 模块判断数据块准备好的逻辑是 blkready 信号有效,该信号有效且时钟到来时,cache 将块数据从 BlkDin 端口一次性载入到对应cache 行缓冲区中,此时 cache 数据命中,直接输出请求数据,解锁计数器使能端,继续访问下一个地址。 自动测试电路会逐一取出 trace 存储器中的主存地址去访问存储系统,并逐一将数据从 cache 模块取出送校验和计算电路计算校验和,计数器值为256时会停止电路运行,此时所有存储访问的 cache 命中率将会在右上角 LED 数码管显示。本次实验的主要任务就是设计该电路的核心模块 cache 子电路。 结合引脚功能说明,实现全相联 cache 模块,该 cache 模块共包括8个 cache 行,每个数据块包含包括4个字节共32位数据。

电路框架

storage.circ

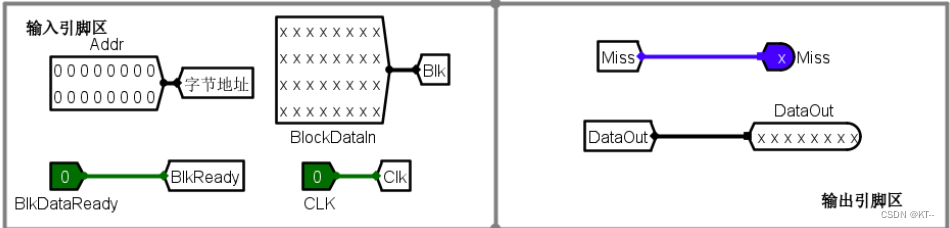

电路引脚

常见问题

标准输出中访问第2块应该命中,结果实际系统没有命中,调度二级存储器进行了块交换,所以访问第2块有3次输出,分别是缺失,blkok,命中三行,这个故障说明调度算法有问题,把不应该淘汰的数据淘汰出去了。

电路测试

完成设计后可以在 cache 自动测试电路中进行测试,正确结果如下:

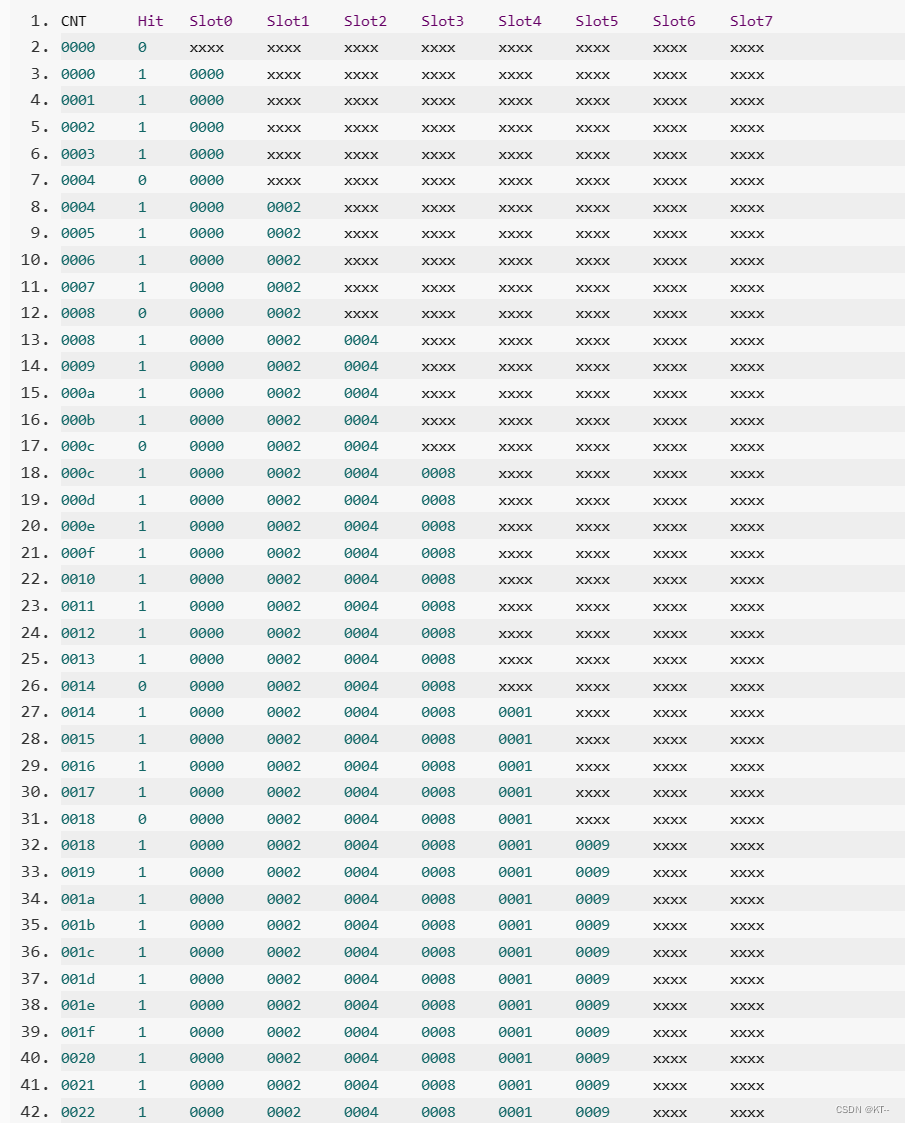

确认实验完成正确后可利用文本编辑工具打开 storage.circ,将所有文字信息复制粘贴到 Educoder平台的 storage.circ 文件中,再点击评测按钮即可进行本关测试,平台会对你设计的电路进行自动测试,为方便测试,请勿修改子电路封装,本关测试用例如下:

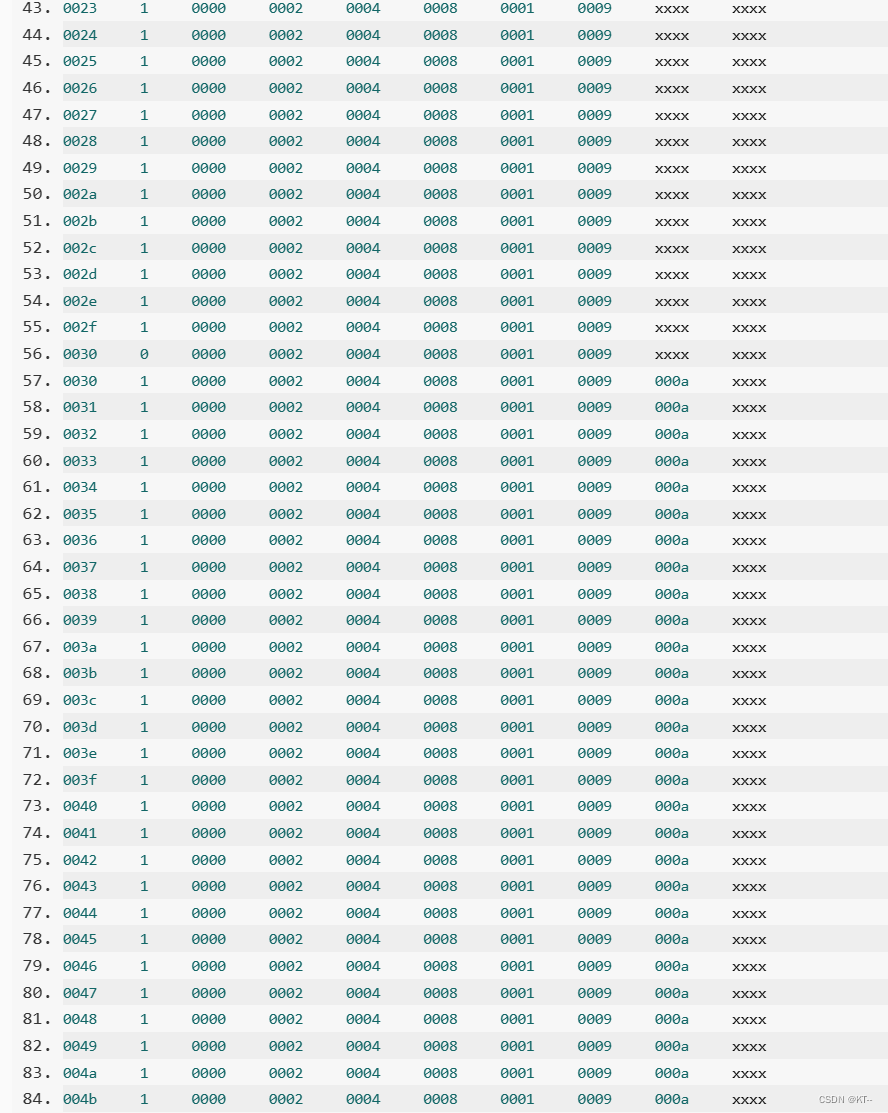

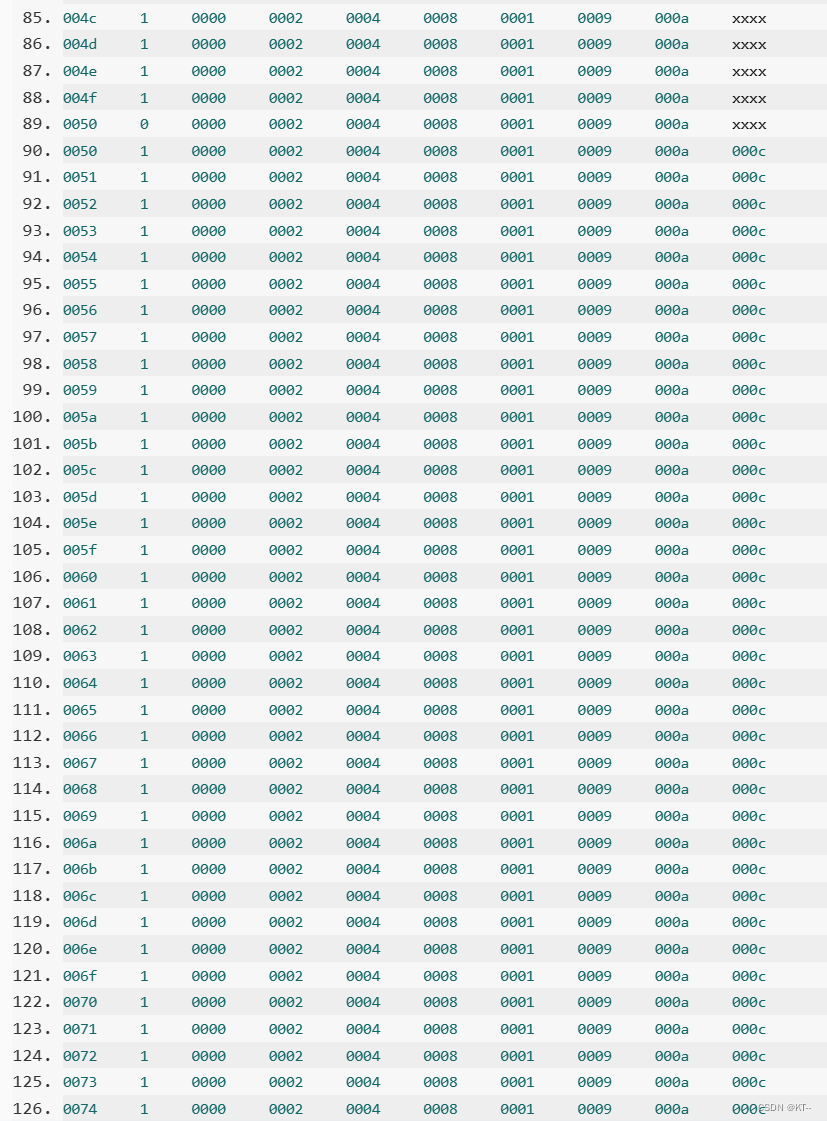

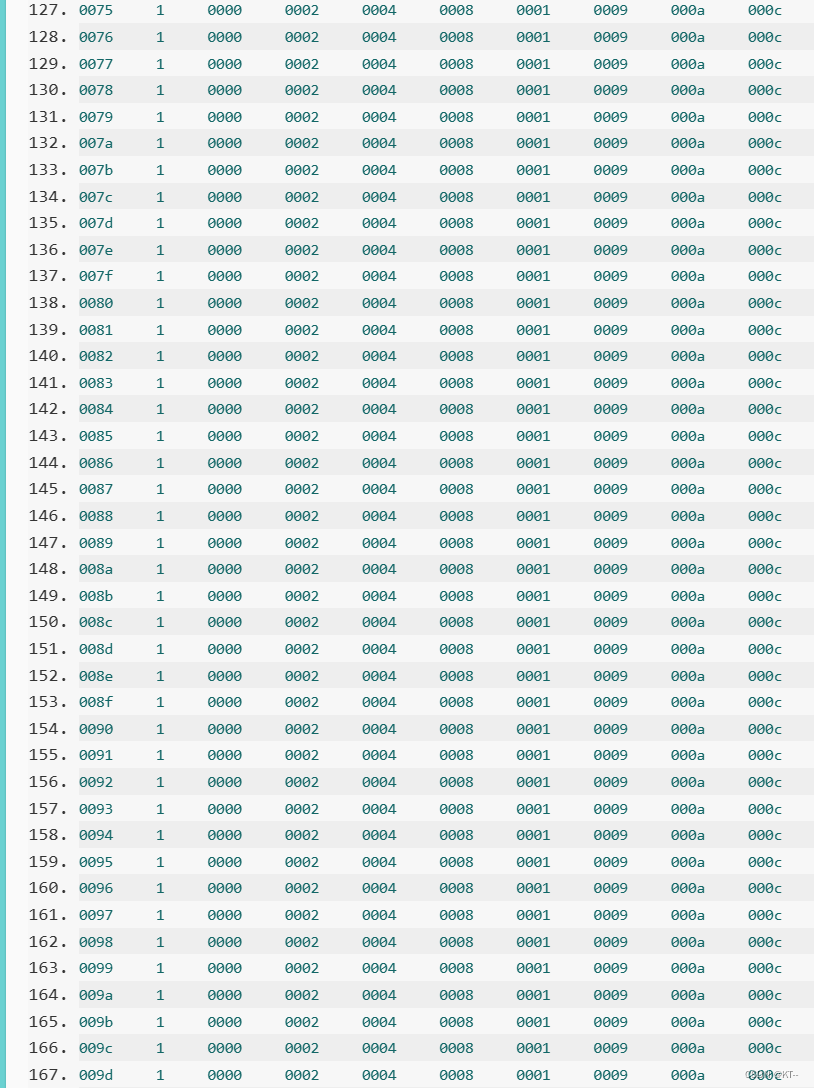

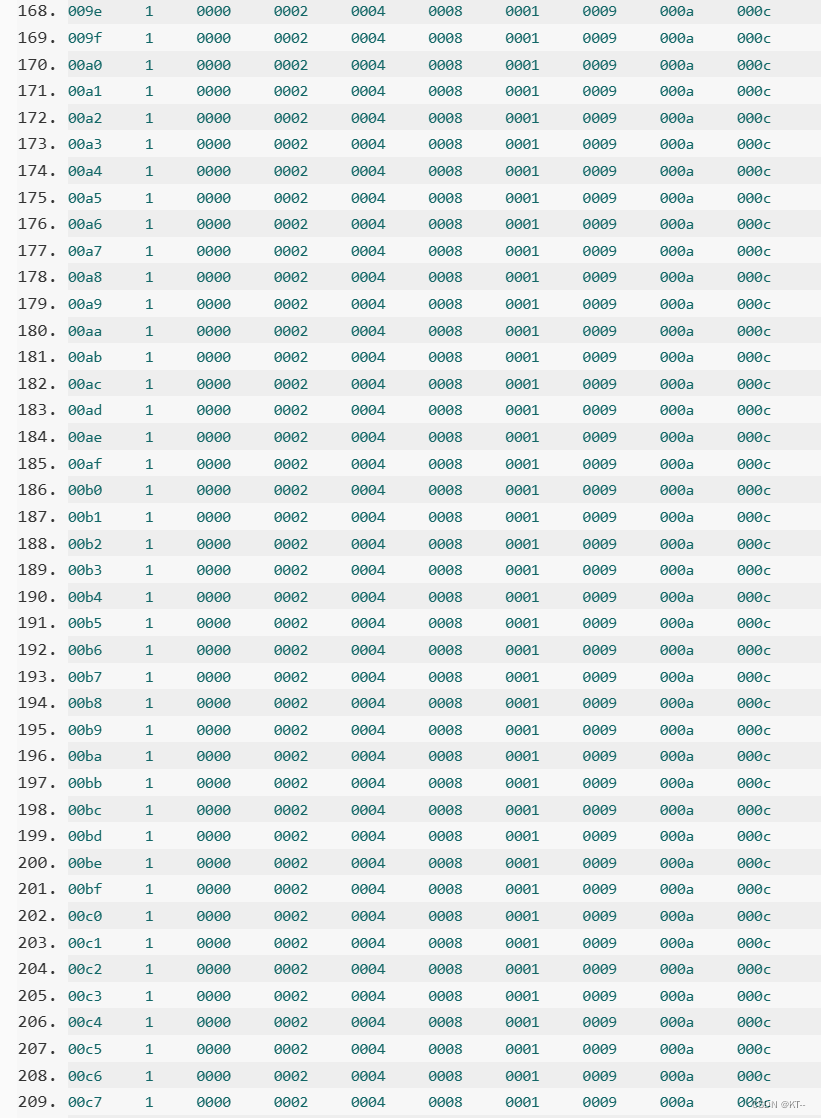

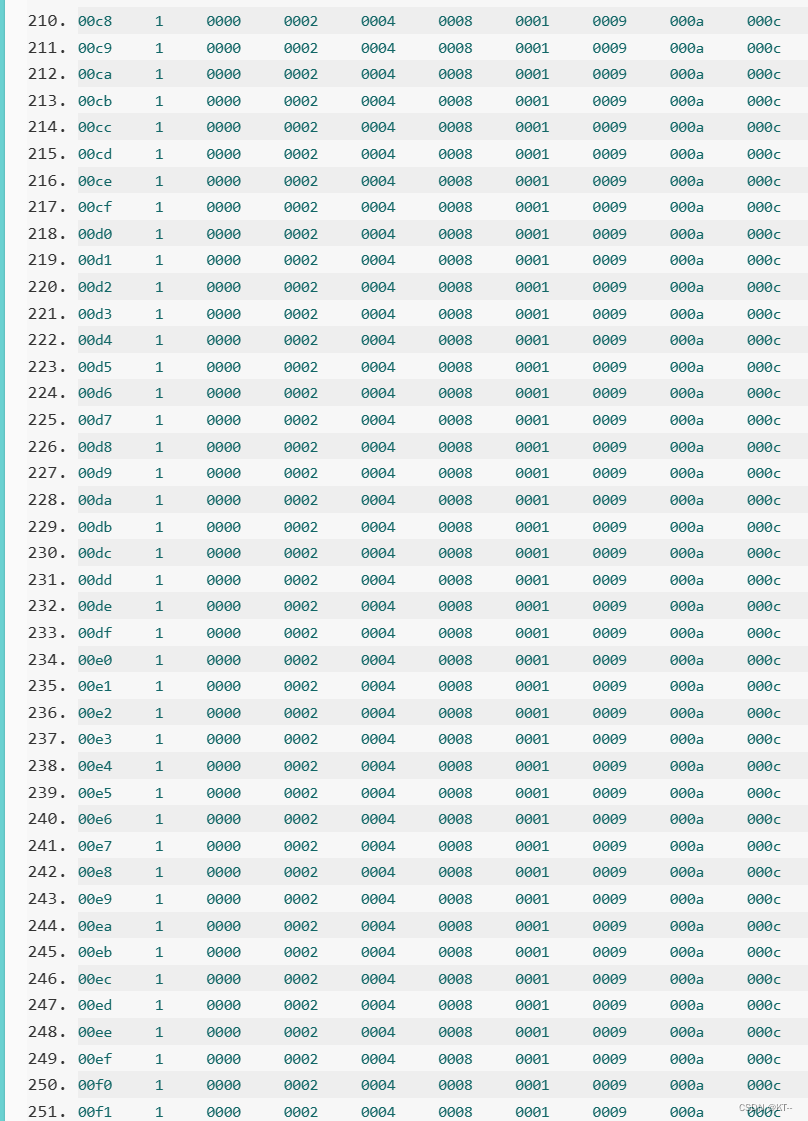

(这里 CNT 位第几次访问,下面第0次访问经历了3个状态,地址位0,缺失,等待从二级存储器载入数据,blkok 信号为 1,载入后,Hit 为1,见前3行)

清零中的毛刺问题解决:

清零动作改成同步清零,具体可以增加一个D触发器,将清零信号接输入,输出接异步清零,另外D触发器时钟触发方式请修改为上跳沿。

每个节拍对应各cache slot中的数据块如下,出现问题,可以参考

链接:https://pan.baidu.com/s/1gFwqQ0dQaN6boQ_lDv6avA

提取码:iah3

7900

7900

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?