第3关:MIPS RAM设计

(下载免费)

百度网盘

链接:https://pan.baidu.com/s/1fIhC-Kn1Uw8I1ZqrNJuEbA

提取码:38oq

实验目的

学生理解主存地址基本概念,理解存储位扩展基本思想,并能利用相关原理构建能同时支持字节、半字、字访问的存储子系统。

实验内容

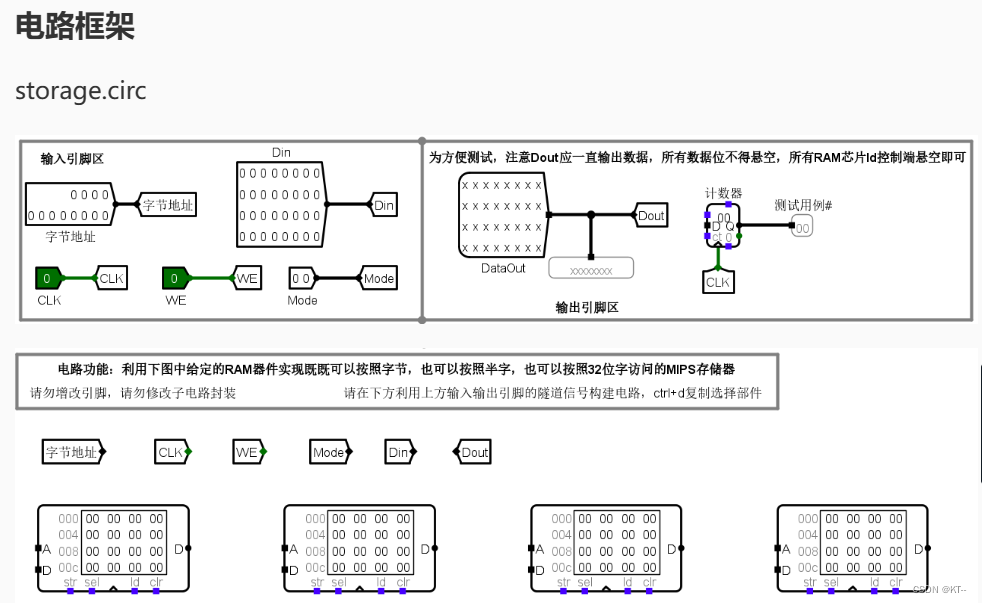

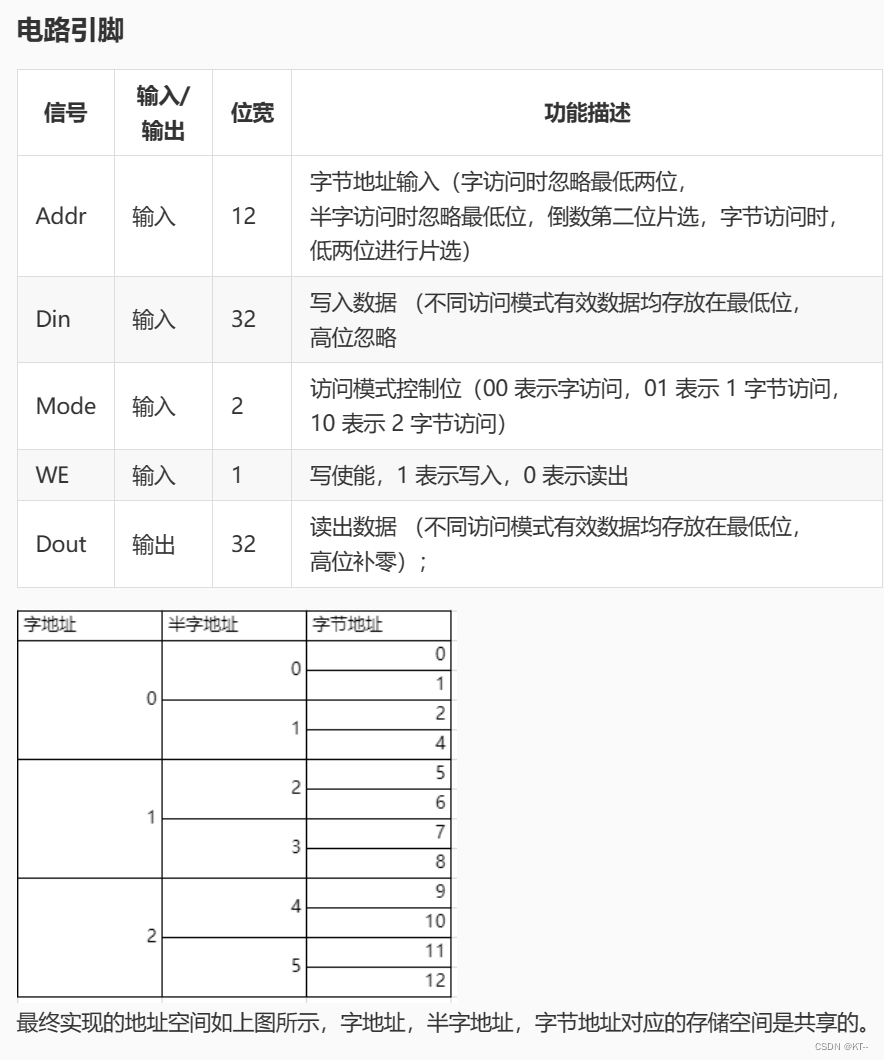

Logisim 中 RAM 组件只能提供固定的地址位宽,数据输出也只能提供固定的数据位宽,访问时无法同时支持字节/半字/字三种访问模式,实验要求利用4个8位的 RAM 组件进行扩展,设计完成既能按照8位、也能按16位、也能按照32位进行读写访问的32位存储器,最终存储器引脚定义如下图。

电路测试

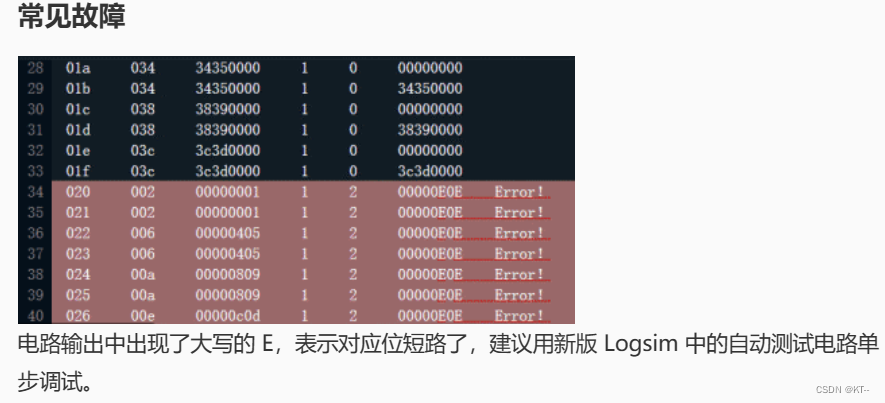

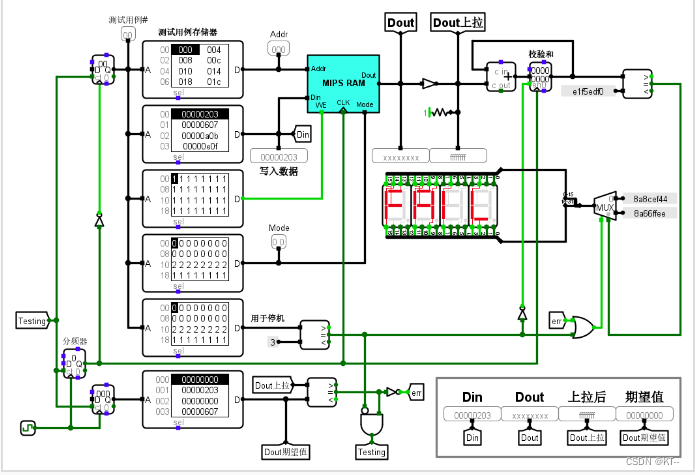

完成存储扩展设计后可以在自动测试电路中进行测试,电路通过会显示 Pass ,未能通过为停在出错位置,并显示 Fail ,如下图所示:

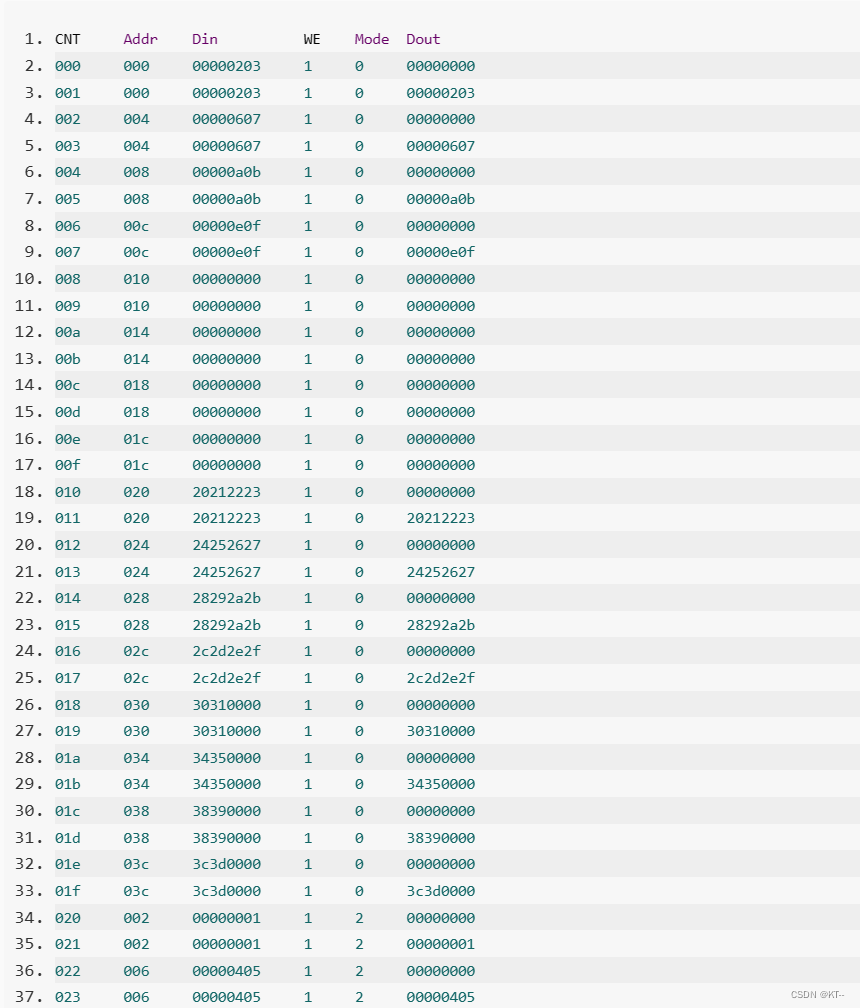

确认实验完成正确后可利用文本编辑工具打开 storage.circ ,将所有文字信息复制粘贴到 Educoder 平台的 storage.circ 文件中,再点击评测按钮即可进行本关测试,平台会对你设计的电路进行自动测试,为方便测试,请勿修改子电路封装,本关测试用例如下:

(以下省略)

百度网盘

链接:https://pan.baidu.com/s/1fIhC-Kn1Uw8I1ZqrNJuEbA

提取码:38oq

1001

1001

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?