第1关:MIPS指令译码器设计

✨创作不易,还希望各位大佬支持一下

👍 点赞,你的认可是我创作的动力!

⭐️ 收藏,你的青睐是我努力的方向!

✏️ 评论,你的意见是我进步的财富!

链接:https://pan.baidu.com/s/1CJkWa8eTsZHYTLazOyQJ6Q

提取码:ckpk

实验目的

帮助学生理解指令译码的基本概念,能将32位MIPS指令字译码成不同的指令译码信号。

实验内容

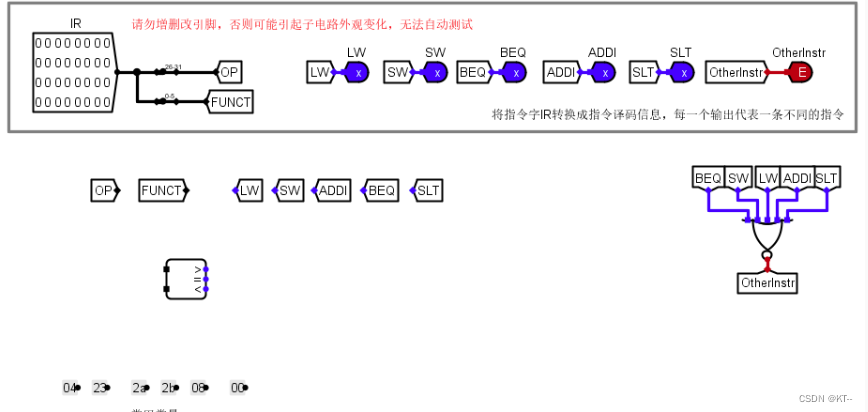

利用比较器等功能模块将32位MIPS 指令字译码生成LW、SW、BEQ、SLT、ADDI、OtherInstr信号:

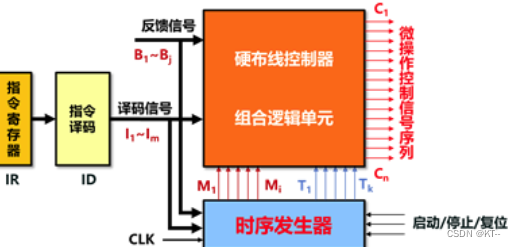

指令译码器是控制器核心功能部件,负责将指令字翻译成一根根的指令译码信号,每一根指令译码信号代表一条具体的指令,如上图中的I1...Im。

电路引脚

子电路外观如下:

电路框架

MipsOnBusCpu-1.circ ◇指令译码器 子电路

注意:可以整体平移引脚框到电路任何位置,但由于电路封装与引脚位置和顺序有关系,所以框内引脚一律不许增删改,哪怕是移动位置调整顺序,改变引脚朝向,也不要在电路中增加额外的引脚,否则测试系统无法测试。

电路测试

完成设计后,可利用文本编辑工具打开 MipsOnBusCpu-1.circ,将所有文字信息复制粘贴到 Educoder 平台的代码框中,再点击评测按钮即可进行本关测试。平台会对你设计的电路进行自动测试,为方便测试,请勿修改子电路封装。

测试输出结果说明

最终输出包括个检测引脚的期望值和实际值,出错时请对比查错。

| # | 信号 | 功能描述 |

|---|---|---|

| 1 | Cnt | 测试用例编号,注意是十六进制 |

| 2 | IR | 指令字IR的值 |

| 3 | LW | 1 |

| 4 | SW | 1 |

| 5 | BEQ | 1 |

| 6 | ADDI | 1 |

| 7 | SLT | 1 |

| 8 | OtherInstr | 1 |

调试技巧与常见故障

1、检查待测电路引脚框架是否和前面的图一致,调整引脚会引起待测部件封装接口改变,导致测试无法正常进行; 2、检查待测电路子电路外观也就是封装和前面的图是否一致,引脚位置,引脚顺序、引脚数目等,这个不一样肯定不正常;

✨创作不易,还希望各位大佬支持一下

👍 点赞,你的认可是我创作的动力!

⭐️ 收藏,你的青睐是我努力的方向!

✏️ 评论,你的意见是我进步的财富!

链接:https://pan.baidu.com/s/1CJkWa8eTsZHYTLazOyQJ6Q

提取码:ckpk

2815

2815

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?