仿真

链接:https://pan.baidu.com/s/1P7HI5anbbGWum1ANJzGFCw

提取码:t2u3

一、实验目的

1、通过实验,能熟悉QUARTUS开发环境,能够掌握QUARTUS的原理图输入法设计电路,掌握使用相关仿真工具进行功能和时序仿真的方法;

2、通过实验,加深对全加器电路的理解,并能使用QUARTUS的原理图输入法完成全加器的设计,并能在QUARTUS中完成相关的仿真验证;

二、实验原理

1、半加器、全加器的功能表见教材相关章节;

2、使用QUARTUS的原理图输入法完成半加器、全加器的设计,并能在QUARTUS中完成相关的仿真验证;

三、实验设备和器材

电脑、QUARTUS集成开发环境。

四、实验内容和步骤

4.1 半加器

在QUARTUS器件库选择相关器件,完成下面实验内容;

1.写出1位半加器的功能表,设计出1位半加器的逻辑电路图(预习时自行完成);

2.在QUARTUS中使用原理图输入法,完成1位半加器电路的设计;

3. 在QUARTUS中完成对所设计1位半加器电路的功能仿真和时序仿真;

4.2 1位全加器

在QUARTUS器件库选择相关器件,完成下面实验内容;

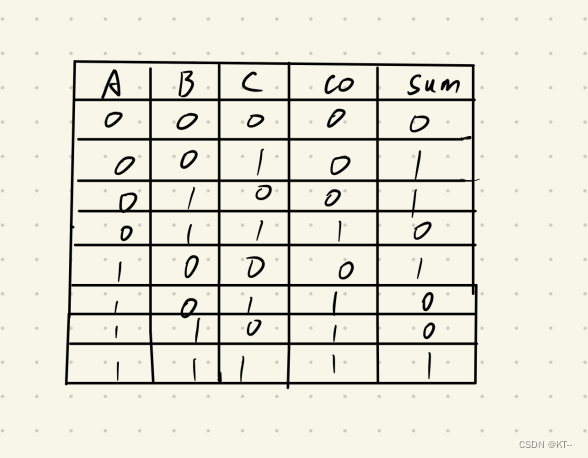

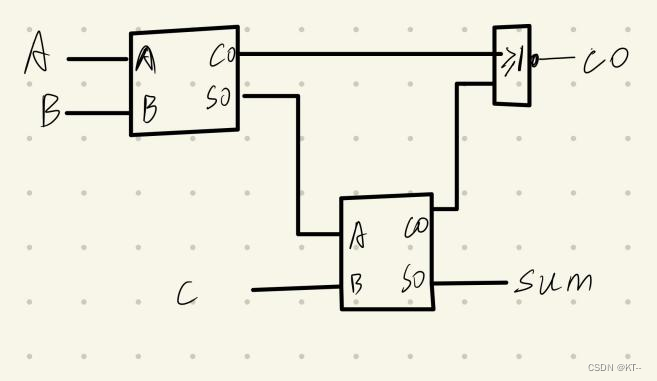

1.写出1位全加器的功能表,设计出1位全加器的逻辑电路图,要求使用4.1所设计的半加器实现(预习时自行完成);

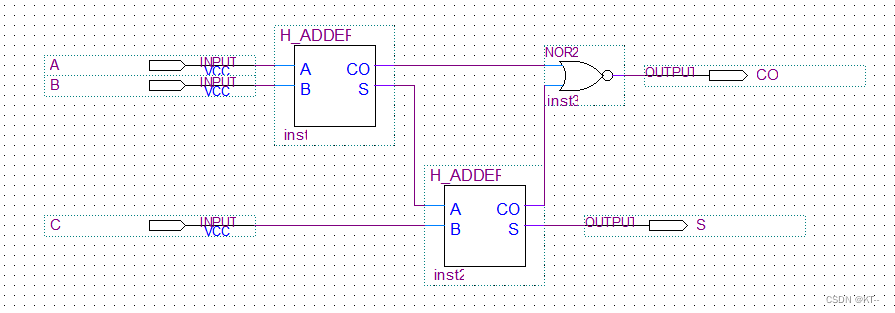

2.在QUARTUS中使用原理图输入法,完成1位全加器电路的设计;

3. 在QUARTUS中完成对所设计1位全加器电路的功能仿真和时序仿真;

4.3 4位全加器

在QUARTUS器件库选择相关器件,完成下面实验内容;

1.写出4位全加器的功能表,设计出4位全加器的逻辑电路图,要求使用4.2所设计的半加器实现(预习时自行完成);

2.在QUARTUS中使用原理图输入法,完成4位全加器电路的设计;

3. 在QUARTUS中完成对所设计4位全加器电路的功能仿真和时序仿真;

五、实验记录和实验结果

5.1 半加器

-

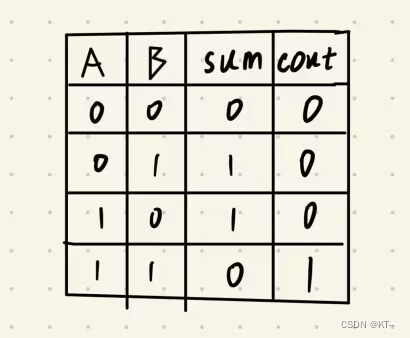

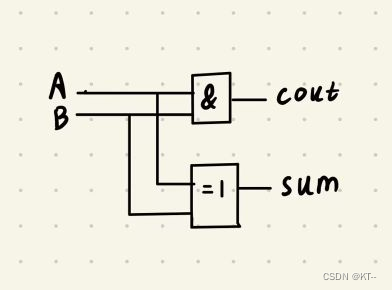

- 给出1位半加器的功能表,并给出设计出的1位半加器(请预习时完成)

-

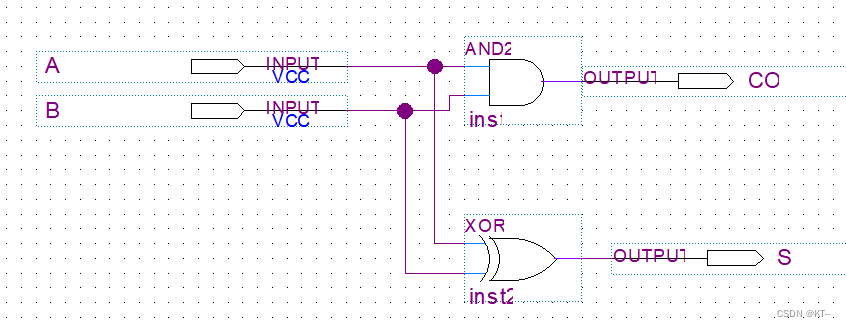

- 给出QUARTUS中使用原理图输入法实现1位半加器设计过程及电路

-

- 在所设计电路基础上,设计合理的输入信号,实现对所设计电路的功能仿真和时序仿真,要求简要说明仿真和验证思路,记录验证电路和输入信号,仿真结果及结论

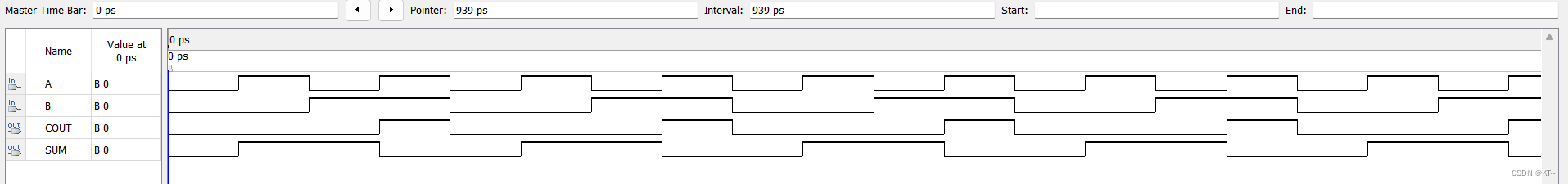

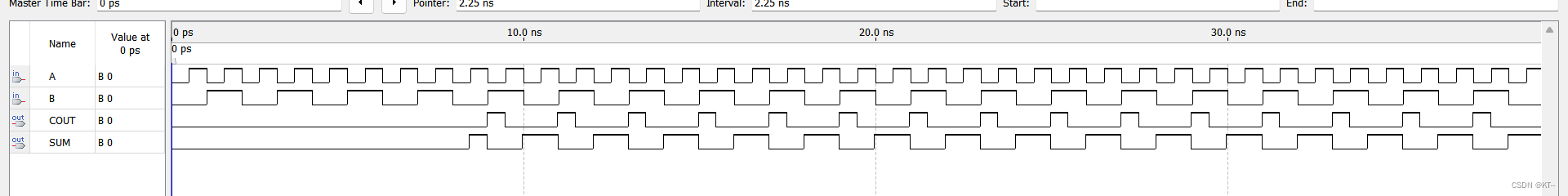

功能仿真:

思路:当两输入相同时,sum=0,相异时,sum=1,仅当两输入全为1时,cout=1,其他情况,cout=0。

仿真结果与功能表一致,故仿真成功。

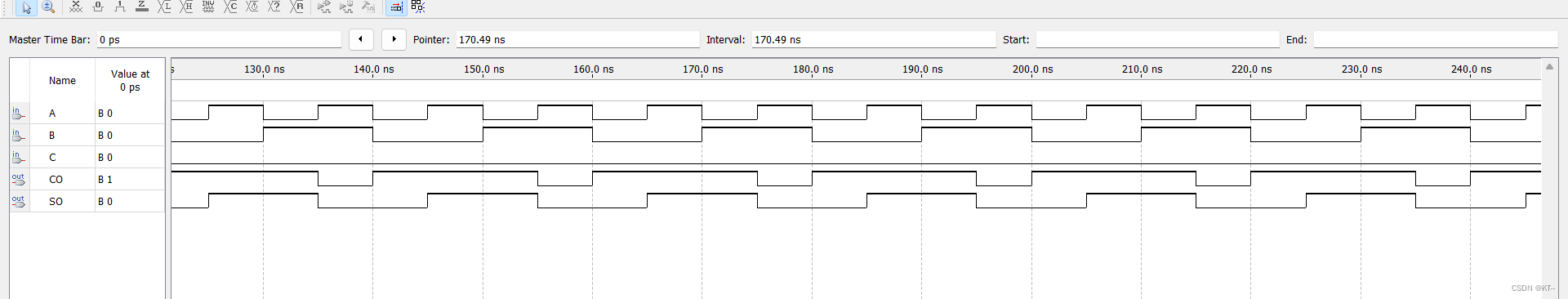

时序仿真:

仿真结果一致,仿真成功。

5.2 1位全加器

- 给出1位全加器的功能表,并给出设计出的1位全加器,要求使用前面设计的半加器(请预习时完成)

- 给出QUARTUS中使用原理图输入法实现1位全加器设计过程及电路

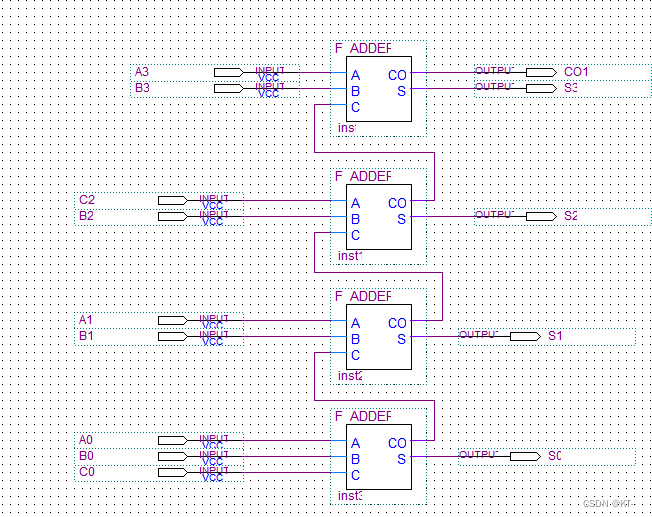

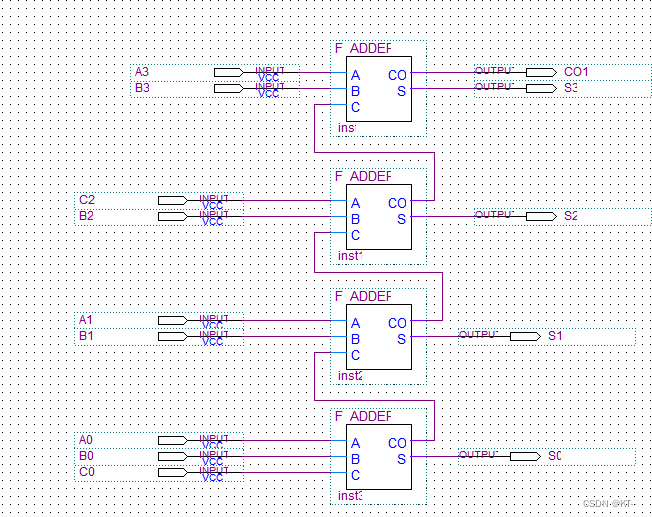

设计过程:调用两个半加器,给第一个半加器输入两个值A、B,将其SO和进位输入C接到第二个半加器上,将其SO作为直接的sum输出,将两个半加器的进位输出接到一个或非门上,作为CO输出。

- 在所设计电路基础上,设计合理的输入信号,实现对所设计电路的功能仿真和时序仿真,要求简要说明仿真和验证思路,记录验证电路和输入信号,仿真结果及结论

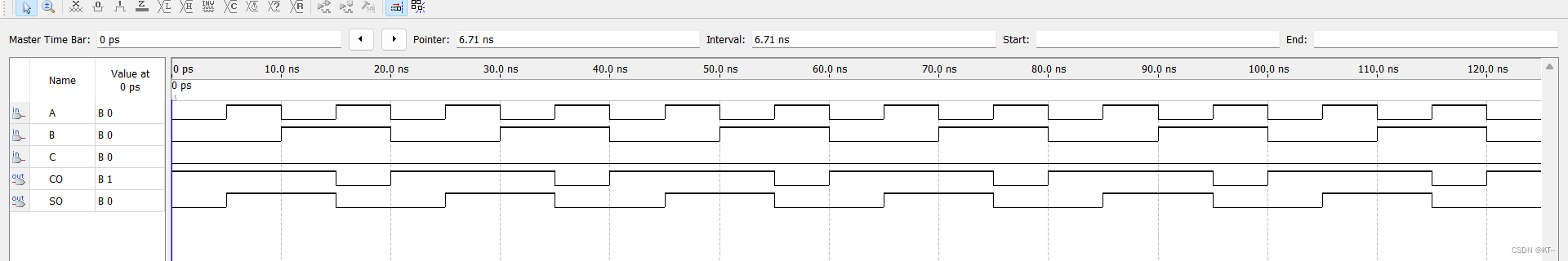

功能仿真:

时序仿真:

5.3 4位全加器

- 给出4位全加器的功能表,并给出设计出的4位全加器,要求使用前面设计的半加器(请预习时完成)

| 四位全加器功能表 | |||||||||||||

| CO | B0 | A0 | A1 | B1 | A2 | B2 | A3 | B3 | S0 | S1 | S2 | S3 | CC |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

- 给出QUARTUS中使用原理图输入法实现4位全加器设计过程及电路

设计过程:

1、新建工程,选择合适的芯片型号和仿真软件。

2、创建原理图文件,利用已建立的半加器和一位全加器模型,设计实现4位全加器并绘制电路图。

3、编译工程,生成逻辑网表和器件配置文件。

4、创建波形文件,定义输入信号的变化和输出信号的期望值。

5、进行功能仿真和时序仿真,观察输出信号是否符合预期。

- 在所设计电路基础上,设计合理的输入信号,实现对所设计电路的功能仿真和时序仿真,要求简要说明仿真和验证思路,记录验证电路和输入信号,仿真结果及结论

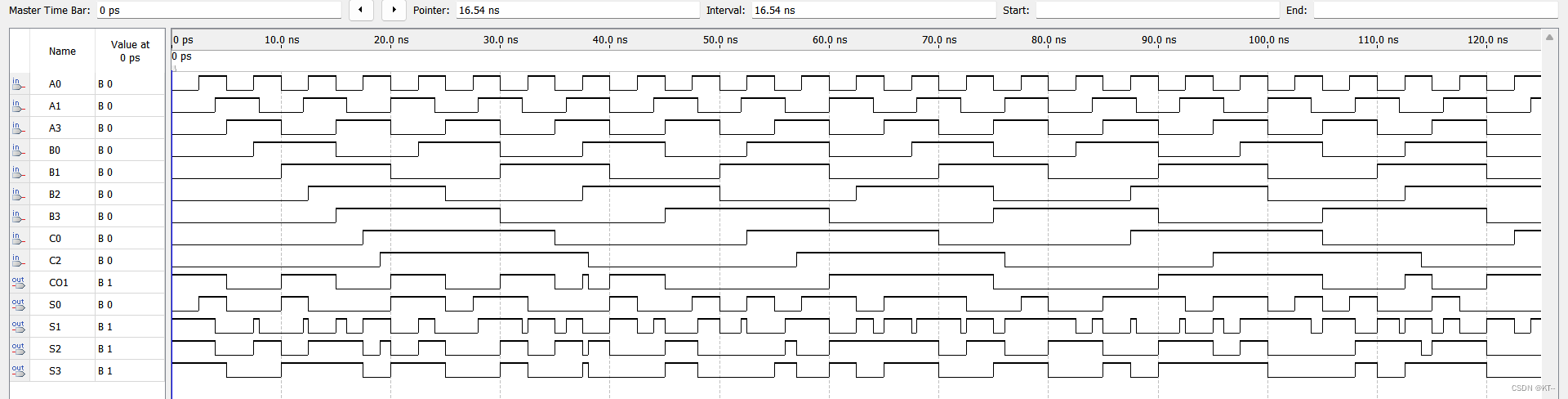

功能仿真:

使用波形编辑器,给输入信号设置激励,观察输出信号是否符合预期,检查电路的功能正确性。观察输出信号的实际表现,验证电路的实际功能和性能,在误差允许范围内与真值表及所需功能是否一致。

仿真结果与

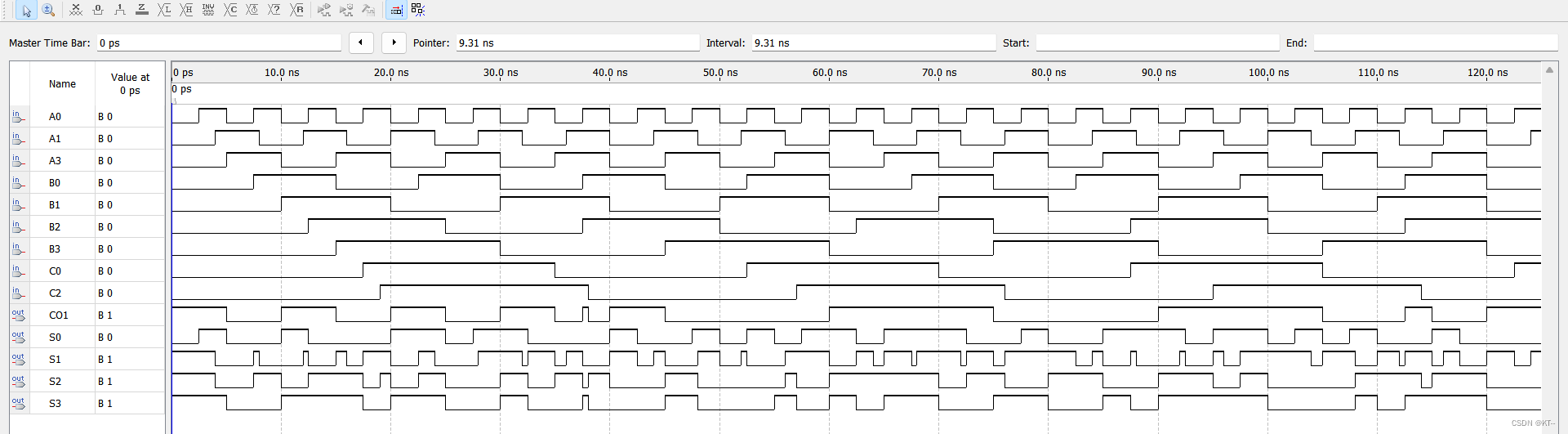

时序仿真:

六、实验预习要求

- 实验前认真阅读本实验指导;

- 熟悉quartus中相关操作及相关器件。

- 完成四和五中要求预习时完成的内容。

七、思考题

1、在quartus完成对组合逻辑电路设计、功能仿真及验证的有哪些?

1、创建一个一位半加器的工程,用原理图方式绘制半加器的电路,编译并仿真。

617

617

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?