用VHDL设计一个计数范围为0-9999的4位十进制计数器建路CNTg可简化设计并便于显示,该计数器分为两个层次,底层电路包括四个十进制计模块CNT10,再由这四个模块共按照图1所示的原理图构成顶层电路CNI999。其中底层和顶层由路均采用VHDI文本输入。

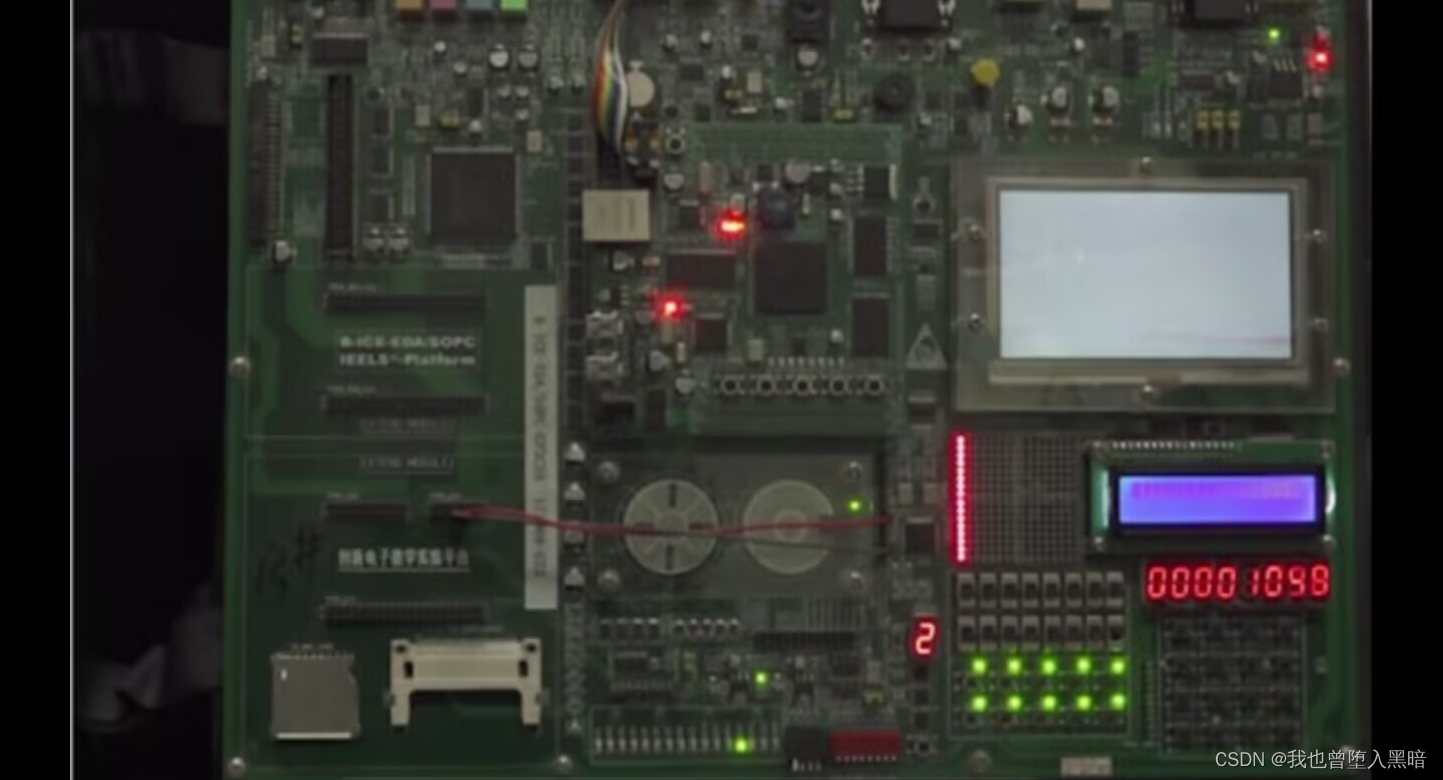

为了简化设计并便于显示,该计数动态扫描显示电路分为两个层次,底层电路包括四个十进制计数器模块CNT10、动态显示控制信号产生模块CTRLS数据动态显示控制模块PISPLAY 等六个模块,再由这六个模块按照图2所示的原理图构成顶层电路DTCNT9999

其中,底层的六个模块用VHDL文本输入,顶层的电路系统则采用原理图输入。DTCNT9999中的CLK1是计数时钟信号:CLK2是动态扫描控制时钟信号,要求在24Hz以上;CLR为清零信号:ENA为计数时钟信号;COM为数码管公共端控制信号;SEG为数码管的显示驱动端,分别接a~g。

1)CNT10的VHDL源程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT10 IS

PORT(CLK:IN STD_LOGIC;

CLR:IN STD_LOGIC;

ENA:IN STD_LOGIC;

CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CO:OUT STD_LOGIC);

END ENTITY CNT10;

ARCHITECTURE ART OF CNT10 IS

SIGNAL CQI:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(CLK,CLR,ENA) IS

BEGIN

IF CLR='1' THEN CQI<="0000";

ELSIF CLK'EVENT AND CLK='1' THEN

IF ENA='1' THEN

IF CQI="1001" THEN

CQI<="0000";

ELSE

CQI<=CQI+'1';

END IF;

END IF;

END IF;

END PROCESS;

PROCESS(CLK,CQI) IS

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF CQI<"1001" THEN

CO<='0';

ELSE

CO<='1';

END IF;

END IF;

END PROCESS;

CQ<=CQI;

END ARCHITECTURE ART;

2)CNT9999的VHDL源程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CNT9999 IS

PORT(CLK1:IN STD_LOGIC;

CLR:IN STD_LOGIC;

ENA:IN STD_LOGIC;

DOUT:OUT STD_LOGIC_VECTOR(15 DOWNTO 0));

END ENTITY CNT9999;

ARCHITECTURE ART OF CNT9999 IS

COMPONENT CNT10 IS

PORT(CLK:IN STD_LOGIC;

CLR:IN STD_LOGIC;

ENA:IN STD_LOGIC;

CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CO:OUT STD_LOGIC);

END COMPONENT CNT10;

SIGNAL S1,S2,S3:STD_LOGIC;

BEGIN

U1:CNT10 PORT MAP(CLK1,CLR,ENA,DOUT(3 DOWNTO 0),S1);

U2:CNT10 PORT MAP(S1,CLR,ENA,DOUT(7 DOWNTO 4),S2);

U3:CNT10 PORT MAP(S2,CLR,ENA,DOUT(11 DOWNTO 8),S3);

U5:CNT10 PORT MAP(S3,CLR,ENA,DOUT(15 DOWNTO 12));

END ARCHITECTURE ART;

3)CTRLS的VHDL源程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CTRLS IS

PORT(CLK: IN STD_LOGIC;

SEL: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END ENTITY CTRLS;

ARCHITECTURE ART OF CTRLS IS

SIGNAL CNT: STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

PROCESS(CLK) IS

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF CNT="111" THEN

CNT<="000";

ELSE

CNT<=CNT+'1';

END IF ;

END IF;

END PROCESS;

SEL<=CNT;

END ARCHITECTURE ART;

- DISPLAY的VHDL源程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY DISPLAY IS

PORT(SEL: IN STD_LOGIC_VECTOR(2 DOWNTO 0);

DATAIN: IN STD_LOGIC_VECTOR(15 DOWNTO 0);

COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY DISPLAY;

ARCHITECTURE ART OF DISPLAY IS

SIGNAL DATA:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(SEL) IS

BEGIN

CASE SEL IS

WHEN "000" => COM<="11111110";

WHEN "001" => COM<="11111101";

WHEN "010" => COM<="11111011";

WHEN "011" => COM<="11110111";

WHEN "100" => COM<="11101111";

WHEN "101" => COM<="11011111";

WHEN "110" => COM<="10111111";

WHEN "111" => COM<="01111111";

WHEN OTHERS => COM<="11111111";

END CASE ;

END PROCESS;

PROCESS(SEL) IS

BEGIN

CASE SEL IS

WHEN "000" =>DATA<=DATAIN(3 DOWNTO 0);

WHEN "001" =>DATA<=DATAIN(7 DOWNTO 4);

WHEN "010" =>DATA<=DATAIN(11 DOWNTO 8);

WHEN "011" =>DATA<=DATAIN(15 DOWNTO 12);

WHEN OTHERS=>DATA<="0000";

END CASE;

CASE DATA IS

WHEN "0000" => SEG<="00111111";--3FH

WHEN "0001" => SEG<="00000110";--06H

WHEN "0010" => SEG<="01011011";--5BH

WHEN "0011" => SEG<="01001111";--4FH

WHEN "0100" => SEG<="01100110";--66H

WHEN "0101" => SEG<="01101101";--6DH

WHEN "0110" => SEG<="01111101";--7DH

WHEN "0111" => SEG<="00000111";--07H

WHEN "1000" => SEG<="01111111";--7FH

WHEN "1001" => SEG<="01101111";--6FH

WHEN OTHERS => SEG<="00000000";--00H

END CASE ;

END PROCESS;

END ARCHITECTURE ART;

- DTCNT9999的VHDL源程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DTCNT9999 IS

PORT(CLK1:IN STD_LOGIC;

CLR:IN STD_LOGIC;

ENA:IN STD_LOGIC;

CLK2:IN STD_LOGIC;

COM:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

SEG:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY DTCNT9999;

ARCHITECTURE ART OF DTCNT9999 IS

COMPONENT CNT10 IS

PORT(CLK:IN STD_LOGIC;

CLR:IN STD_LOGIC;

ENA:IN STD_LOGIC;

CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CO:OUT STD_LOGIC);

END COMPONENT CNT10;

COMPONENT CTRLS IS

PORT(CLK:IN STD_LOGIC;

SEL:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END COMPONENT CTRLS;

COMPONENT DISPLAY IS

PORT(SEL:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

DATAIN:IN STD_LOGIC_VECTOR(15 DOWNTO 0);

COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END COMPONENT DISPLAY;

SIGNAL S1,S2,S3,S4,S5:STD_LOGIC;

SIGNAL S:STD_LOGIC_VECTOR(2 DOWNTO 0);

SIGNAL DOUT:STD_LOGIC_VECTOR(15 DOWNTO 0);

BEGIN

U1:CNT10 PORT MAP(CLK1,CLR,ENA,DOUT(3 DOWNTO 0),S1);

U2:CNT10 PORT MAP(S1,CLR,ENA,DOUT(7 DOWNTO 4),S2);

U3:CNT10 PORT MAP(S2,CLR,ENA,DOUT(11 DOWNTO 8),S3);

U5:CNT10 PORT MAP(S3,CLR,ENA,DOUT(15 DOWNTO 12));

U10:CTRLS PORT MAP(CLK2,S(2 DOWNTO 0));

U11:DISPLAY PORT MAP(S,DOUT,COM,SEG);

END ARCHITECTURE ART;

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?