设计并调试好8位十进制数字频率计,并用GW48系列或其他EDA实验开发系统(事先应选定拟采用的实验芯片的型号)进行硬件验证

设计思路:数字频率计数器其实就是对数字秒表的进一步深入,其功能是测出某个频率的大小。

要测出某个频率的大小那就是设定一秒钟周期,周期内测试的频率的脉冲上升沿多少。

频率 =上升沿脉冲个数/T,当T等于1s时候,则频率=上升沿脉冲个数。

为了能够在数码管上显示依旧需要加CTRLS(动态扫描)和DISPLAY(动态显示),而1S的周期哪来的呢,这是可以设定由内部产生或者外部产生,这里我设置为内部产生,通过一个分配器的操作来达到输出的周期时间为1S。

为了能够测量多次频率,那么就需要对前面一次频率进行一个保存,当前面频率保存的时候,计数器不工作,并且给一个清零信号将前一次测频的结果清除。

cnt10 源程序

--CNT10.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT10 IS

PORT(CLK:IN STD_LOGIC;

CLR:IN STD_LOGIC;

ENA:IN STD_LOGIC;

CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CO:OUT STD_LOGIC);

END ENTITY CNT10;

ARCHITECTURE ART OF CNT10 IS

SIGNAL CQI:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(CLK,CLR,ENA) IS

BEGIN

IF CLR='1' THEN CQI<="0000";

ELSIF CLK'EVENT AND CLK='1' THEN

IF ENA='1' THEN

IF CQI="1001" THEN

CQI<="0000";

ELSE

CQI<=CQI+'1';

END IF;

END IF;

END IF;

END PROCESS;

PROCESS(CLK,CQI) IS

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF CQI<"1001" THEN

CO<='0';

ELSE

CO<='1';

END IF;

END IF;

END PROCESS;

CQ<=CQI;

END ARCHITECTURE ART;控制信号源代码

--TESCTL.VHD(控制信号)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY TESTCTL IS

--其中clk信号由分配器产生

PORT(CLK: IN STD_LOGIC;

TSTEN: OUT STD_LOGIC; --输出时钟信号,用于控制计数器

CLR_CNT: OUT STD_LOGIC; --清零信号,用于清除计数器数据

LOAD: OUT STD_LOGIC); --用于发送给寄存器用于存储数据,其中电平波形于TSTEN相反

END ENTITY TESTCTL;

ARCHITECTURE ART OF TESTCTL IS

SIGNAL DIV2CLK : STD_LOGIC; --2分频时钟信号

BEGIN

PROCESS(CLK) IS

BEGIN

IF CLK'EVENT AND CLK='1' THEN

DIV2CLK<= NOT DIV2CLK; --进行一个翻转

END IF;

END PROCESS;

PROCESS(CLK,DIV2CLK) IS

BEGIN

IF CLK='0'AND DIV2CLK='0' THEN

CLR_CNT<='1';

ELSE CLR_CNT <='0';

END IF;

END PROCESS;

LOAD<=NOT DIV2CLK;

TSTEN <= DIV2CLK;

END ARCHITECTURE ART;分频器源程序

--CLKGEN.VHD(分频器)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CLKGEN IS

PORT(CLK: IN STD_LOGIC;

NEWCLK: OUT STD_LOGIC);

END ENTITY CLKGEN;

ARCHITECTURE ART OF CLKGEN IS

--SIGNAL CNT: INTEGER RANGE 0 TO 10#49999999#;

SIGNAL CNT: INTEGER RANGE 0 TO 10#1#;

BEGIN

PROCESS(CLK) IS

BEGIN

IF CLK'EVENT AND CLK='1' THEN

--IF CNT=10#49999999# THEN CNT<=0;

IF CNT=10#1# THEN CNT<=0;

ELSE CNT<=CNT+1;

END IF;

END IF;

END PROCESS;

PROCESS(CNT) IS

BEGIN

--IF CNT=10#49999999# THEN NEWCLK<='1';

IF CNT=10#1# THEN NEWCLK<='1';

ELSE

NEWCLK<='0';

END IF;

END PROCESS;

END ARCHITECTURE ART;32位寄存器源程序

--REG32B.VHD(32位锁存器)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY REG32B IS

PORT(LOAD:IN STD_LOGIC; --为1时候代表锁存器工作

DIN:IN STD_LOGIC_VECTOR(31 DOWNTO 0); --DIN是计数结果

DOUT:OUT STD_LOGIC_VECTOR(31 DOWNTO 0));

END ENTITY REG32B;

ARCHITECTURE ART OF REG32B IS

BEGIN

PROCESS(LOAD,DIN)IS

BEGIN

IF(LOAD'EVENT AND LOAD='1')THEN

DOUT<=DIN;

END IF;

END PROCESS;

END ARCHITECTURE ART;

--DISPLAY.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY DISPLAY IS

PORT(SEL: IN STD_LOGIC_VECTOR(2 DOWNTO 0);

DATAIN: IN STD_LOGIC_VECTOR(31 DOWNTO 0);

COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY DISPLAY;

ARCHITECTURE ART OF DISPLAY IS

SIGNAL DATA:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(SEL) IS

BEGIN

CASE SEL IS

WHEN "000" => COM<="11111110";

WHEN "001" => COM<="11111101";

WHEN "010" => COM<="11111011";

WHEN "011" => COM<="11110111";

WHEN "100" => COM<="11101111";

WHEN "101" => COM<="11011111";

WHEN "110" => COM<="10111111";

WHEN "111" => COM<="01111111";

WHEN OTHERS => COM<="11111111";

END CASE ;

END PROCESS;

PROCESS(SEL) IS

BEGIN

CASE SEL IS

WHEN "000" =>DATA<=DATAIN(3 DOWNTO 0);

WHEN "001" =>DATA<=DATAIN(7 DOWNTO 4);

WHEN "010" =>DATA<=DATAIN(11 DOWNTO 8);

WHEN "011" =>DATA<=DATAIN(15 DOWNTO 12);

WHEN "100" =>DATA<=DATAIN(19 DOWNTO 16);

WHEN "101" =>DATA<=DATAIN(23 DOWNTO 20);

WHEN "110" =>DATA<=DATAIN(27 DOWNTO 24);

WHEN "111" =>DATA<=DATAIN(31 DOWNTO 28);

WHEN OTHERS=>DATA<="0000";

END CASE;

CASE DATA IS

WHEN "0000" => SEG<="00111111";--3FH

WHEN "0001" => SEG<="00000110";--06H

WHEN "0010" => SEG<="01011011";--5BH

WHEN "0011" => SEG<="01001111";--4FH

WHEN "0100" => SEG<="01100110";--66H

WHEN "0101" => SEG<="01101101";--6DH

WHEN "0110" => SEG<="01111101";--7DH

WHEN "0111" => SEG<="00000111";--07H

WHEN "1000" => SEG<="01111111";--7FH

WHEN "1001" => SEG<="01101111";--6FH

WHEN OTHERS => SEG<="00000000";--00H

END CASE ;

END PROCESS;

END ARCHITECTURE ART;

--CTRLS.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CTRLS IS

PORT(CLK: IN STD_LOGIC;

SEL: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END ENTITY CTRLS;

ARCHITECTURE ART OF CTRLS IS

SIGNAL CNT: STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

PROCESS(CLK) IS

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF CNT="111" THEN

CNT<="000";

ELSE

CNT<=CNT+'1';

END IF ;

END IF;

END PROCESS;

SEL<=CNT;

END ARCHITECTURE ART;

RTL视图

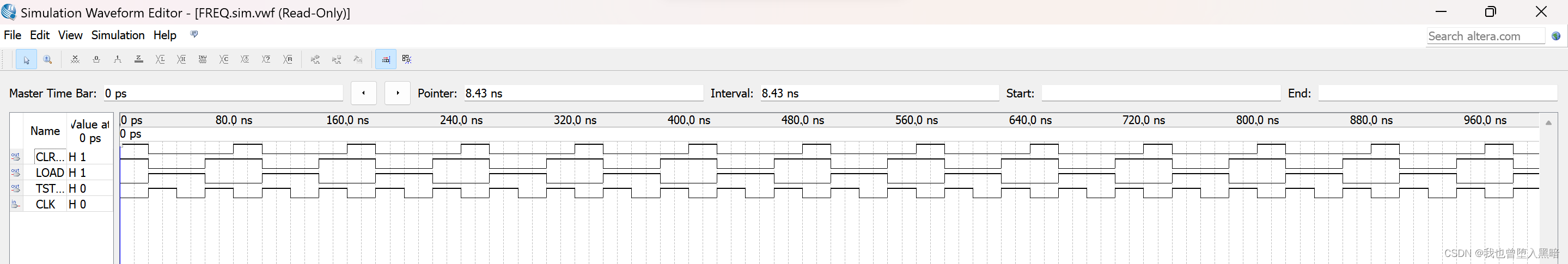

TESTCL波形仿真

FREQ波形仿真

2476

2476

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?