数据选择器概述

数据选择:指经过选择,将多路数据中的某一路数据传到公共数据线上。(相当于多个输入的单刀多掷开关)

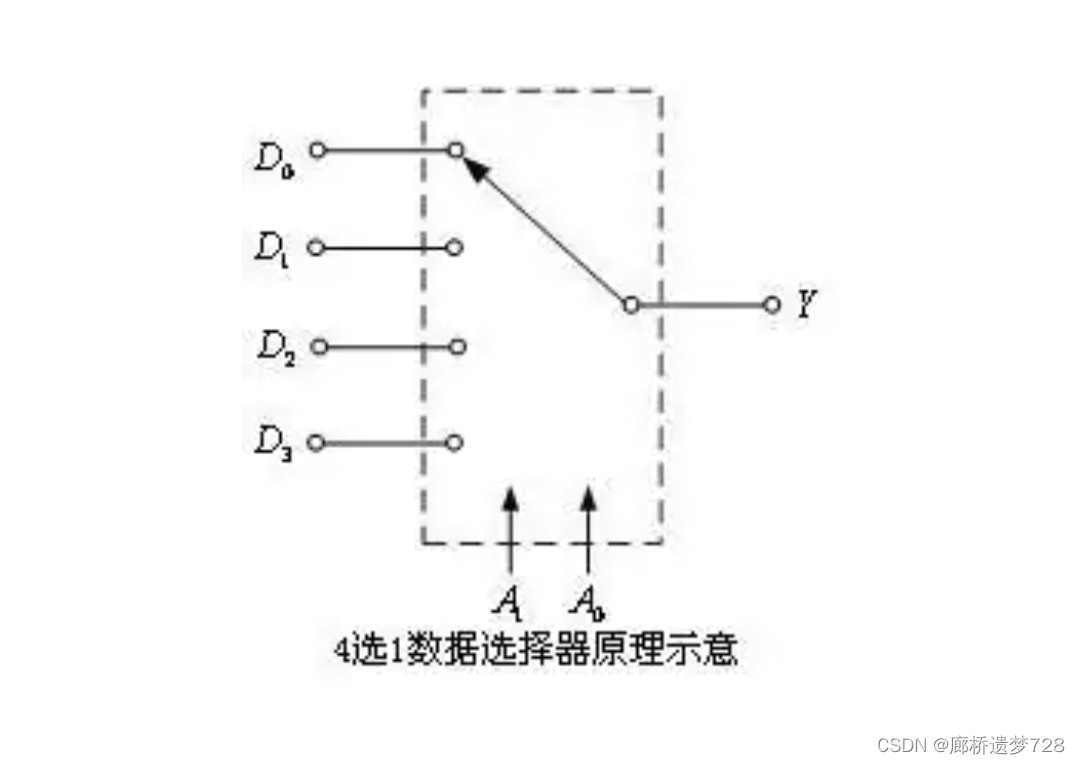

数据选择器:能实现数据选择功能的逻辑电路。也称多路选择器或多路开关。如下图为4选1数据选择器:

对于4选1数据选择器,最常见的芯片为74LS153,其内部有两个4选1数据选择器。

工作原理:给A1、A0一组信号,比如10,就相当于给了一个二进制数字2,也就相当于选通了D2这个输入端,此时Y输出的就是D2的信号;D2是什么,Y就输出什么。

真值表:

| 地址输入 | 输出 | |

| A1 | A0 | Y |

| 0 | 0 | D0 |

| 0 | 1 | D1 |

| 1 | 0 | D2 |

| 1 | ||

本文介绍了数据选择器的工作原理,如4选1和8选1数据选择器,及其在FPGA和移位运算中的应用。通过逻辑函数展开和香农定理,展示了如何用数据选择器实现特定逻辑功能,如L=AC+BC。

本文介绍了数据选择器的工作原理,如4选1和8选1数据选择器,及其在FPGA和移位运算中的应用。通过逻辑函数展开和香农定理,展示了如何用数据选择器实现特定逻辑功能,如L=AC+BC。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

875

875

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?