译码器概述

译码器(Decoder)的逻辑功能是将每个输人的二进制代码译成对应的输出高、低电平信号或另外一个代码或一个脉冲。因此,译码是编码的逆过程。

译码器的种类很多,但它们的工作原理和分析设计方法大同小异,其中二进制译码器、二-十进制译码器和显示译码器是三种最典型,使用十分广泛的译码电路。

二进制译码器(最小项译码器)

将输入的n位二进制代码对应成2^n个不同输出端。在译码器工作时,无论输入什么,有且只有一个输出端电平与其他输出端不同。

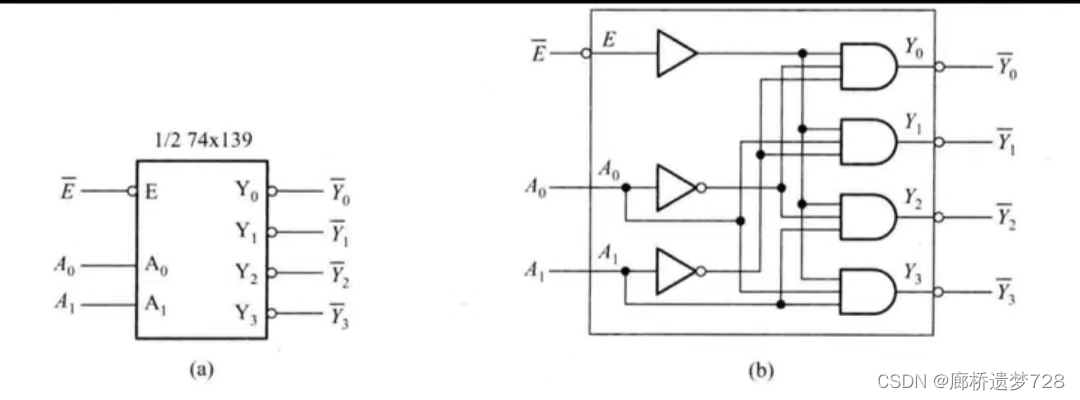

2线-4线译码器

有两个输入变量A1、A0,共有4种不同状态组合,因而有4个输出端。其框图和结构如下:

E:使能端,如上图所示为低电平有效,字母上的“-”号说明低电平有效(而不是逻辑非)。

其真值表如下:

| 输入 | 输出 | |||||

| E | A1 | A0 | Y0 | Y1 | Y2 | Y3 |

| 1 | X | X | 1 | 1 | 1 | 1 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 0 |

3线-8线译码器

框图和结构如下所示:

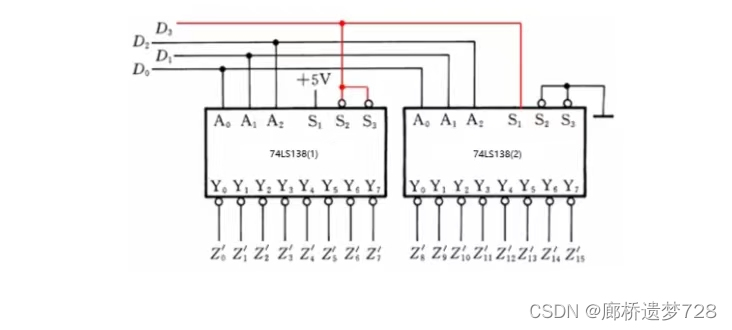

设置了3个使能端,当E1、E2为低电平,E3为高电平时译码器工作,为扩展电路的功能(级联)提供了方便。如下图为级联:

当D3 = 0时,(1)译码器工作,(2)译码器被禁止。若输入D3、D2、D1、D0=0100时,译码器(1)输出:11110111。

当D3 = 1时,(2)译码器工作,(1)译码器被禁止。若输入D3、D2、D1、D0=1101时,译码器2输出:11111011。

七段显示译码器

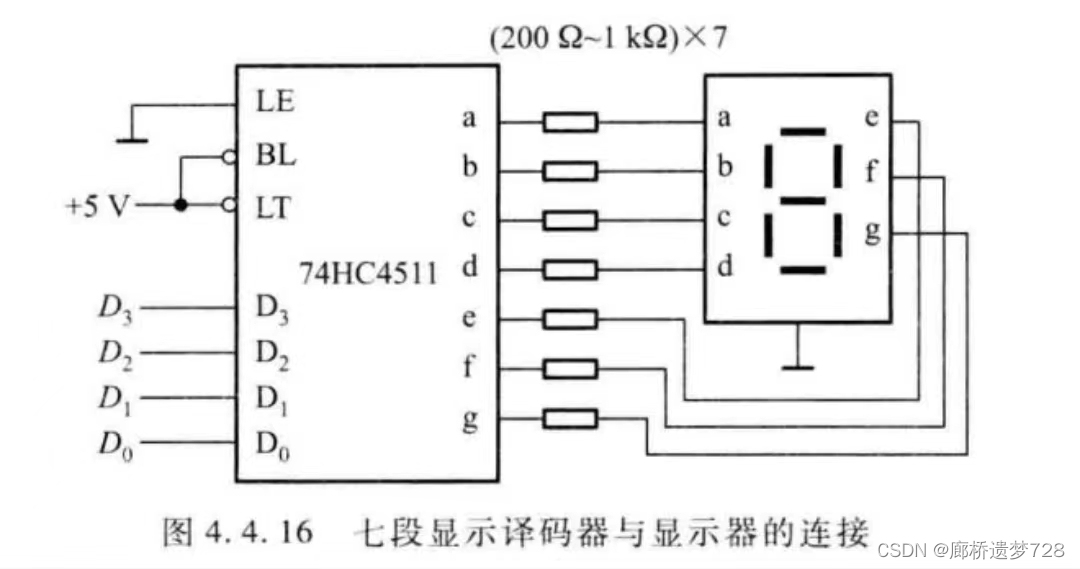

用来驱动各种显示器件,从而将用二进制代码表示的数字、文字、符号翻译成人们习惯的形式直观地显示出来的电路,称为显示译码器。

七段显示译码器:将输入的BCD码译成相应输出信号,以驱动显示器显示出相应数字(0到9)的电路。

LT:灯测试输入,当其为有效电平时,无论输入是什么,每一个二极管都会亮(用来测试二极管的好坏)。

BL:当BL输入有效电平、LT为无效电平时,无论输入什么,二极管均熄灭。例如:当我们在显示0023.0800时,实际上只需显示23.08即可,把其他位置上的0熄灭即可。

LE:锁存使能输入,当LE为无效值时(参照上图为0),锁存器不工作,译码器的输出随输入D变化而变化;当LE为有效电平时,输出只取决于锁存器的内容。

1033

1033

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?