认识时钟树

1.1什么是时钟

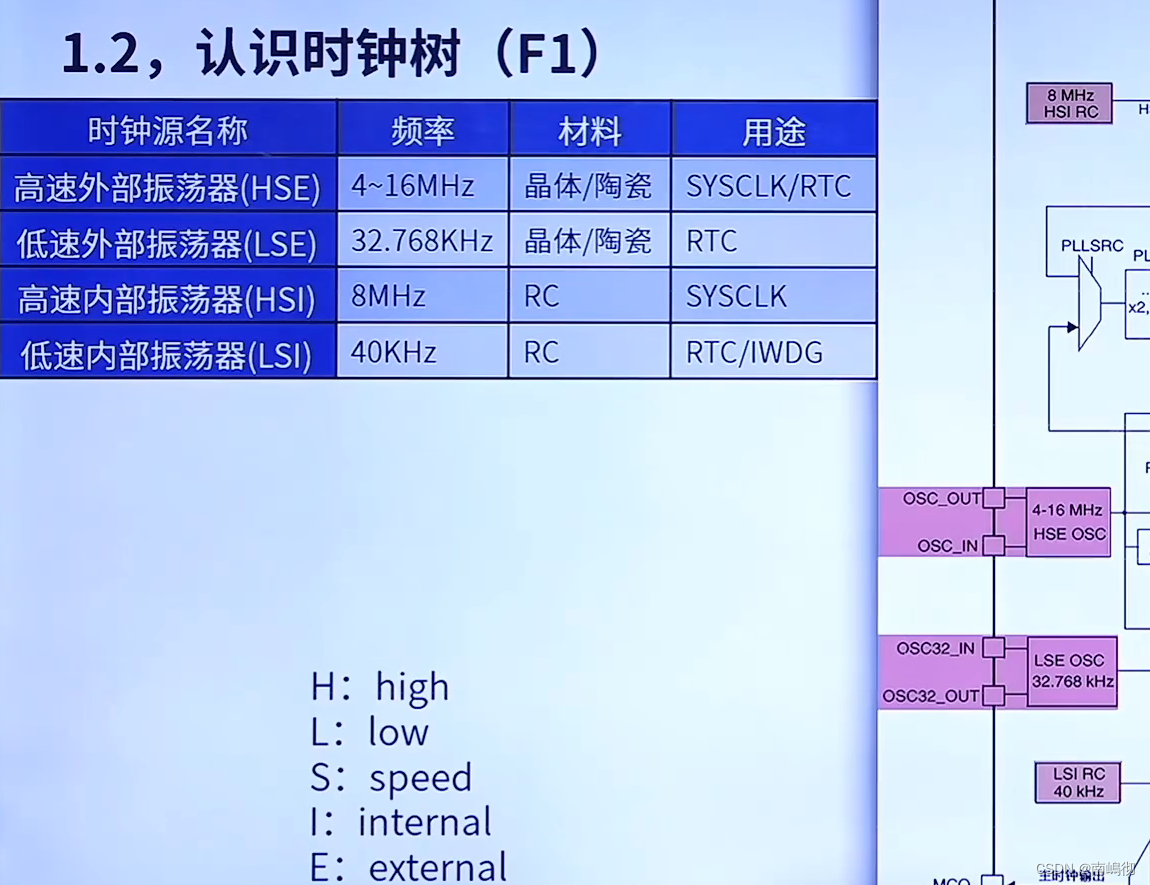

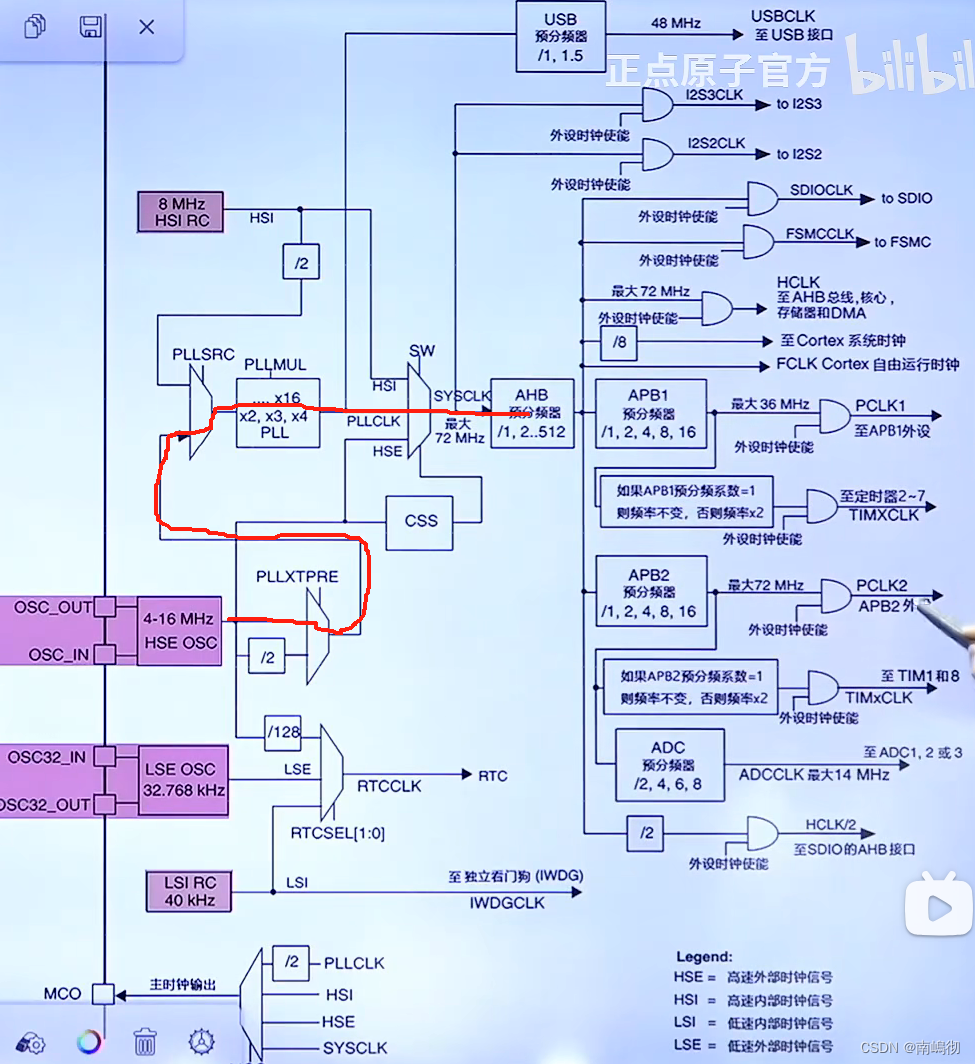

每个振荡器都对应着右边的图片 外部就是芯片外部的晶振(接入芯片内部) 内部振荡器就是在芯片内部的

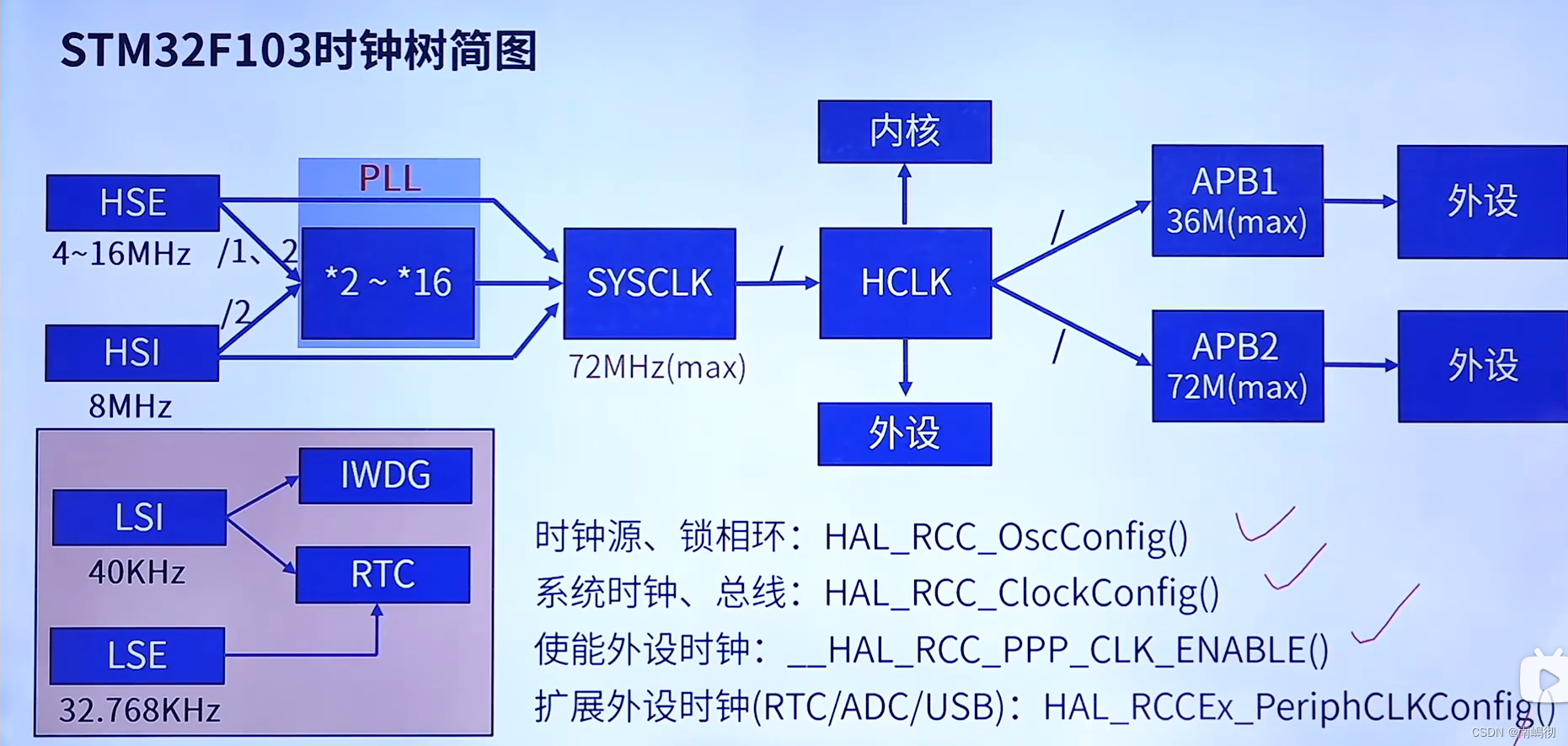

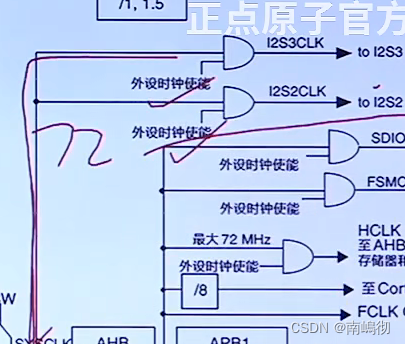

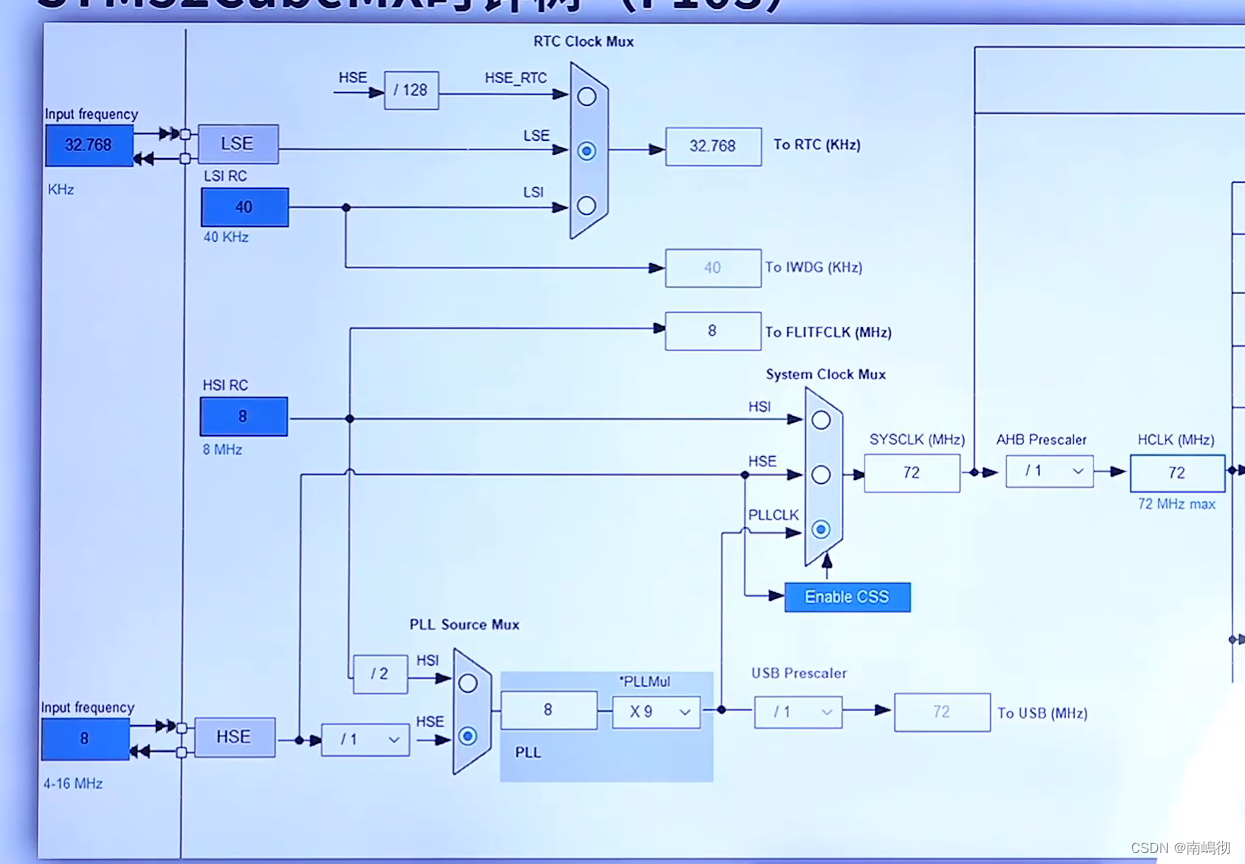

HSE 和HSI都是高速的振荡器 外部的可以提供4-16MHZ的晶振 内部可提供8MHZ的晶振 SYSCLK是系统的内部时钟 他的晶振是72MHZ HSE和HSI通过锁相环使得晶振频率增加到72MHZ

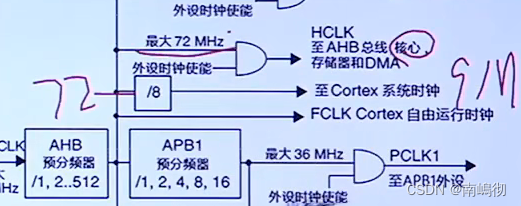

外部振荡器HSE可以有两条路到系统的内部时钟(大部分使用的都是外部晶振 内部的太小了通过了锁相环后无法达到72MHZ) 然后到达HCLK(AHB总线) 有前面的学习可知 AHB总线也挂载着外设 内核的时钟也是由HCLK提供的 AHB总线通过桥分为APB1和APB2(两个都挂载着外设)SYSCLK通过分频到达HCLK HCLK通过分频到达APB1 APB2

LSI 和LSE都是低速晶振

右下角的四个函数 通过调用这些函数从而改变分频、锁相环 使得各个部分的时钟得以配置 还有外设的时钟得以配置

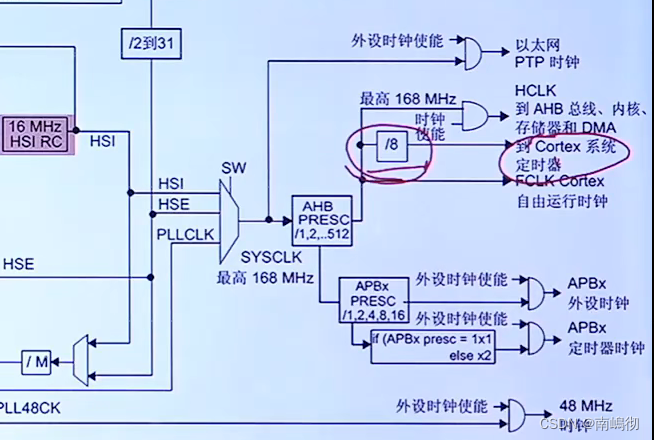

外部时钟通过选择器(选择器通过寄存器来编写选择位) 走1通道 (如果走2通道就要分频 8变为4)然后再到一个选择器通过锁相器到达系统的时钟 (系统时钟的三条线代表着三个来源)然后通过选择器在到达AHB总线(不分频) AHB总线通过桥分为APB1 APB2 (AHB总线位72MHZ)但是APB1的时钟是36MHZ通过了二分频(选择器)外设线要使能时钟才能使用(不然时钟无法到达外设)

AHB总线为72MHZ通过分屏(8分频)到达系统时钟)(9MHZ)然后到HCLK为72MHZ

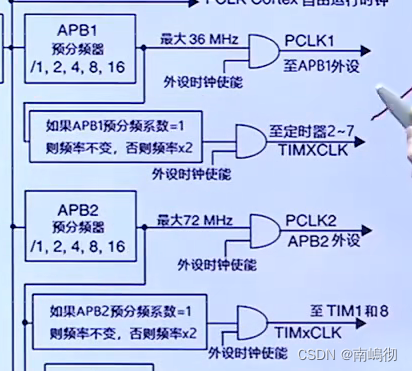

定时器的时钟系统 :定时器2-7挂载在APB1总线上 (最大36MHZ)如果要使得时钟为72MHZ要经过倍频器

下面的TIM1和8定时器挂载在APB2总线上 最大时72MHZ

外设时钟 要使用一个外设首先要给外设的时钟使能

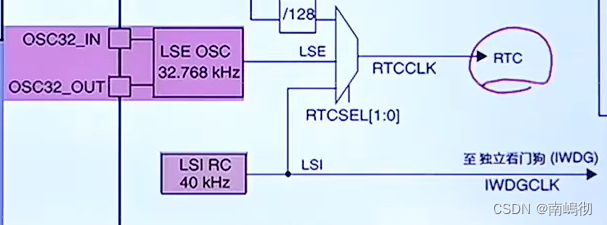

看门狗由内部低速振荡器提供时钟 (需要的精度不是很高) RTC一个外设(时钟由外部高速振荡器提供 需求的精度高) 外部时钟比内部时钟的精度要高

STM32CubeMX时钟树(F103)

到F4在详细介绍

认识时钟树

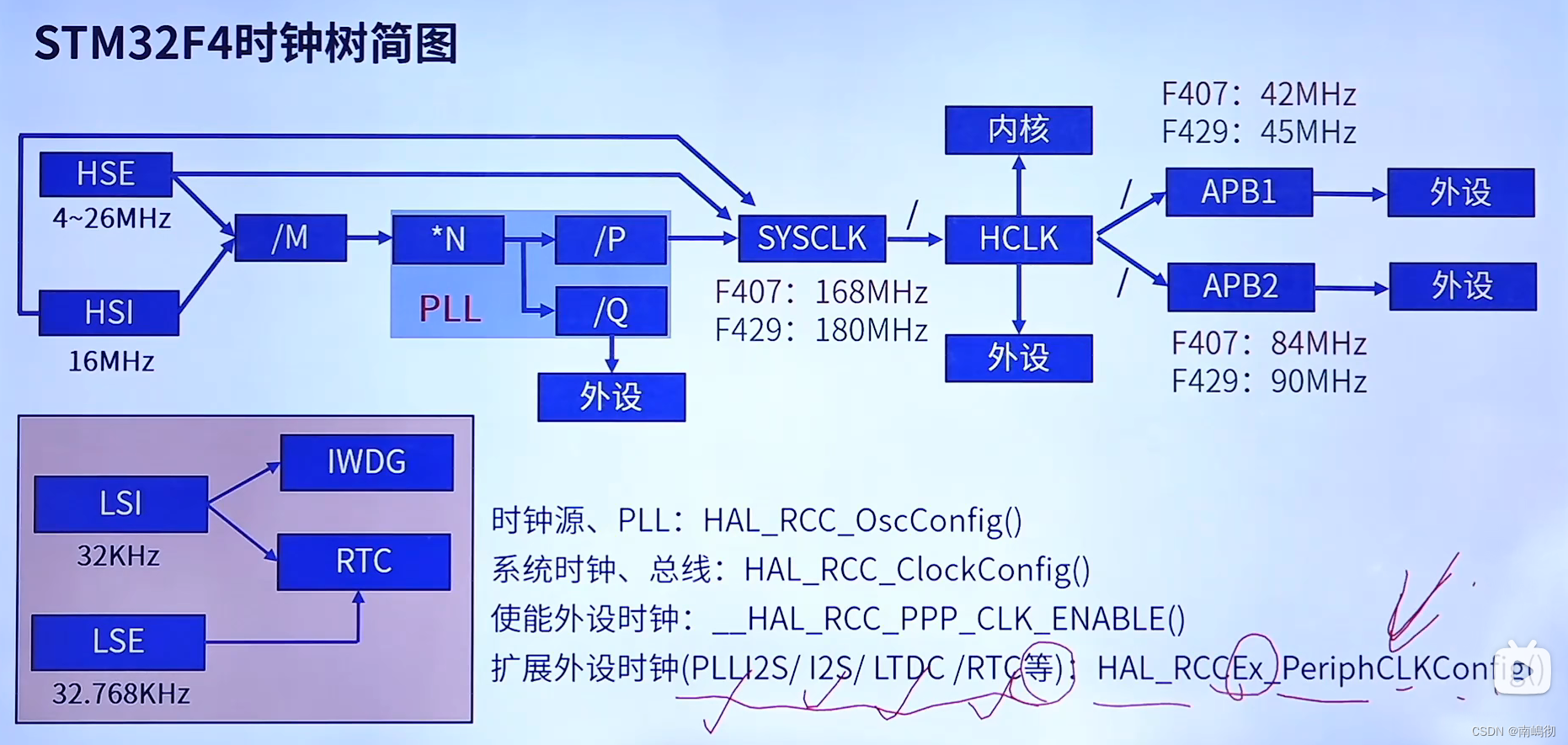

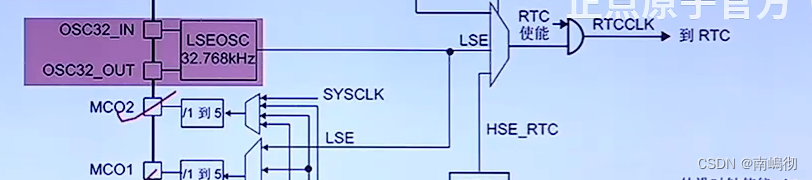

F4时钟简图

HSE(外部) 和HSI(内部) 高速晶振 通过分频(/M)锁相环到达SYSCLK系统时钟F407:168MHZ 通过分频到达AHB总线 AHB总线通过桥到达APB1 和APB2 (也有分屏) 为外设提供时钟 右下脚的函数是配置SYSCLK时钟的来源和其他总线的时钟的

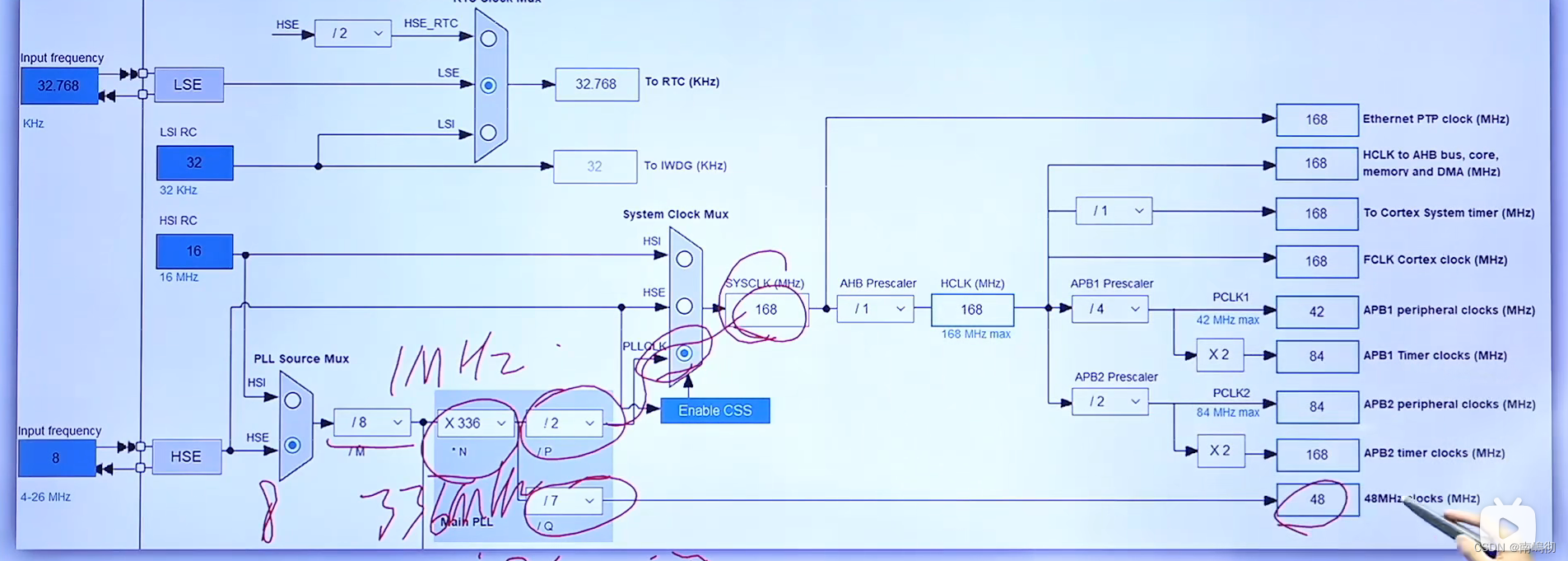

首先外部振荡器HSE经过线到达第一个选择器然后/M(分频)进入第一个锁相环 PLL到达VCO(V代表电压 C代表震荡 O代表稳定 电压震荡稳定器)到达VCO这个中枢有下面的*n (倍频)然后出VCO有三条路(都是分频)/P /Q /R(/R没用) /P后进入系统时钟到达SYSCLK /Q为外设提供时钟(要使用外设要先给外设时钟使能)

系统时钟SYSCLK到达AHB总线AHB总线经过桥到达APB1 和APB2 (这里统称APBX)

在F407系列中APB1为42MZH APB2为84MHZ 总系统时钟168MHZ经过分频后(APB1分4 APB2分2) 给外设时钟 挂载在APB1 和APB2总线上的定时器得到时钟 (可以去芯片手册查询挂载在APB1 和APB2 上的定时器)

然后AHB总线还可以通过上面的选择器给予FLASH SRAM(储存器)时钟 还可分频(/8)给内核时钟

上面的RTC优先使用外部低速振荡器获得时钟 要是外部低速振荡器挂了就启用外部高速振荡器

CubeMX时钟树图

3519

3519

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?