实验2 带控制端的8位运算器设计

一、实验目的

- 掌握加法器的设计方法。

- 掌握测试文件的设计方法。

- 掌握FPGA技术的层次化设计方法。

- 掌握FPGA下载测试方法。

二、实验主要仪器设备

- FPGA实验板

- FPGA实验板配套软件,ModelSim仿真软件

三、设计任务与要求

1. 基本任务及要求

(1)用Verilog设计一个带低有效控制端的一位全加器,再利用级联方法构成带低有效控制端的8位加法器。

(2)用Verilog测试文件,实现ModelSim时序仿真。

(3)根据FPGA开发板,配置输入和输出管脚,生成下载文件,实现下载测试。

2. 扩展任务及要求

(1)用Verilog设计带低有效控制端的4位并行进位加法器,再利用层次设计方法构成带低有效控制端的8位并行加法器。

(2)用Verilog设计加减运算器,通过控制端完成8位加法和8位减法的转换。

(3)用Verilog测试文件,实现ModelSim时序仿真。

(4)根据FPGA开发板,配置输入和输出管脚,生成下载文件,实现下载测试。

四、实验内容与步骤

1. 基本任务

(1) 带低有效控制端的1位全加器

(a) 工作原理

输入信号:

a 和 b:两个要进行加法的二进制位。

cin:来自低位的进位输入。

enable:控制端,当其为低电平(如0)时,全加器处于活动状态,进行加法运算;当其为高电平(如1)时,全加器处于非活动状态,不执行加法运算。

加法运算:

当enable为低电平时,全加器执行以下加法运算:

使用a、b和Cin作为输入,全加器会计算这三个输入位的和(Sum),并确定是否需要向高位进位(Cout)。

输出信号:

Sum:a、b和Cin的和的二进制表示。

Cout:如果加法运算产生了向高位的进位,则Cout为高电平;否则为低电平。

控制端的影响:

当enable为高电平时,全加器的输出(Sum和Cout)不会根据输入(a、b、Cin)的变化而更新。它们可能保持之前的值,或者根据全加器的具体实现而定(可能是高阻态、不确定态或固定值)。

(b) Verilog源程序

`timescale 1ns / 1ps

module full_adder_with_enable(

input a, b, cin, enable,

output reg sum, cout // 使用reg以支持条件赋值

);

// 当enable为0时,执行全加操作

// 当enable为1时,sum和cout保持为0(或你可以根据需要设置其他值)

always @(*) begin

if (!enable) begin

sum = cin ^ a ^ b;

cout = (a & b) | ((a ^ b) & cin); // 这里使用括号确保正确的运算顺序

end else begin

// 例如,将它们置为0

sum = 0;

cout = 0;

end

end

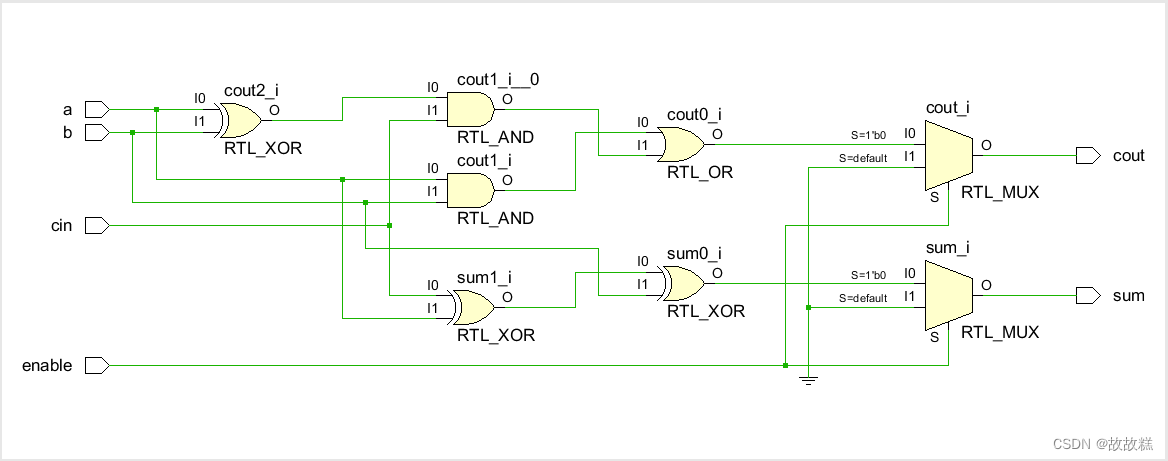

endmodule(c) RTL视图

下图中

a 和 b:两个要进行加法的二进制位。

cin:来自低位的进位输入。

enable:控制端,(低有效)

(d) ModelSim源程序

`timescale 1ns / 1ps

module full_adder_with_enable_tb;

// 输入和输出信号的声明

reg a, b, cin, enable;

wire sum, cout;

// 实例化被测试的模块

full_adder_with_enable DUT (

.a(a),

.b(b),

.cin(cin),

.enable(enable),

.sum(sum),

.cout(cout)

);

initial begin

enable = 0; cin = 0; a = 0; b = 0;

#10; // 等待10个时间单位

enable = 0; cin = 0; a = 0; b = 1;

#10; // 等待10个时间单位

enable = 0; cin = 0; a = 1; b = 0;

#10; // 等待10个时间单位

enable = 0; cin = 0; a = 1; b = 1;

#10; // 等待10个时间单位

enable = 0; cin = 1; a = 0; b = 0;

#10; // 等待10个时间单位

enable = 0; cin = 1; a = 0; b = 1;

#10; // 等待10个时间单位

enable = 0; cin = 1; a = 1; b = 0;

#10; // 等待10个时间单位

enable = 0; cin = 1; a =1 ; b = 1;

#10; // 等待10个时间单位

enable = 1; cin = 0; a = 0; b = 0;

#10; // 等待10个时间单位

enable =1; cin = 0; a = 0; b = 1;

#10; // 等待10个时间单位

enable = 1; cin = 0; a = 1; b = 0;

#10; // 等待10个时间单位

enable = 1; cin = 0; a = 1; b = 1;

#10; // 等待10个时间单位

enable = 1; cin = 1; a = 0; b = 0;

#10; // 等待10个时间单位

enable = 1; cin = 1; a = 0; b = 1;

#10; // 等待10个时间单位

enable = 1; cin = 1; a = 1; b = 0;

#10; // 等待10个时间单位

enable = 1; cin = 1; a = 1; b = 1;

#10; // 等待10个时间单位

$stop;

end

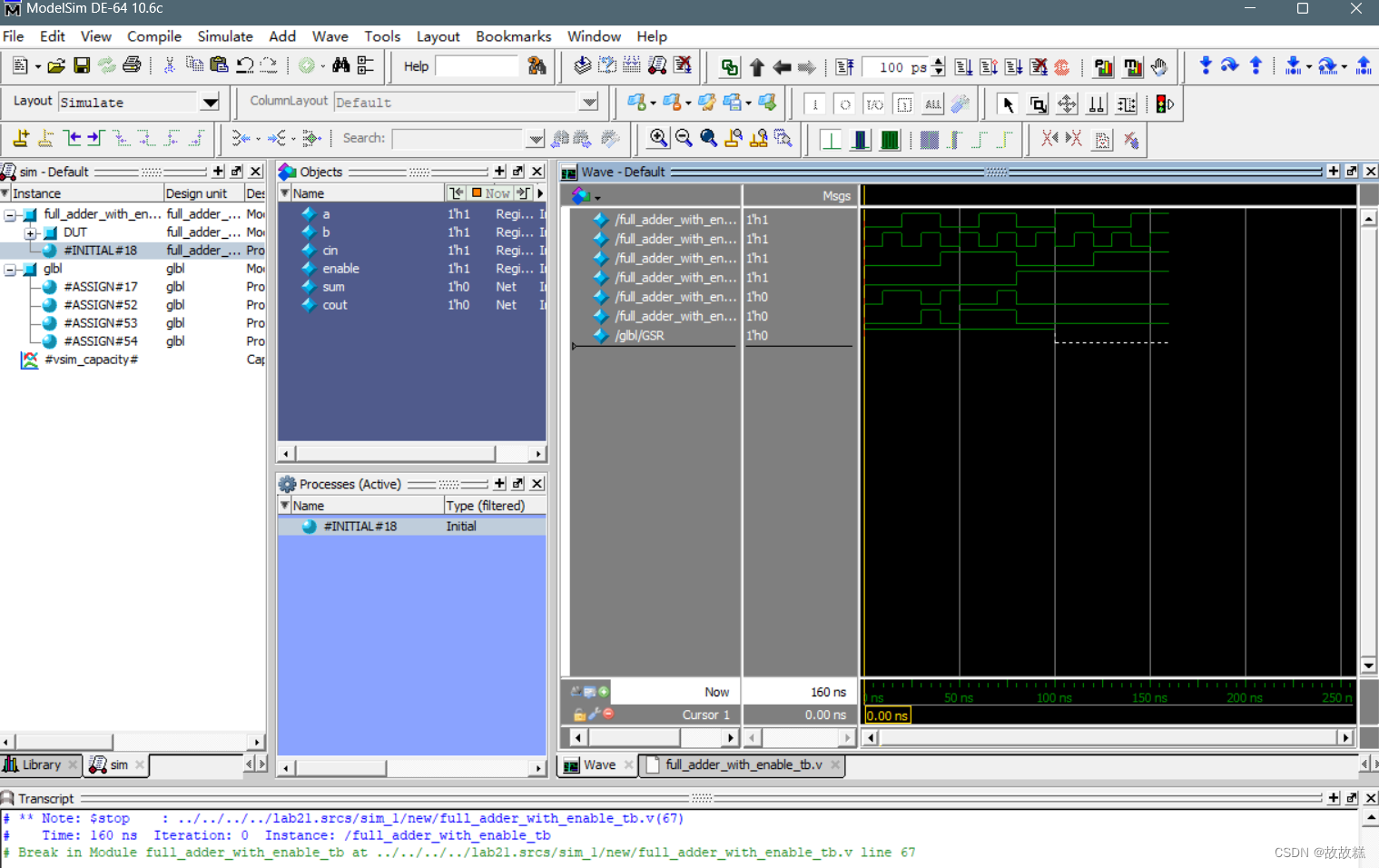

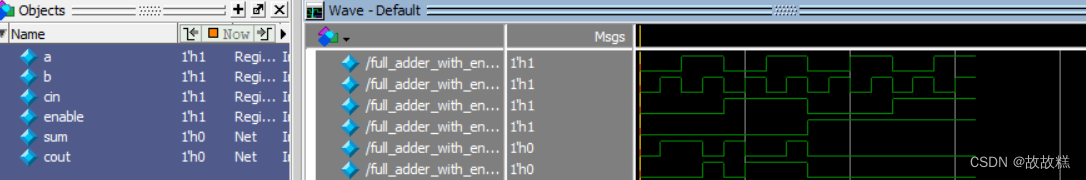

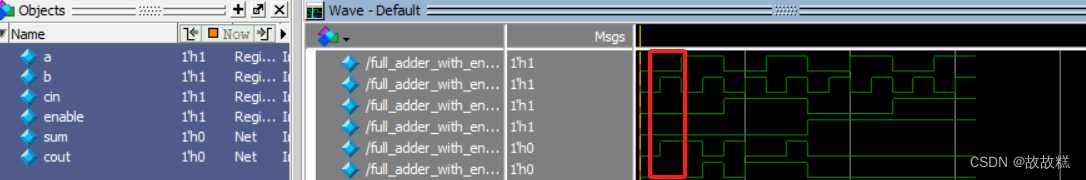

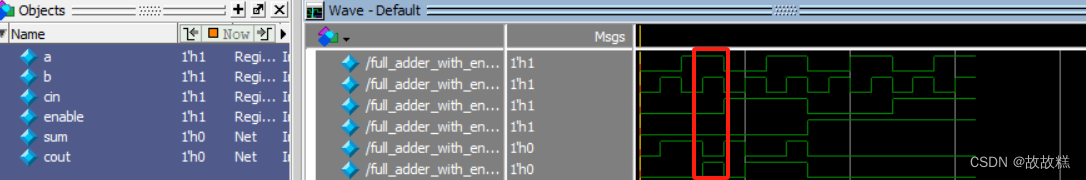

endmodule(d) ModelSim仿真结果

a 和 b:两个要进行加法的二进制位。

cin:来自低位的进位输入。

enable:控制端,(低有效)

分析:

当使能端为高电平时,加法器不工作,输出cout 和sum 输出为0

当使能端为低电平时,加法器工作,当输入a=0,b=0,cin=0,输出sum=0,进位输出cout=0

当使能端为低电平时,加法器工作,当输入a=0,b=1,cin=0,输出sum=1,进位输出cout=0

当使能端为低电平时,加法器工作,当输入a=1,b=1,cin=0,输出sum=0,进位输出cout=1

当使能端为低电平时,加法器工作,当输入a=1,b=1,cin=1,输出sum=0,进位输出cout=1

(e) 下载测试结果

管脚配置

#Clock

set_property -dict {PACKAGE_PIN K21 IOSTANDARD LVCMOS33} [get_ports clk_50M] ;#50MHz main clock in

set_property -dict {PACKAGE_PIN H21 IOSTANDARD LVCMOS33} [get_ports clk_11M0592] ;#11.0592MHz clock for UART

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clk_11M0592_IBUF]

create_clock -period 20.000 -name clk_50M -waveform {0.000 10.000} [get_ports clk_50M]

create_clock -period 90.422 -name clk_11M0592 -waveform {0.000 45.211} [get_ports clk_11M0592]

#Touch Button

set_property -dict {PACKAGE_PIN T2 IOSTANDARD LVCMOS33} [get_ports touch_btn[0]] ;#BTN1

set_property -dict {PACKAGE_PIN M1 IOSTANDARD LVCMOS33} [get_ports touch_btn[1]] ;#BTN2

set_property -dict {PACKAGE_PIN P3 IOSTANDARD LVCMOS33} [get_ports touch_btn[2]] ;#BTN3

set_property -dict {PACKAGE_PIN U2 IOSTANDARD LVCMOS33} [get_ports touch_btn[3]] ;#BTN4

set_property -dict {PACKAGE_PIN U1 IOSTANDARD LVCMOS33} [get_ports clock_btn] ;#BTN5

set_property -dict {PACKAGE_PIN U5 IOSTANDARD LVCMOS33} [get_ports reset_btn] ;#BTN6

#required if touch button used as manual clock source

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clock_btn_IBUF]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets reset_btn_IBUF]

#CPLD GPIO 12-16

#set_property -dict {PACKAGE_PIN J14 IOSTANDARD LVCMOS33} [get_ports {uart_wrn}]

#set_property -dict {PACKAGE_PIN L14 IOSTANDARD LVCMOS33} [get_ports {uart_rdn}]

#set_property -dict {PACKAGE_PIN J15 IOSTANDARD LVCMOS33} [get_ports {uart_tbre}]

#set_property -dict {PACKAGE_PIN K15 IOSTANDARD LVCMOS33} [get_ports {uart_tsre}]

#set_property -dict {PACKAGE_PIN L15 IOSTANDARD LVCMOS33} [get_ports {uart_dataready}]

#Ext serial

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN H18} [get_ports txd] ;#GPIO5

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN J20} [get_ports rxd] ;#GPIO6

#Digital Video

set_property -dict {PACKAGE_PIN H22 IOSTANDARD LVCMOS33} [get_ports video_clk]

set_property -dict {PACKAGE_PIN E26 IOSTANDARD LVCMOS33} [get_ports {video_red[2]}]

set_property -dict {PACKAGE_PIN F24 IOSTANDARD LVCMOS33} [get_ports {video_red[1]}]

set_property -dict {PACKAGE_PIN K23 IOSTANDARD LVCMOS33} [get_ports {video_red[0]}]

set_property -dict {PACKAGE_PIN F23 IOSTANDARD LVCMOS33} [get_ports {video_green[2]}]

set_property -dict {PACKAGE_PIN E23 IOSTANDARD LVCMOS33} [get_ports {video_green[1]}]

set_property -dict {PACKAGE_PIN K22 IOSTANDARD LVCMOS33} [get_ports {video_green[0]}]

set_property -dict {PACKAGE_PIN D25 IOSTANDARD LVCMOS33} [get_ports {video_blue[1]}]

set_property -dict {PACKAGE_PIN E25 IOSTANDARD LVCMOS33} [get_ports {video_blue[0]}]

set_property -dict {PACKAGE_PIN J24 IOSTANDARD LVCMOS33} [get_ports video_hsync]

set_property -dict {PACKAGE_PIN H24 IOSTANDARD LVCMOS33} [get_ports video_vsync]

set_property -dict {PACKAGE_PIN G24 IOSTANDARD LVCMOS33} [get_ports video_de]

#LEDS

set_property -dict {PACKAGE_PIN B24 IOSTANDARD LVCMOS33} [get_ports sum]

set_property -dict {PACKAGE_PIN E21 IOSTANDARD LVCMOS33} [get_ports cout]

set_property -dict {PACKAGE_PIN A24 IOSTANDARD LVCMOS33} [get_ports {leds[2]}]

set_property -dict {PACKAGE_PIN D23 IOSTANDARD LVCMOS33} [get_ports {leds[3]}]

set_property -dict {PACKAGE_PIN C22 IOSTANDARD LVCMOS33} [get_ports {leds[4]}]

set_property -dict {PACKAGE_PIN C21 IOSTANDARD LVCMOS33} [get_ports {leds[5]}]

set_property -dict {PACKAGE_PIN E20 IOSTANDARD LVCMOS33} [get_ports {leds[6]}]

set_property -dict {PACKAGE_PIN B22 IOSTANDARD LVCMOS33} [get_ports {leds[7]}]

set_property -dict {PACKAGE_PIN C23 IOSTANDARD LVCMOS33} [get_ports {leds[8]}]

set_property -dict {PACKAGE_PIN A23 IOSTANDARD LVCMOS33} [get_ports {leds[9]}]

set_property -dict {PACKAGE_PIN D21 IOSTANDARD LVCMOS33} [get_ports {leds[10]}]

set_property -dict {PACKAGE_PIN A18 IOSTANDARD LVCMOS33} [get_ports {leds[11]}]

set_property -dict {PACKAGE_PIN D20 IOSTANDARD LVCMOS33} [get_ports {leds[12]}]

set_property -dict {PACKAGE_PIN A22 IOSTANDARD LVCMOS33} [get_ports {leds[13]}]

set_property -dict {PACKAGE_PIN A20 IOSTANDARD LVCMOS33} [get_ports {leds[14]}]

set_property -dict {PACKAGE_PIN B20 IOSTANDARD LVCMOS33} [get_ports {leds[15]}]

#DPY0

set_property -dict {PACKAGE_PIN B19 IOSTANDARD LVCMOS33} [get_ports {dpy0[0]}]

set_property -dict {PACKAGE_PIN D19 IOSTANDARD LVCMOS33} [get_ports {dpy0[1]}]

set_property -dict {PACKAGE_PIN B21 IOSTANDARD LVCMOS33} [get_ports {dpy0[2]}]

set_property -dict {PACKAGE_PIN A19 IOSTANDARD LVCMOS33} [get_ports {dpy0[3]}]

set_property -dict {PACKAGE_PIN E18 IOSTANDARD LVCMOS33} [get_ports {dpy0[4]}]

set_property -dict {PACKAGE_PIN C19 IOSTANDARD LVCMOS33} [get_ports {dpy0[5]}]

set_property -dict {PACKAGE_PIN B17 IOSTANDARD LVCMOS33} [get_ports {dpy0[6]}]

set_property -dict {PACKAGE_PIN C17 IOSTANDARD LVCMOS33} [get_ports {dpy0[7]}]

#DPY1

set_property -dict {PACKAGE_PIN A17 IOSTANDARD LVCMOS33} [get_ports {dpy1[0]}]

set_property -dict {PACKAGE_PIN D16 IOSTANDARD LVCMOS33} [get_ports {dpy1[1]}]

set_property -dict {PACKAGE_PIN E17 IOSTANDARD LVCMOS33} [get_ports {dpy1[2]}]

set_property -dict {PACKAGE_PIN F17 IOSTANDARD LVCMOS33} [get_ports {dpy1[3]}]

set_property -dict {PACKAGE_PIN E16 IOSTANDARD LVCMOS33} [get_ports {dpy1[4]}]

set_property -dict {PACKAGE_PIN G16 IOSTANDARD LVCMOS33} [get_ports {dpy1[5]}]

set_property -dict {PACKAGE_PIN F15 IOSTANDARD LVCMOS33} [get_ports {dpy1[6]}]

set_property -dict {PACKAGE_PIN G17 IOSTANDARD LVCMOS33} [get_ports {dpy1[7]}]

#DIP_SW

set_property -dict {PACKAGE_PIN T3 IOSTANDARD LVCMOS33} [get_ports enable]

set_property -dict {PACKAGE_PIN J3 IOSTANDARD LVCMOS33} [get_ports cin]

set_property -dict {PACKAGE_PIN M2 IOSTANDARD LVCMOS33} [get_ports a]

set_property -dict {PACKAGE_PIN P1 IOSTANDARD LVCMOS33} [get_ports b]

set_property -dict {PACKAGE_PIN P4 IOSTANDARD LVCMOS33} [get_ports {dip_sw[4]}]

set_property -dict {PACKAGE_PIN L5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[5]}]

set_property -dict {PACKAGE_PIN L3 IOSTANDARD LVCMOS33} [get_ports {dip_sw[6]}]

set_property -dict {PACKAGE_PIN N6 IOSTANDARD LVCMOS33} [get_ports {dip_sw[7]}]

set_property -dict {PACKAGE_PIN M6 IOSTANDARD LVCMOS33} [get_ports {dip_sw[8]}]

set_property -dict {PACKAGE_PIN N7 IOSTANDARD LVCMOS33} [get_ports {dip_sw[9]}]

set_property -dict {PACKAGE_PIN M7 IOSTANDARD LVCMOS33} [get_ports {dip_sw[10]}]

set_property -dict {PACKAGE_PIN L7 IOSTANDARD LVCMOS33} [get_ports {dip_sw[11]}]

set_property -dict {PACKAGE_PIN M5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[12]}]

set_property -dict {PACKAGE_PIN K3 IOSTANDARD LVCMOS33} [get_ports {dip_sw[13]}]

set_property -dict {PACKAGE_PIN J1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[14]}]

set_property -dict {PACKAGE_PIN L2 IOSTANDARD LVCMOS33} [get_ports {dip_sw[15]}]

set_property -dict {PACKAGE_PIN K2 IOSTANDARD LVCMOS33} [get_ports {dip_sw[16]}]

set_property -dict {PACKAGE_PIN K1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[17]}]

set_property -dict {PACKAGE_PIN N3 IOSTANDARD LVCMOS33} [get_ports {dip_sw[18]}]

set_property -dict {PACKAGE_PIN L4 IOSTANDARD LVCMOS33} [get_ports {dip_sw[19]}]

set_property -dict {PACKAGE_PIN M4 IOSTANDARD LVCMOS33} [get_ports {dip_sw[20]}]

set_property -dict {PACKAGE_PIN N2 IOSTANDARD LVCMOS33} [get_ports {dip_sw[21]}]

set_property -dict {PACKAGE_PIN P6 IOSTANDARD LVCMOS33} [get_ports {dip_sw[22]}]

set_property -dict {PACKAGE_PIN N1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[23]}]

set_property -dict {PACKAGE_PIN P5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[24]}]

set_property -dict {PACKAGE_PIN R3 IOSTANDARD LVCMOS33} [get_ports {dip_sw[25]}]

set_property -dict {PACKAGE_PIN T4 IOSTANDARD LVCMOS33} [get_ports {dip_sw[26]}]

set_property -dict {PACKAGE_PIN R1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[27]}]

set_property -dict {PACKAGE_PIN R5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[28]}]

set_property -dict {PACKAGE_PIN T5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[29]}]

set_property -dict {PACKAGE_PIN R6 IOSTANDARD LVCMOS33} [get_ports {dip_sw[30]}]

set_property -dict {PACKAGE_PIN R2 IOSTANDARD LVCMOS33} [get_ports {dip_sw[31]}]

set_property -dict {PACKAGE_PIN C2 IOSTANDARD LVCMOS33} [get_ports {flash_a[0]}]

set_property -dict {PACKAGE_PIN H9 IOSTANDARD LVCMOS33} [get_ports {flash_a[1]}]

set_property -dict {PACKAGE_PIN H8 IOSTANDARD LVCMOS33} [get_ports {flash_a[2]}]

set_property -dict {PACKAGE_PIN G9 IOSTANDARD LVCMOS33} [get_ports {flash_a[3]}]

set_property -dict {PACKAGE_PIN H7 IOSTANDARD LVCMOS33} [get_ports {flash_a[4]}]

set_property -dict {PACKAGE_PIN F8 IOSTANDARD LVCMOS33} [get_ports {flash_a[5]}]

set_property -dict {PACKAGE_PIN G8 IOSTANDARD LVCMOS33} [get_ports {flash_a[6]}]

set_property -dict {PACKAGE_PIN K7 IOSTANDARD LVCMOS33} [get_ports {flash_a[7]}]

set_property -dict {PACKAGE_PIN G7 IOSTANDARD LVCMOS33} [get_ports {flash_a[8]}]

set_property -dict {PACKAGE_PIN F7 IOSTANDARD LVCMOS33} [get_ports {flash_a[9]}]

set_property -dict {PACKAGE_PIN E6 IOSTANDARD LVCMOS33} [get_ports {flash_a[10]}]

set_property -dict {PACKAGE_PIN D6 IOSTANDARD LVCMOS33} [get_ports {flash_a[11]}]

set_property -dict {PACKAGE_PIN F5 IOSTANDARD LVCMOS33} [get_ports {flash_a[12]}]

set_property -dict {PACKAGE_PIN E3 IOSTANDARD LVCMOS33} [get_ports {flash_a[13]}]

set_property -dict {PACKAGE_PIN G5 IOSTANDARD LVCMOS33} [get_ports {flash_a[14]}]

set_property -dict {PACKAGE_PIN F4 IOSTANDARD LVCMOS33} [get_ports {flash_a[15]}]

set_property -dict {PACKAGE_PIN H6 IOSTANDARD LVCMOS33} [get_ports {flash_a[16]}]

set_property -dict {PACKAGE_PIN G4 IOSTANDARD LVCMOS33} [get_ports {flash_a[17]}]

set_property -dict {PACKAGE_PIN J6 IOSTANDARD LVCMOS33} [get_ports {flash_a[18]}]

set_property -dict {PACKAGE_PIN H4 IOSTANDARD LVCMOS33} [get_ports {flash_a[19]}]

set_property -dict {PACKAGE_PIN J5 IOSTANDARD LVCMOS33} [get_ports {flash_a[20]}]

set_property -dict {PACKAGE_PIN J4 IOSTANDARD LVCMOS33} [get_ports {flash_a[21]}]

set_property -dict {PACKAGE_PIN K6 IOSTANDARD LVCMOS33} [get_ports {flash_a[22]}]

set_property -dict {PACKAGE_PIN D4 IOSTANDARD LVCMOS33} [get_ports {flash_d[0]}]

set_property -dict {PACKAGE_PIN C1 IOSTANDARD LVCMOS33} [get_ports {flash_d[1]}]

set_property -dict {PACKAGE_PIN D1 IOSTANDARD LVCMOS33} [get_ports {flash_d[2]}]

set_property -dict {PACKAGE_PIN E1 IOSTANDARD LVCMOS33} [get_ports {flash_d[3]}]

set_property -dict {PACKAGE_PIN G1 IOSTANDARD LVCMOS33} [get_ports {flash_d[4]}]

set_property -dict {PACKAGE_PIN A2 IOSTANDARD LVCMOS33} [get_ports {flash_d[5]}]

set_property -dict {PACKAGE_PIN C3 IOSTANDARD LVCMOS33} [get_ports {flash_d[6]}]

set_property -dict {PACKAGE_PIN B4 IOSTANDARD LVCMOS33} [get_ports {flash_d[7]}]

set_property -dict {PACKAGE_PIN D3 IOSTANDARD LVCMOS33} [get_ports {flash_d[8]}]

set_property -dict {PACKAGE_PIN E2 IOSTANDARD LVCMOS33} [get_ports {flash_d[9]}]

set_property -dict {PACKAGE_PIN F3 IOSTANDARD LVCMOS33} [get_ports {flash_d[10]}]

set_property -dict {PACKAGE_PIN F2 IOSTANDARD LVCMOS33} [get_ports {flash_d[11]}]

set_property -dict {PACKAGE_PIN G2 IOSTANDARD LVCMOS33} [get_ports {flash_d[12]}]

set_property -dict {PACKAGE_PIN B2 IOSTANDARD LVCMOS33} [get_ports {flash_d[13]}]

set_property -dict {PACKAGE_PIN A3 IOSTANDARD LVCMOS33} [get_ports {flash_d[14]}]

set_property -dict {PACKAGE_PIN A4 IOSTANDARD LVCMOS33} [get_ports {flash_d[15]}]

set_property -dict {PACKAGE_PIN B1 IOSTANDARD LVCMOS33} [get_ports flash_byte_n]

set_property -dict {PACKAGE_PIN E5 IOSTANDARD LVCMOS33} [get_ports flash_ce_n ]

set_property -dict {PACKAGE_PIN A5 IOSTANDARD LVCMOS33} [get_ports flash_oe_n ]

set_property -dict {PACKAGE_PIN G6 IOSTANDARD LVCMOS33} [get_ports flash_rp_n ]

set_property -dict {PACKAGE_PIN D5 IOSTANDARD LVCMOS33} [get_ports flash_vpen ]

set_property -dict {PACKAGE_PIN B5 IOSTANDARD LVCMOS33} [get_ports flash_we_n ]

set_property -dict {PACKAGE_PIN T19 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[0]}]

set_property -dict {PACKAGE_PIN V18 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[1]}]

set_property -dict {PACKAGE_PIN T18 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[2]}]

set_property -dict {PACKAGE_PIN V17 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[3]}]

set_property -dict {PACKAGE_PIN U17 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[4]}]

set_property -dict {PACKAGE_PIN R20 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[5]}]

set_property -dict {PACKAGE_PIN R23 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[6]}]

set_property -dict {PACKAGE_PIN T23 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[7]}]

set_property -dict {PACKAGE_PIN U22 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[8]}]

set_property -dict {PACKAGE_PIN Y22 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[9]}]

set_property -dict {PACKAGE_PIN AB24 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[10]}]

set_property -dict {PACKAGE_PIN AA23 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[11]}]

set_property -dict {PACKAGE_PIN Y21 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[12]}]

set_property -dict {PACKAGE_PIN Y20 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[13]}]

set_property -dict {PACKAGE_PIN AA22 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[14]}]

set_property -dict {PACKAGE_PIN W19 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[15]}]

set_property -dict {PACKAGE_PIN W21 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[16]}]

set_property -dict {PACKAGE_PIN W20 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[17]}]

set_property -dict {PACKAGE_PIN W18 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[18]}]

set_property -dict {PACKAGE_PIN V19 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[19]}]

set_property -dict {PACKAGE_PIN L22 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[1]}]

set_property -dict {PACKAGE_PIN L20 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[0]}]

set_property -dict {PACKAGE_PIN K25 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[3]}]

set_property -dict {PACKAGE_PIN L23 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[2]}]

set_property -dict {PACKAGE_PIN L24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[0]}]

set_property -dict {PACKAGE_PIN L25 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[1]}]

set_property -dict {PACKAGE_PIN M26 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[2]}]

set_property -dict {PACKAGE_PIN M25 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[3]}]

set_property -dict {PACKAGE_PIN N26 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[4]}]

set_property -dict {PACKAGE_PIN P24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[5]}]

set_property -dict {PACKAGE_PIN P26 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[6]}]

set_property -dict {PACKAGE_PIN P25 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[7]}]

set_property -dict {PACKAGE_PIN AA24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[8]}]

set_property -dict {PACKAGE_PIN Y23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[9]}]

set_property -dict {PACKAGE_PIN V21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[10]}]

set_property -dict {PACKAGE_PIN W24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[11]}]

set_property -dict {PACKAGE_PIN W23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[12]}]

set_property -dict {PACKAGE_PIN V22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[13]}]

set_property -dict {PACKAGE_PIN V23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[14]}]

set_property -dict {PACKAGE_PIN U21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[15]}]

set_property -dict {PACKAGE_PIN P21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[16]}]

set_property -dict {PACKAGE_PIN M21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[17]}]

set_property -dict {PACKAGE_PIN P23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[18]}]

set_property -dict {PACKAGE_PIN P19 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[19]}]

set_property -dict {PACKAGE_PIN N19 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[20]}]

set_property -dict {PACKAGE_PIN M20 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[21]}]

set_property -dict {PACKAGE_PIN N24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[22]}]

set_property -dict {PACKAGE_PIN N21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[23]}]

set_property -dict {PACKAGE_PIN T22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[24]}]

set_property -dict {PACKAGE_PIN R22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[25]}]

set_property -dict {PACKAGE_PIN R21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[26]}]

set_property -dict {PACKAGE_PIN P20 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[27]}]

set_property -dict {PACKAGE_PIN N22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[28]}]

set_property -dict {PACKAGE_PIN N23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[29]}]

set_property -dict {PACKAGE_PIN M24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[30]}]

set_property -dict {PACKAGE_PIN M22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[31]}]

set_property -dict {PACKAGE_PIN U19 IOSTANDARD LVCMOS33} [get_ports base_ram_ce_n]

set_property -dict {PACKAGE_PIN T20 IOSTANDARD LVCMOS33} [get_ports base_ram_oe_n]

set_property -dict {PACKAGE_PIN U20 IOSTANDARD LVCMOS33} [get_ports base_ram_we_n]

set_property -dict {PACKAGE_PIN AF25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[0]}]

set_property -dict {PACKAGE_PIN AE25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[1]}]

set_property -dict {PACKAGE_PIN AE26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[2]}]

set_property -dict {PACKAGE_PIN AD25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[3]}]

set_property -dict {PACKAGE_PIN AD26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[4]}]

set_property -dict {PACKAGE_PIN AC22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[5]}]

set_property -dict {PACKAGE_PIN Y17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[6]}]

set_property -dict {PACKAGE_PIN AA18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[7]}]

set_property -dict {PACKAGE_PIN AA17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[8]}]

set_property -dict {PACKAGE_PIN Y25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[9]}]

set_property -dict {PACKAGE_PIN AA25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[10]}]

set_property -dict {PACKAGE_PIN AB26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[11]}]

set_property -dict {PACKAGE_PIN AB25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[12]}]

set_property -dict {PACKAGE_PIN AC26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[13]}]

set_property -dict {PACKAGE_PIN AC24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[14]}]

set_property -dict {PACKAGE_PIN AF17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[15]}]

set_property -dict {PACKAGE_PIN AE17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[16]}]

set_property -dict {PACKAGE_PIN AF18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[17]}]

set_property -dict {PACKAGE_PIN AE18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[18]}]

set_property -dict {PACKAGE_PIN AF19 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[19]}]

set_property -dict {PACKAGE_PIN R25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[1]}]

set_property -dict {PACKAGE_PIN R26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[0]}]

set_property -dict {PACKAGE_PIN AB22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[3]}]

set_property -dict {PACKAGE_PIN AD24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[2]}]

set_property -dict {PACKAGE_PIN AF24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[0]}]

set_property -dict {PACKAGE_PIN AE23 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[1]}]

set_property -dict {PACKAGE_PIN AF23 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[2]}]

set_property -dict {PACKAGE_PIN AE22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[3]}]

set_property -dict {PACKAGE_PIN AF22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[4]}]

set_property -dict {PACKAGE_PIN AE21 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[5]}]

set_property -dict {PACKAGE_PIN AE20 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[6]}]

set_property -dict {PACKAGE_PIN AF20 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[7]}]

set_property -dict {PACKAGE_PIN Y26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[8]}]

set_property -dict {PACKAGE_PIN W25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[9]}]

set_property -dict {PACKAGE_PIN W26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[10]}]

set_property -dict {PACKAGE_PIN V24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[11]}]

set_property -dict {PACKAGE_PIN V26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[12]}]

set_property -dict {PACKAGE_PIN U25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[13]}]

set_property -dict {PACKAGE_PIN U26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[14]}]

set_property -dict {PACKAGE_PIN U24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[15]}]

set_property -dict {PACKAGE_PIN AB16 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[16]}]

set_property -dict {PACKAGE_PIN AC19 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[17]}]

set_property -dict {PACKAGE_PIN AB17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[18]}]

set_property -dict {PACKAGE_PIN AC18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[19]}]

set_property -dict {PACKAGE_PIN AD18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[20]}]

set_property -dict {PACKAGE_PIN AC16 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[21]}]

set_property -dict {PACKAGE_PIN Y15 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[22]}]

set_property -dict {PACKAGE_PIN AA15 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[23]}]

set_property -dict {PACKAGE_PIN AD17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[24]}]

set_property -dict {PACKAGE_PIN AC17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[25]}]

set_property -dict {PACKAGE_PIN AD20 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[26]}]

set_property -dict {PACKAGE_PIN AB21 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[27]}]

set_property -dict {PACKAGE_PIN AD21 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[28]}]

set_property -dict {PACKAGE_PIN AC21 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[29]}]

set_property -dict {PACKAGE_PIN AA19 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[30]}]

set_property -dict {PACKAGE_PIN AC23 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[31]}]

set_property -dict {PACKAGE_PIN AD23 IOSTANDARD LVCMOS33} [get_ports ext_ram_ce_n]

set_property -dict {PACKAGE_PIN AB19 IOSTANDARD LVCMOS33} [get_ports ext_ram_oe_n]

set_property -dict {PACKAGE_PIN AD19 IOSTANDARD LVCMOS33} [get_ports ext_ram_we_n]

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

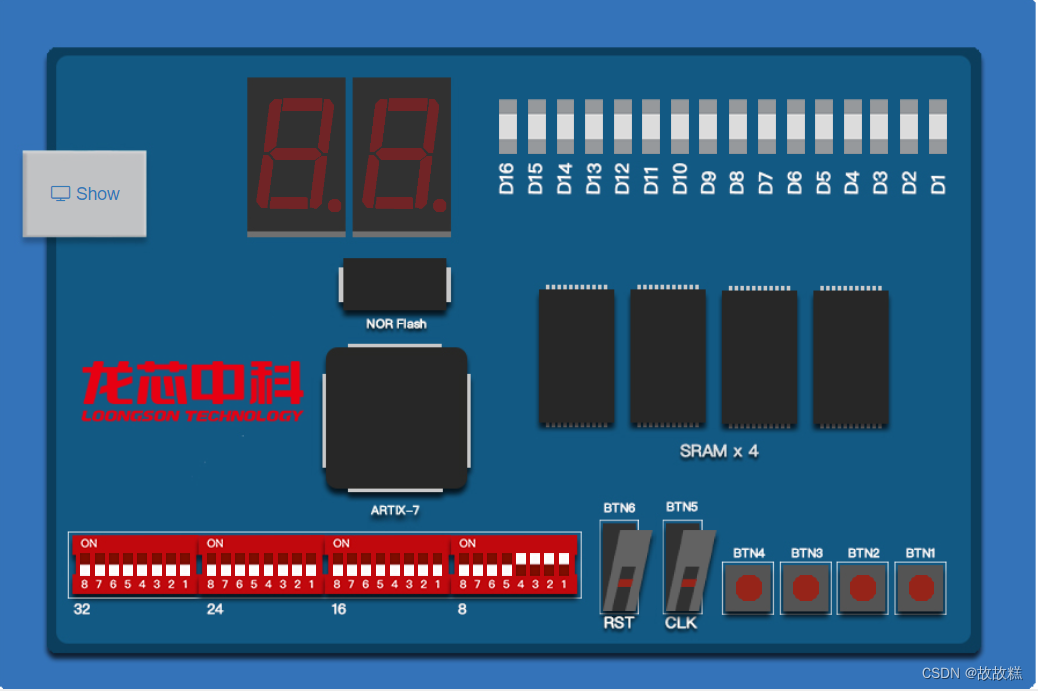

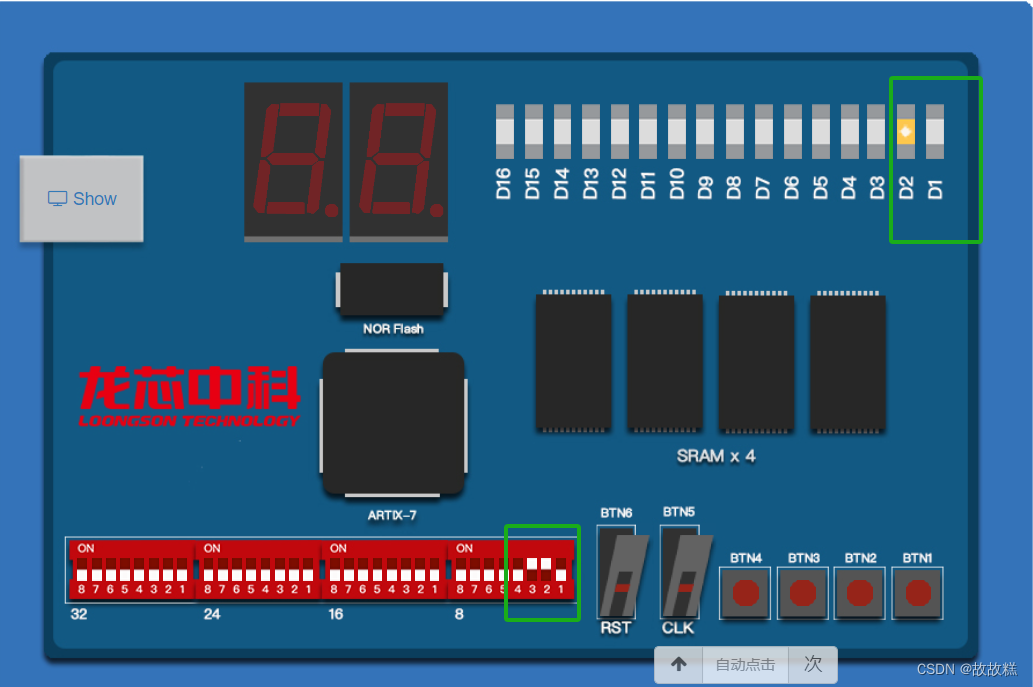

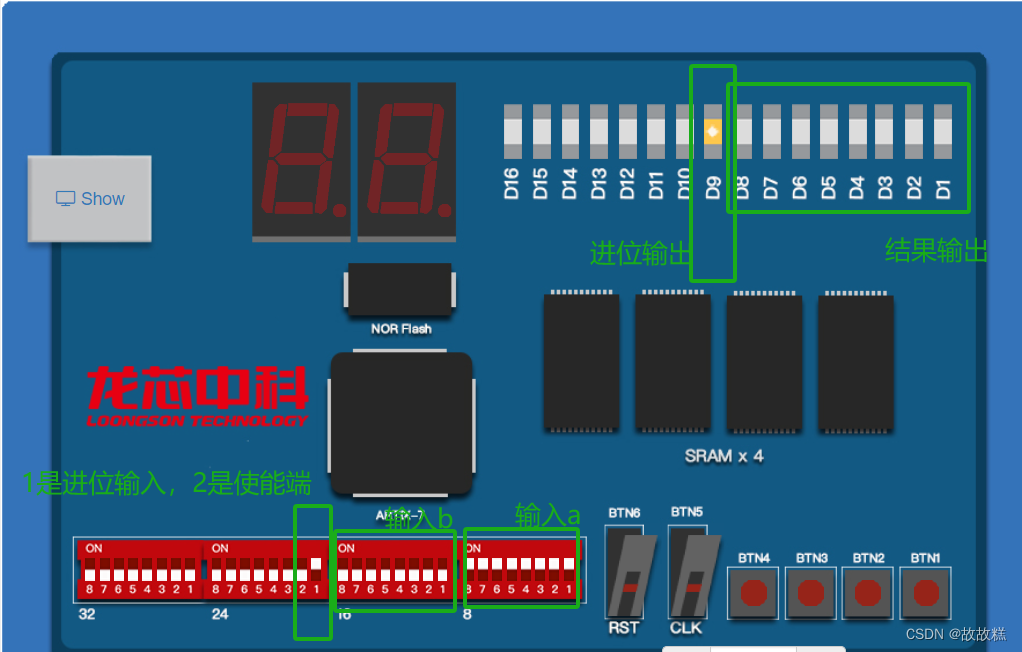

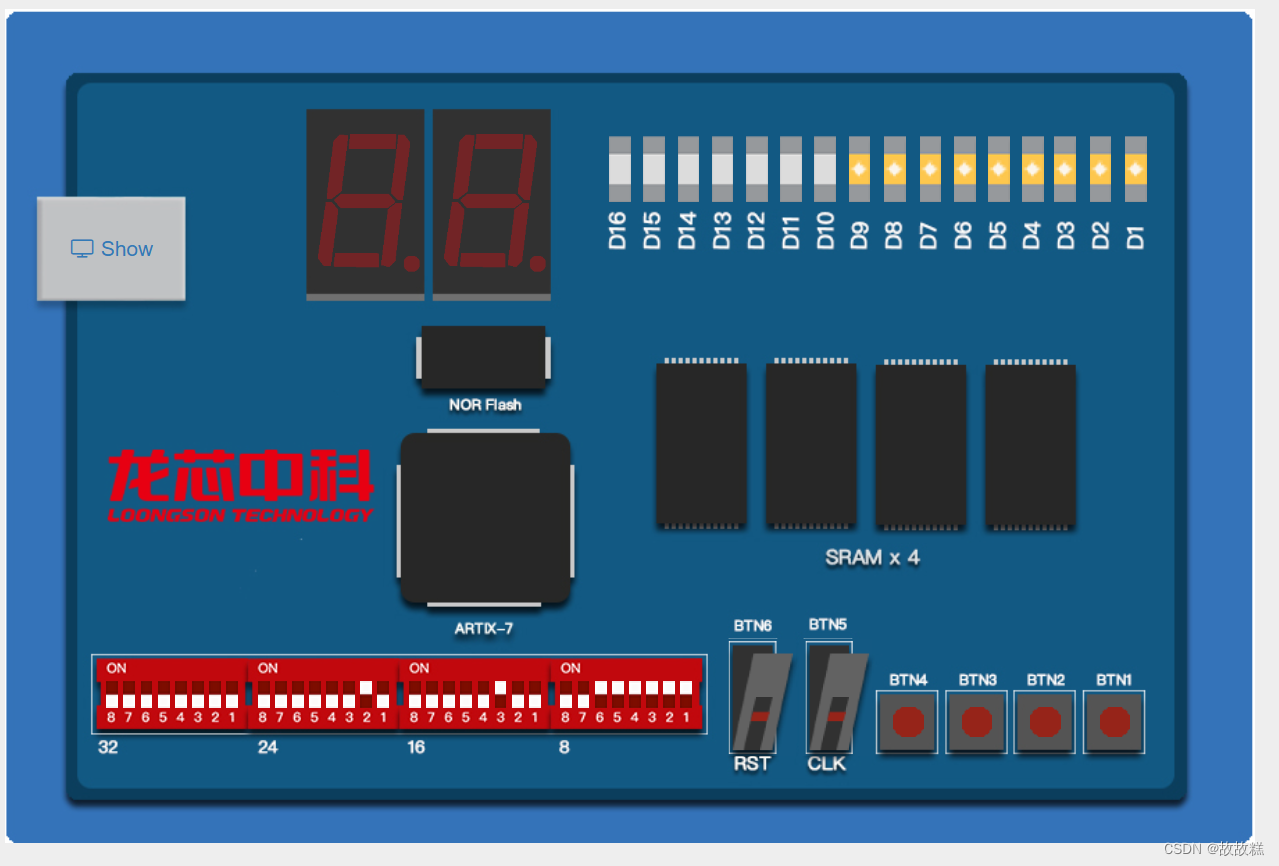

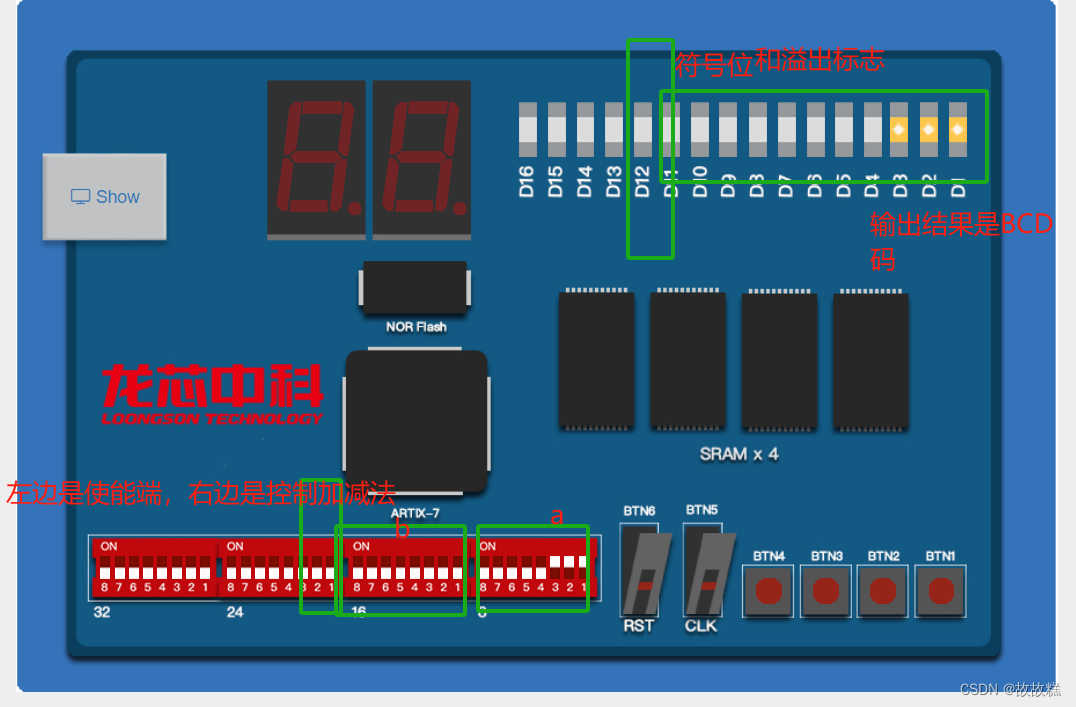

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]测试图

D1:代表sum,灯亮表示和为1

D2:代表 cout进位输出,灯亮表示进位为1

按钮1:enable使能输入,拨到下边代表有效(低有效)

按钮2:输入a拨上去代表b=1,即输入1

按钮3:输入b.拨上去代表b=1,即输入1

按钮4:进位输入cin,拨上去代表有进位输入1

例如:按钮1拨上边(使能输出为1,无效状态

),则加法器不工作,D1 D2灯不亮,

按钮1拨下边,表示加法器有效,按扭4拨上代表进位为1,而按钮23拨下边代表两个二进制输入都是0,则输出sum=1,D1灯亮,没有进位输出,则D2灯不亮

按钮1拨下边,表示加法器有效,按扭4拨下代表进位为0,而按钮23波上边代表两个二进制输入都是1,则输出sum=0,D1不亮,有进位输出,则D2灯亮

按钮1拨下边,表示加法器有效,按扭4拨上代表进位为1,而按钮23波上边代表两个二进制输入都是1,则输出sum=1,D1亮,有进位输出,则D2灯亮

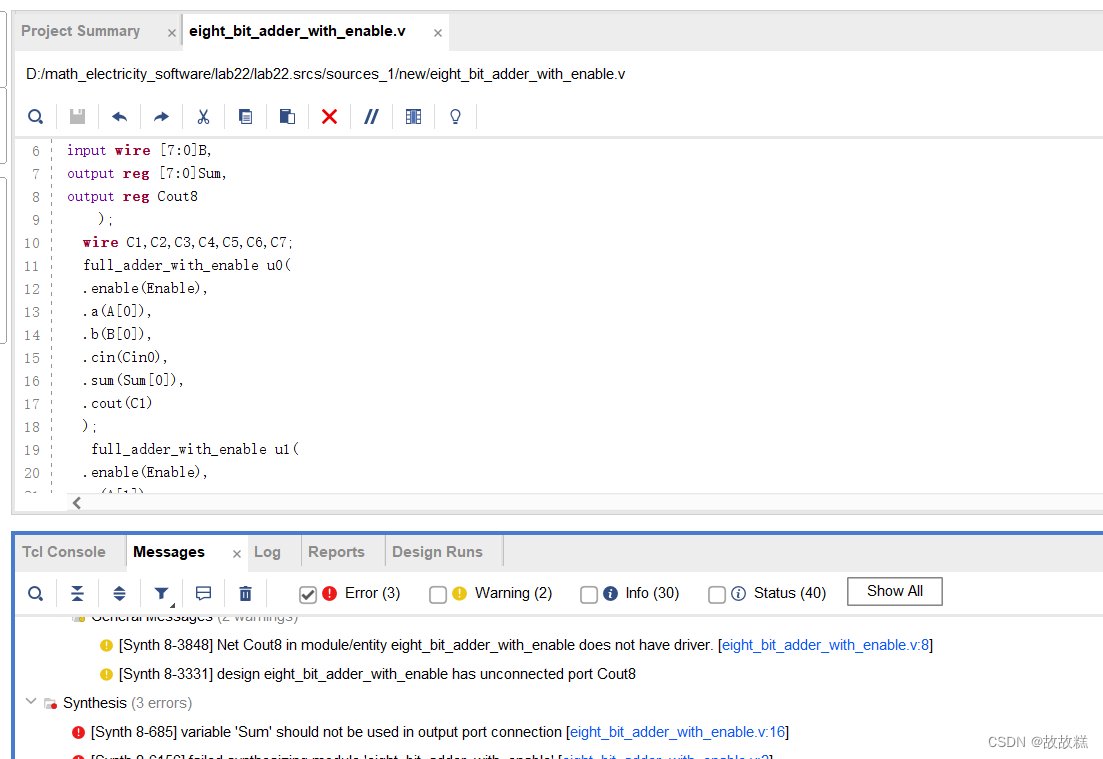

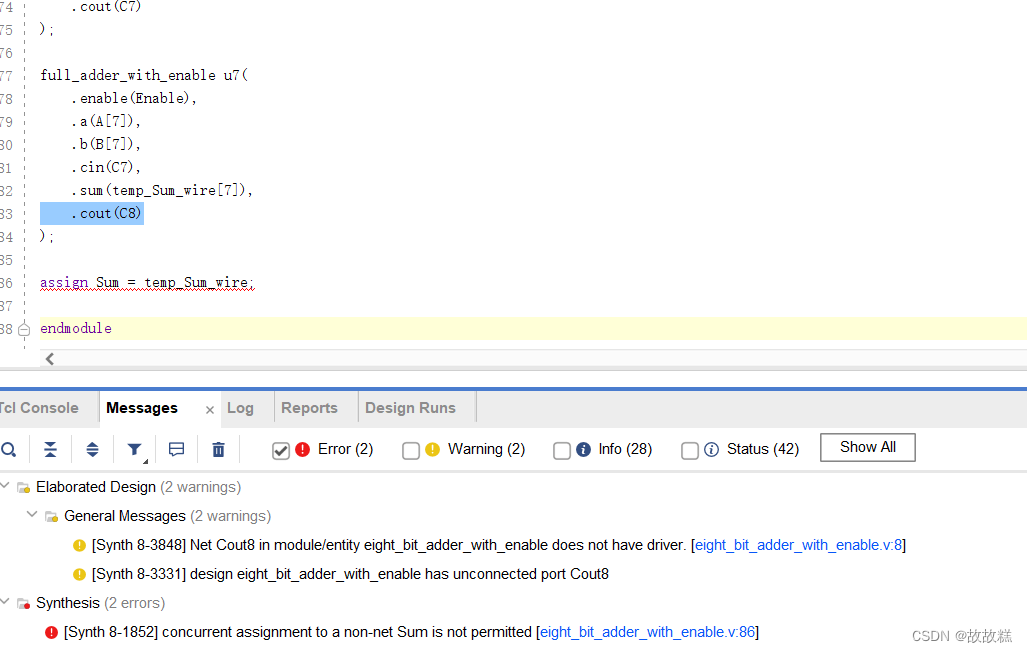

(2) 由1位全加器级联8位加法器

(a) 工作原理

全加器接收两个1位二进制数(A和B)和一个进位输入(Cin),并产生一个1位和(Sum)以及一个进位输出(Cout)。

现在,为了构建一个8位加法器,我们需要将8个全加器级联起来。每一位的全加器都会接收两个输入位(来自A和B)和一个进位输入(对于最低位是全0,对于其他位则是来自前一级全加器的Cout)。

(b) Verilog源程序

`timescale 1ns / 1ps

module eight_bit_adder_with_enable(

input wire Cin0,

input wire Enable,

input wire [7:0] A,

input wire [7:0] B,

output reg [7:0] Sum,

output wire Cout8

);

wire [7:0] temp_Sum_wire;

wire C1, C2, C3, C4, C5, C6, C7;

full_adder_with_enable u0(

.enable(Enable),

.a(A[0]),

.b(B[0]),

.cin(Cin0),

.sum(temp_Sum_wire[0]),

.cout(C1)

);

full_adder_with_enable u1(

.enable(Enable),

.a(A[1]),

.b(B[1]),

.cin(C1),

.sum(temp_Sum_wire[1]),

.cout(C2)

);

full_adder_with_enable u2(

.enable(Enable),

.a(A[2]),

.b(B[2]),

.cin(C2),

.sum(temp_Sum_wire[2]),

.cout(C3)

);

full_adder_with_enable u3(

.enable(Enable),

.a(A[3]),

.b(B[3]),

.cin(C3),

.sum(temp_Sum_wire[3]),

.cout(C4)

);

full_adder_with_enable u4(

.enable(Enable),

.a(A[4]),

.b(B[4]),

.cin(C4),

.sum(temp_Sum_wire[4]),

.cout(C5)

);

full_adder_with_enable u5(

.enable(Enable),

.a(A[5]),

.b(B[5]),

.cin(C5),

.sum(temp_Sum_wire[5]),

.cout(C6)

);

full_adder_with_enable u6(

.enable(Enable),

.a(A[6]),

.b(B[6]),

.cin(C6),

.sum(temp_Sum_wire[6]),

.cout(C7)

);

full_adder_with_enable u7(

.enable(Enable),

.a(A[7]),

.b(B[7]),

.cin(C7),

.sum(temp_Sum_wire[7]),

.cout(Cout8)

);

always @* begin

if (!Enable)

Sum = temp_Sum_wire;

else

Sum = 8'bz; // or any other default value

end

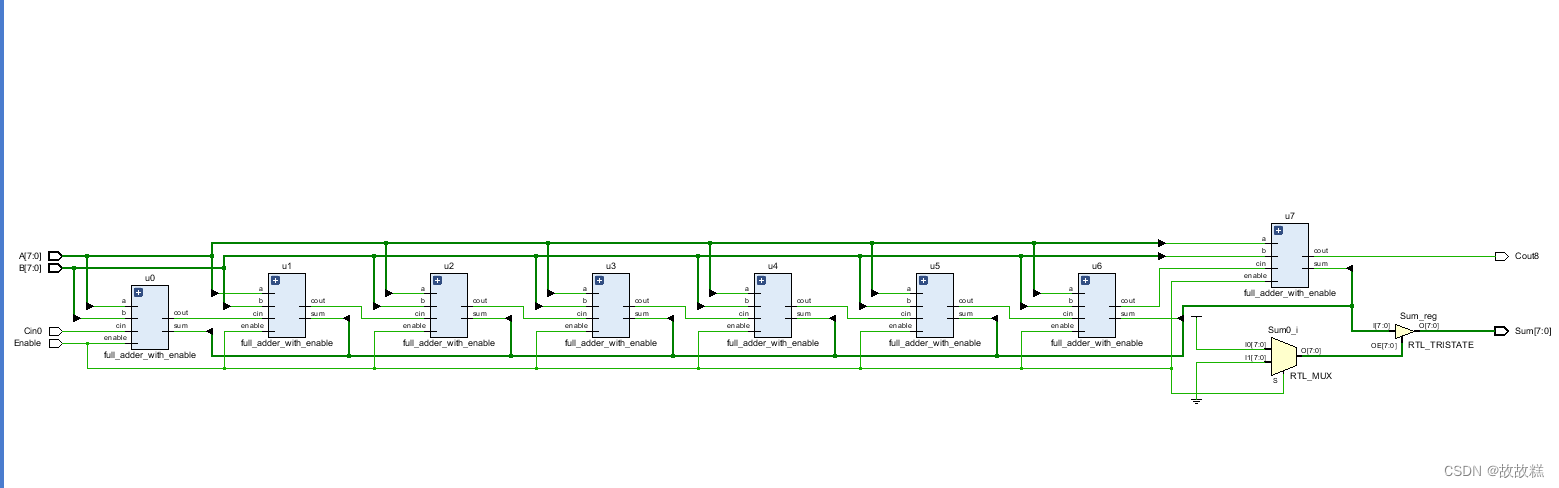

endmodule(c) RTL视图

(d) ModelSim源程序

`timescale 1ns / 1ps

module eight_bit_adder_with_enable_tb;

reg Cin0, Enable;

reg [7:0] A, B;

wire [7:0] Sum;

wire Cout8;

// Instantiate the DUT

eight_bit_adder_with_enable dut (

.Cin0(Cin0),

.Enable(Enable),

.A(A),

.B(B),

.Sum(Sum),

.Cout8(Cout8)

);

// Stimulus generation

initial begin

Cin0 = 0;

Enable = 1;

A = 8'b00000000;

B = 8'b00000001;

#10;

Cin0 = 0;

Enable = 0;

A = 8'b00000000;

B = 8'b00000001;

#10;

Cin0 = 0;

Enable = 0;

A = 8'b11111111;

B = 8'b00000001;

#10;

Cin0 =1;

Enable = 0;

A = 8'b11111111;

B = 8'b00000000;

#10;

// End simulation

$finish;

end

// Display results

always @(Sum or Cout8) begin

$display("Sum = %b, Cout8 = %b", Sum, Cout8);

end

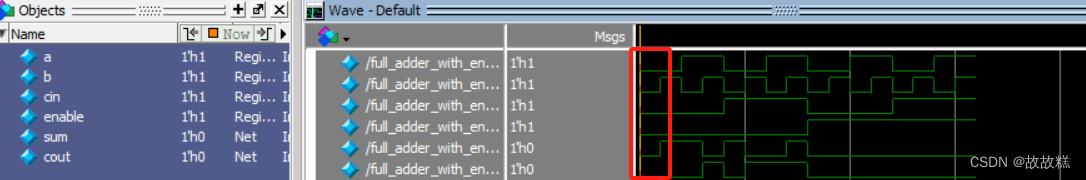

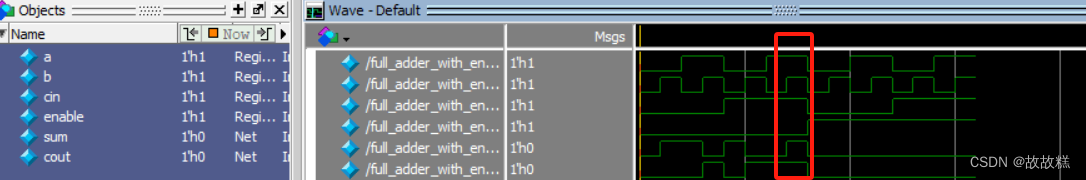

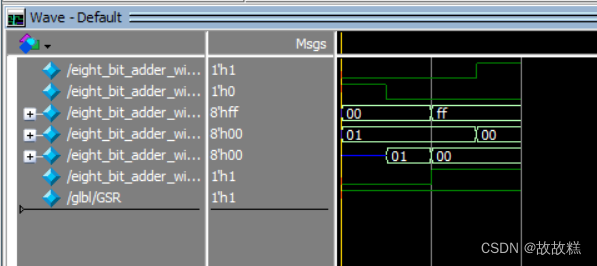

endmodule(d) ModelSim仿真结果

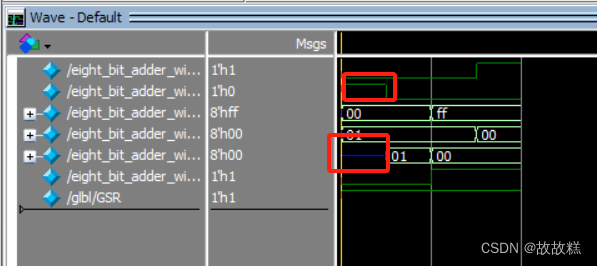

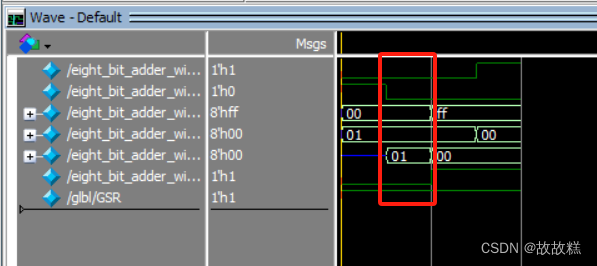

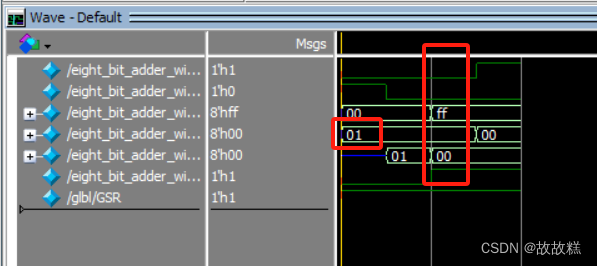

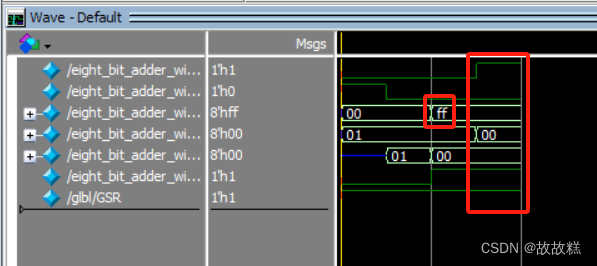

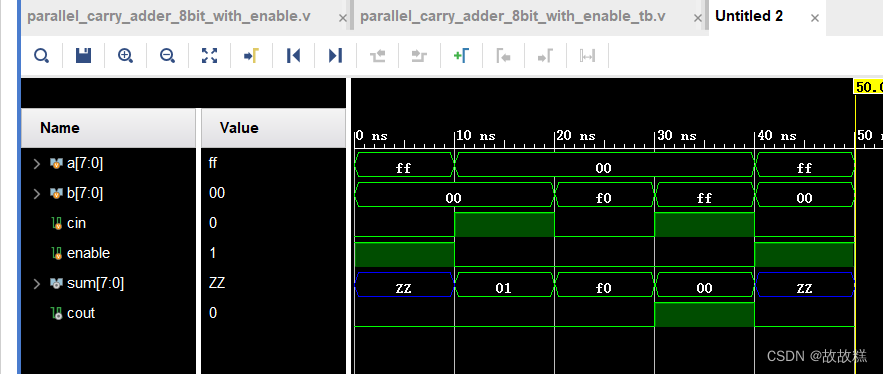

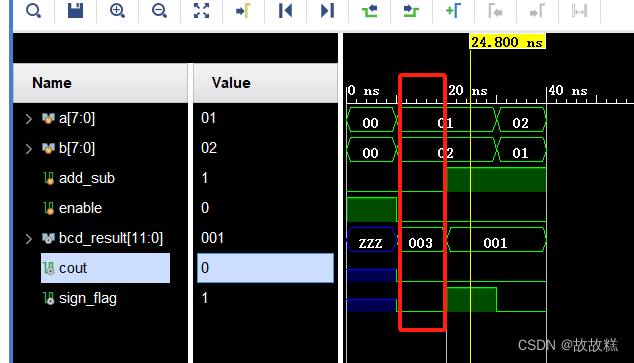

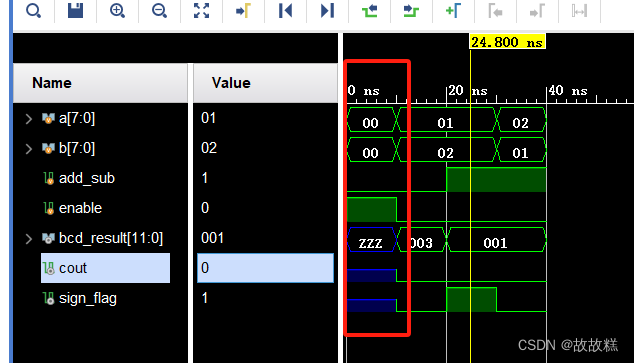

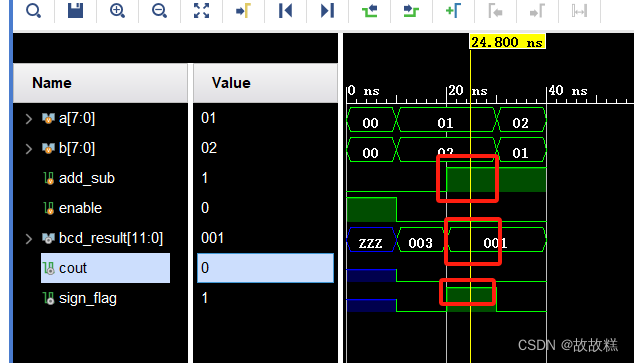

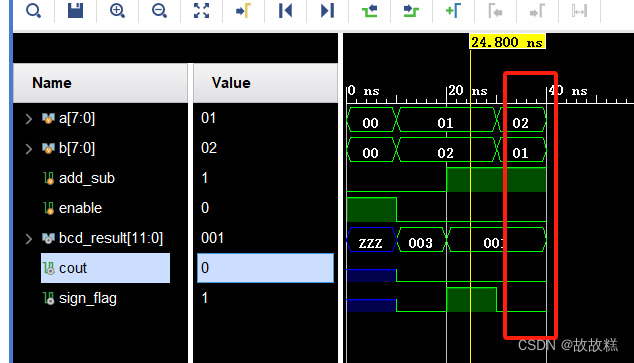

下面是具体分析:

进位输入Cin,使能输入Enable,八位二进制A和B,输出和Sum,进位输出Cout

在源文件中我们分别让:

(1)

Cin0 = 0;

Enable = 1;

A = 8'b00000000;

B = 8'b00000001;

#10;

当使能端Enable输入高电平,此时处于无效状态,输出为高阻态

(2)

Cin0 = 0;

Enable = 0;

A = 8'b00000000;

B = 8'b00000001;

#10;

当使能端Enable输入低电平,此时处于有效状态,,此时输入A=00000000,B=00000001进位输入Cin=0(低电平),输出Sum为00000001,进位输出为Cout8=0(低电平)

(3)

Cin0 = 0;

Enable = 0;

A = 8'b11111111;

B = 8'b00000001;

#10;

当使能端Enable输入低电平,此时处于有效状态,,此时输入A=11111111,B=00000001,进位输入Cin=0(低电平),输出Sum为00000000,进位输出为Cout8=1(高电平)

Cin0 =1;

Enable = 0;

A = 8'b11111111;

B = 8'b00000000;

#10;

当使能端Enable输入低电平,此时处于有效状态,,此时输入A=11111111,B=00000000,进位输入Cin=1(高电平),输出Sum为00000000,进位输出为Cout8=1(高电平)

(e) 下载测试结

管脚配置

#Clock

set_property -dict {PACKAGE_PIN K21 IOSTANDARD LVCMOS33} [get_ports clk_50M] ;#50MHz main clock in

set_property -dict {PACKAGE_PIN H21 IOSTANDARD LVCMOS33} [get_ports clk_11M0592] ;#11.0592MHz clock for UART

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clk_11M0592_IBUF]

create_clock -period 20.000 -name clk_50M -waveform {0.000 10.000} [get_ports clk_50M]

create_clock -period 90.422 -name clk_11M0592 -waveform {0.000 45.211} [get_ports clk_11M0592]

#Touch Button

set_property -dict {PACKAGE_PIN T2 IOSTANDARD LVCMOS33} [get_ports touch_btn[0]] ;#BTN1

set_property -dict {PACKAGE_PIN M1 IOSTANDARD LVCMOS33} [get_ports touch_btn[1]] ;#BTN2

set_property -dict {PACKAGE_PIN P3 IOSTANDARD LVCMOS33} [get_ports touch_btn[2]] ;#BTN3

set_property -dict {PACKAGE_PIN U2 IOSTANDARD LVCMOS33} [get_ports touch_btn[3]] ;#BTN4

set_property -dict {PACKAGE_PIN U1 IOSTANDARD LVCMOS33} [get_ports clock_btn] ;#BTN5

set_property -dict {PACKAGE_PIN U5 IOSTANDARD LVCMOS33} [get_ports reset_btn] ;#BTN6

#required if touch button used as manual clock source

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clock_btn_IBUF]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets reset_btn_IBUF]

#CPLD GPIO 12-16

#set_property -dict {PACKAGE_PIN J14 IOSTANDARD LVCMOS33} [get_ports {uart_wrn}]

#set_property -dict {PACKAGE_PIN L14 IOSTANDARD LVCMOS33} [get_ports {uart_rdn}]

#set_property -dict {PACKAGE_PIN J15 IOSTANDARD LVCMOS33} [get_ports {uart_tbre}]

#set_property -dict {PACKAGE_PIN K15 IOSTANDARD LVCMOS33} [get_ports {uart_tsre}]

#set_property -dict {PACKAGE_PIN L15 IOSTANDARD LVCMOS33} [get_ports {uart_dataready}]

#Ext serial

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN H18} [get_ports txd] ;#GPIO5

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN J20} [get_ports rxd] ;#GPIO6

#Digital Video

set_property -dict {PACKAGE_PIN H22 IOSTANDARD LVCMOS33} [get_ports video_clk]

set_property -dict {PACKAGE_PIN E26 IOSTANDARD LVCMOS33} [get_ports {video_red[2]}]

set_property -dict {PACKAGE_PIN F24 IOSTANDARD LVCMOS33} [get_ports {video_red[1]}]

set_property -dict {PACKAGE_PIN K23 IOSTANDARD LVCMOS33} [get_ports {video_red[0]}]

set_property -dict {PACKAGE_PIN F23 IOSTANDARD LVCMOS33} [get_ports {video_green[2]}]

set_property -dict {PACKAGE_PIN E23 IOSTANDARD LVCMOS33} [get_ports {video_green[1]}]

set_property -dict {PACKAGE_PIN K22 IOSTANDARD LVCMOS33} [get_ports {video_green[0]}]

set_property -dict {PACKAGE_PIN D25 IOSTANDARD LVCMOS33} [get_ports {video_blue[1]}]

set_property -dict {PACKAGE_PIN E25 IOSTANDARD LVCMOS33} [get_ports {video_blue[0]}]

set_property -dict {PACKAGE_PIN J24 IOSTANDARD LVCMOS33} [get_ports video_hsync]

set_property -dict {PACKAGE_PIN H24 IOSTANDARD LVCMOS33} [get_ports video_vsync]

set_property -dict {PACKAGE_PIN G24 IOSTANDARD LVCMOS33} [get_ports video_de]

#LEDS

set_property -dict {PACKAGE_PIN B24 IOSTANDARD LVCMOS33} [get_ports Sum[0]]

set_property -dict {PACKAGE_PIN E21 IOSTANDARD LVCMOS33} [get_ports Sum[1]]

set_property -dict {PACKAGE_PIN A24 IOSTANDARD LVCMOS33} [get_ports Sum[2]]

set_property -dict {PACKAGE_PIN D23 IOSTANDARD LVCMOS33} [get_ports Sum[3]]

set_property -dict {PACKAGE_PIN C22 IOSTANDARD LVCMOS33} [get_ports Sum[4]]

set_property -dict {PACKAGE_PIN C21 IOSTANDARD LVCMOS33} [get_ports Sum[5]]

set_property -dict {PACKAGE_PIN E20 IOSTANDARD LVCMOS33} [get_ports Sum[6]]

set_property -dict {PACKAGE_PIN B22 IOSTANDARD LVCMOS33} [get_ports Sum[7]]

set_property -dict {PACKAGE_PIN C23 IOSTANDARD LVCMOS33} [get_ports Cout8]

set_property -dict {PACKAGE_PIN A23 IOSTANDARD LVCMOS33} [get_ports {leds[9]}]

set_property -dict {PACKAGE_PIN D21 IOSTANDARD LVCMOS33} [get_ports {leds[10]}]

set_property -dict {PACKAGE_PIN A18 IOSTANDARD LVCMOS33} [get_ports {leds[11]}]

set_property -dict {PACKAGE_PIN D20 IOSTANDARD LVCMOS33} [get_ports {leds[12]}]

set_property -dict {PACKAGE_PIN A22 IOSTANDARD LVCMOS33} [get_ports {leds[13]}]

set_property -dict {PACKAGE_PIN A20 IOSTANDARD LVCMOS33} [get_ports {leds[14]}]

set_property -dict {PACKAGE_PIN B20 IOSTANDARD LVCMOS33} [get_ports {leds[15]}]

#DPY0

set_property -dict {PACKAGE_PIN B19 IOSTANDARD LVCMOS33} [get_ports {dpy0[0]}]

set_property -dict {PACKAGE_PIN D19 IOSTANDARD LVCMOS33} [get_ports {dpy0[1]}]

set_property -dict {PACKAGE_PIN B21 IOSTANDARD LVCMOS33} [get_ports {dpy0[2]}]

set_property -dict {PACKAGE_PIN A19 IOSTANDARD LVCMOS33} [get_ports {dpy0[3]}]

set_property -dict {PACKAGE_PIN E18 IOSTANDARD LVCMOS33} [get_ports {dpy0[4]}]

set_property -dict {PACKAGE_PIN C19 IOSTANDARD LVCMOS33} [get_ports {dpy0[5]}]

set_property -dict {PACKAGE_PIN B17 IOSTANDARD LVCMOS33} [get_ports {dpy0[6]}]

set_property -dict {PACKAGE_PIN C17 IOSTANDARD LVCMOS33} [get_ports {dpy0[7]}]

#DPY1

set_property -dict {PACKAGE_PIN A17 IOSTANDARD LVCMOS33} [get_ports {dpy1[0]}]

set_property -dict {PACKAGE_PIN D16 IOSTANDARD LVCMOS33} [get_ports {dpy1[1]}]

set_property -dict {PACKAGE_PIN E17 IOSTANDARD LVCMOS33} [get_ports {dpy1[2]}]

set_property -dict {PACKAGE_PIN F17 IOSTANDARD LVCMOS33} [get_ports {dpy1[3]}]

set_property -dict {PACKAGE_PIN E16 IOSTANDARD LVCMOS33} [get_ports {dpy1[4]}]

set_property -dict {PACKAGE_PIN G16 IOSTANDARD LVCMOS33} [get_ports {dpy1[5]}]

set_property -dict {PACKAGE_PIN F15 IOSTANDARD LVCMOS33} [get_ports {dpy1[6]}]

set_property -dict {PACKAGE_PIN G17 IOSTANDARD LVCMOS33} [get_ports {dpy1[7]}]

#DIP_SW

set_property -dict {PACKAGE_PIN T3 IOSTANDARD LVCMOS33} [get_ports A[0]]

set_property -dict {PACKAGE_PIN J3 IOSTANDARD LVCMOS33} [get_ports A[1]]

set_property -dict {PACKAGE_PIN M2 IOSTANDARD LVCMOS33} [get_ports A[2]]

set_property -dict {PACKAGE_PIN P1 IOSTANDARD LVCMOS33} [get_ports A[3]]

set_property -dict {PACKAGE_PIN P4 IOSTANDARD LVCMOS33} [get_ports A[4]]

set_property -dict {PACKAGE_PIN L5 IOSTANDARD LVCMOS33} [get_ports A[5]]

set_property -dict {PACKAGE_PIN L3 IOSTANDARD LVCMOS33} [get_ports A[6]]

set_property -dict {PACKAGE_PIN N6 IOSTANDARD LVCMOS33} [get_ports A[7]]

set_property -dict {PACKAGE_PIN M6 IOSTANDARD LVCMOS33} [get_ports B[0]]

set_property -dict {PACKAGE_PIN N7 IOSTANDARD LVCMOS33} [get_ports B[1]]

set_property -dict {PACKAGE_PIN M7 IOSTANDARD LVCMOS33} [get_ports B[2]]

set_property -dict {PACKAGE_PIN L7 IOSTANDARD LVCMOS33} [get_ports B[3]]

set_property -dict {PACKAGE_PIN M5 IOSTANDARD LVCMOS33} [get_ports B[4]]

set_property -dict {PACKAGE_PIN K3 IOSTANDARD LVCMOS33} [get_ports B[5]]

set_property -dict {PACKAGE_PIN J1 IOSTANDARD LVCMOS33} [get_ports B[6]]

set_property -dict {PACKAGE_PIN L2 IOSTANDARD LVCMOS33} [get_ports B[7]]

set_property -dict {PACKAGE_PIN K2 IOSTANDARD LVCMOS33} [get_ports Cin0]

set_property -dict {PACKAGE_PIN K1 IOSTANDARD LVCMOS33} [get_ports Enable]

set_property -dict {PACKAGE_PIN N3 IOSTANDARD LVCMOS33} [get_ports {dip_sw[18]}]

set_property -dict {PACKAGE_PIN L4 IOSTANDARD LVCMOS33} [get_ports {dip_sw[19]}]

set_property -dict {PACKAGE_PIN M4 IOSTANDARD LVCMOS33} [get_ports {dip_sw[20]}]

set_property -dict {PACKAGE_PIN N2 IOSTANDARD LVCMOS33} [get_ports {dip_sw[21]}]

set_property -dict {PACKAGE_PIN P6 IOSTANDARD LVCMOS33} [get_ports {dip_sw[22]}]

set_property -dict {PACKAGE_PIN N1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[23]}]

set_property -dict {PACKAGE_PIN P5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[24]}]

set_property -dict {PACKAGE_PIN R3 IOSTANDARD LVCMOS33} [get_ports {dip_sw[25]}]

set_property -dict {PACKAGE_PIN T4 IOSTANDARD LVCMOS33} [get_ports {dip_sw[26]}]

set_property -dict {PACKAGE_PIN R1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[27]}]

set_property -dict {PACKAGE_PIN R5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[28]}]

set_property -dict {PACKAGE_PIN T5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[29]}]

set_property -dict {PACKAGE_PIN R6 IOSTANDARD LVCMOS33} [get_ports {dip_sw[30]}]

set_property -dict {PACKAGE_PIN R2 IOSTANDARD LVCMOS33} [get_ports {dip_sw[31]}]

set_property -dict {PACKAGE_PIN C2 IOSTANDARD LVCMOS33} [get_ports {flash_a[0]}]

set_property -dict {PACKAGE_PIN H9 IOSTANDARD LVCMOS33} [get_ports {flash_a[1]}]

set_property -dict {PACKAGE_PIN H8 IOSTANDARD LVCMOS33} [get_ports {flash_a[2]}]

set_property -dict {PACKAGE_PIN G9 IOSTANDARD LVCMOS33} [get_ports {flash_a[3]}]

set_property -dict {PACKAGE_PIN H7 IOSTANDARD LVCMOS33} [get_ports {flash_a[4]}]

set_property -dict {PACKAGE_PIN F8 IOSTANDARD LVCMOS33} [get_ports {flash_a[5]}]

set_property -dict {PACKAGE_PIN G8 IOSTANDARD LVCMOS33} [get_ports {flash_a[6]}]

set_property -dict {PACKAGE_PIN K7 IOSTANDARD LVCMOS33} [get_ports {flash_a[7]}]

set_property -dict {PACKAGE_PIN G7 IOSTANDARD LVCMOS33} [get_ports {flash_a[8]}]

set_property -dict {PACKAGE_PIN F7 IOSTANDARD LVCMOS33} [get_ports {flash_a[9]}]

set_property -dict {PACKAGE_PIN E6 IOSTANDARD LVCMOS33} [get_ports {flash_a[10]}]

set_property -dict {PACKAGE_PIN D6 IOSTANDARD LVCMOS33} [get_ports {flash_a[11]}]

set_property -dict {PACKAGE_PIN F5 IOSTANDARD LVCMOS33} [get_ports {flash_a[12]}]

set_property -dict {PACKAGE_PIN E3 IOSTANDARD LVCMOS33} [get_ports {flash_a[13]}]

set_property -dict {PACKAGE_PIN G5 IOSTANDARD LVCMOS33} [get_ports {flash_a[14]}]

set_property -dict {PACKAGE_PIN F4 IOSTANDARD LVCMOS33} [get_ports {flash_a[15]}]

set_property -dict {PACKAGE_PIN H6 IOSTANDARD LVCMOS33} [get_ports {flash_a[16]}]

set_property -dict {PACKAGE_PIN G4 IOSTANDARD LVCMOS33} [get_ports {flash_a[17]}]

set_property -dict {PACKAGE_PIN J6 IOSTANDARD LVCMOS33} [get_ports {flash_a[18]}]

set_property -dict {PACKAGE_PIN H4 IOSTANDARD LVCMOS33} [get_ports {flash_a[19]}]

set_property -dict {PACKAGE_PIN J5 IOSTANDARD LVCMOS33} [get_ports {flash_a[20]}]

set_property -dict {PACKAGE_PIN J4 IOSTANDARD LVCMOS33} [get_ports {flash_a[21]}]

set_property -dict {PACKAGE_PIN K6 IOSTANDARD LVCMOS33} [get_ports {flash_a[22]}]

set_property -dict {PACKAGE_PIN D4 IOSTANDARD LVCMOS33} [get_ports {flash_d[0]}]

set_property -dict {PACKAGE_PIN C1 IOSTANDARD LVCMOS33} [get_ports {flash_d[1]}]

set_property -dict {PACKAGE_PIN D1 IOSTANDARD LVCMOS33} [get_ports {flash_d[2]}]

set_property -dict {PACKAGE_PIN E1 IOSTANDARD LVCMOS33} [get_ports {flash_d[3]}]

set_property -dict {PACKAGE_PIN G1 IOSTANDARD LVCMOS33} [get_ports {flash_d[4]}]

set_property -dict {PACKAGE_PIN A2 IOSTANDARD LVCMOS33} [get_ports {flash_d[5]}]

set_property -dict {PACKAGE_PIN C3 IOSTANDARD LVCMOS33} [get_ports {flash_d[6]}]

set_property -dict {PACKAGE_PIN B4 IOSTANDARD LVCMOS33} [get_ports {flash_d[7]}]

set_property -dict {PACKAGE_PIN D3 IOSTANDARD LVCMOS33} [get_ports {flash_d[8]}]

set_property -dict {PACKAGE_PIN E2 IOSTANDARD LVCMOS33} [get_ports {flash_d[9]}]

set_property -dict {PACKAGE_PIN F3 IOSTANDARD LVCMOS33} [get_ports {flash_d[10]}]

set_property -dict {PACKAGE_PIN F2 IOSTANDARD LVCMOS33} [get_ports {flash_d[11]}]

set_property -dict {PACKAGE_PIN G2 IOSTANDARD LVCMOS33} [get_ports {flash_d[12]}]

set_property -dict {PACKAGE_PIN B2 IOSTANDARD LVCMOS33} [get_ports {flash_d[13]}]

set_property -dict {PACKAGE_PIN A3 IOSTANDARD LVCMOS33} [get_ports {flash_d[14]}]

set_property -dict {PACKAGE_PIN A4 IOSTANDARD LVCMOS33} [get_ports {flash_d[15]}]

set_property -dict {PACKAGE_PIN B1 IOSTANDARD LVCMOS33} [get_ports flash_byte_n]

set_property -dict {PACKAGE_PIN E5 IOSTANDARD LVCMOS33} [get_ports flash_ce_n ]

set_property -dict {PACKAGE_PIN A5 IOSTANDARD LVCMOS33} [get_ports flash_oe_n ]

set_property -dict {PACKAGE_PIN G6 IOSTANDARD LVCMOS33} [get_ports flash_rp_n ]

set_property -dict {PACKAGE_PIN D5 IOSTANDARD LVCMOS33} [get_ports flash_vpen ]

set_property -dict {PACKAGE_PIN B5 IOSTANDARD LVCMOS33} [get_ports flash_we_n ]

set_property -dict {PACKAGE_PIN T19 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[0]}]

set_property -dict {PACKAGE_PIN V18 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[1]}]

set_property -dict {PACKAGE_PIN T18 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[2]}]

set_property -dict {PACKAGE_PIN V17 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[3]}]

set_property -dict {PACKAGE_PIN U17 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[4]}]

set_property -dict {PACKAGE_PIN R20 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[5]}]

set_property -dict {PACKAGE_PIN R23 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[6]}]

set_property -dict {PACKAGE_PIN T23 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[7]}]

set_property -dict {PACKAGE_PIN U22 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[8]}]

set_property -dict {PACKAGE_PIN Y22 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[9]}]

set_property -dict {PACKAGE_PIN AB24 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[10]}]

set_property -dict {PACKAGE_PIN AA23 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[11]}]

set_property -dict {PACKAGE_PIN Y21 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[12]}]

set_property -dict {PACKAGE_PIN Y20 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[13]}]

set_property -dict {PACKAGE_PIN AA22 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[14]}]

set_property -dict {PACKAGE_PIN W19 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[15]}]

set_property -dict {PACKAGE_PIN W21 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[16]}]

set_property -dict {PACKAGE_PIN W20 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[17]}]

set_property -dict {PACKAGE_PIN W18 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[18]}]

set_property -dict {PACKAGE_PIN V19 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[19]}]

set_property -dict {PACKAGE_PIN L22 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[1]}]

set_property -dict {PACKAGE_PIN L20 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[0]}]

set_property -dict {PACKAGE_PIN K25 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[3]}]

set_property -dict {PACKAGE_PIN L23 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[2]}]

set_property -dict {PACKAGE_PIN L24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[0]}]

set_property -dict {PACKAGE_PIN L25 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[1]}]

set_property -dict {PACKAGE_PIN M26 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[2]}]

set_property -dict {PACKAGE_PIN M25 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[3]}]

set_property -dict {PACKAGE_PIN N26 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[4]}]

set_property -dict {PACKAGE_PIN P24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[5]}]

set_property -dict {PACKAGE_PIN P26 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[6]}]

set_property -dict {PACKAGE_PIN P25 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[7]}]

set_property -dict {PACKAGE_PIN AA24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[8]}]

set_property -dict {PACKAGE_PIN Y23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[9]}]

set_property -dict {PACKAGE_PIN V21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[10]}]

set_property -dict {PACKAGE_PIN W24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[11]}]

set_property -dict {PACKAGE_PIN W23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[12]}]

set_property -dict {PACKAGE_PIN V22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[13]}]

set_property -dict {PACKAGE_PIN V23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[14]}]

set_property -dict {PACKAGE_PIN U21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[15]}]

set_property -dict {PACKAGE_PIN P21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[16]}]

set_property -dict {PACKAGE_PIN M21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[17]}]

set_property -dict {PACKAGE_PIN P23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[18]}]

set_property -dict {PACKAGE_PIN P19 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[19]}]

set_property -dict {PACKAGE_PIN N19 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[20]}]

set_property -dict {PACKAGE_PIN M20 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[21]}]

set_property -dict {PACKAGE_PIN N24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[22]}]

set_property -dict {PACKAGE_PIN N21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[23]}]

set_property -dict {PACKAGE_PIN T22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[24]}]

set_property -dict {PACKAGE_PIN R22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[25]}]

set_property -dict {PACKAGE_PIN R21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[26]}]

set_property -dict {PACKAGE_PIN P20 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[27]}]

set_property -dict {PACKAGE_PIN N22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[28]}]

set_property -dict {PACKAGE_PIN N23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[29]}]

set_property -dict {PACKAGE_PIN M24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[30]}]

set_property -dict {PACKAGE_PIN M22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[31]}]

set_property -dict {PACKAGE_PIN U19 IOSTANDARD LVCMOS33} [get_ports base_ram_ce_n]

set_property -dict {PACKAGE_PIN T20 IOSTANDARD LVCMOS33} [get_ports base_ram_oe_n]

set_property -dict {PACKAGE_PIN U20 IOSTANDARD LVCMOS33} [get_ports base_ram_we_n]

set_property -dict {PACKAGE_PIN AF25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[0]}]

set_property -dict {PACKAGE_PIN AE25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[1]}]

set_property -dict {PACKAGE_PIN AE26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[2]}]

set_property -dict {PACKAGE_PIN AD25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[3]}]

set_property -dict {PACKAGE_PIN AD26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[4]}]

set_property -dict {PACKAGE_PIN AC22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[5]}]

set_property -dict {PACKAGE_PIN Y17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[6]}]

set_property -dict {PACKAGE_PIN AA18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[7]}]

set_property -dict {PACKAGE_PIN AA17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[8]}]

set_property -dict {PACKAGE_PIN Y25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[9]}]

set_property -dict {PACKAGE_PIN AA25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[10]}]

set_property -dict {PACKAGE_PIN AB26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[11]}]

set_property -dict {PACKAGE_PIN AB25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[12]}]

set_property -dict {PACKAGE_PIN AC26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[13]}]

set_property -dict {PACKAGE_PIN AC24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[14]}]

set_property -dict {PACKAGE_PIN AF17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[15]}]

set_property -dict {PACKAGE_PIN AE17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[16]}]

set_property -dict {PACKAGE_PIN AF18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[17]}]

set_property -dict {PACKAGE_PIN AE18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[18]}]

set_property -dict {PACKAGE_PIN AF19 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[19]}]

set_property -dict {PACKAGE_PIN R25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[1]}]

set_property -dict {PACKAGE_PIN R26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[0]}]

set_property -dict {PACKAGE_PIN AB22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[3]}]

set_property -dict {PACKAGE_PIN AD24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[2]}]

set_property -dict {PACKAGE_PIN AF24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[0]}]

set_property -dict {PACKAGE_PIN AE23 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[1]}]

set_property -dict {PACKAGE_PIN AF23 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[2]}]

set_property -dict {PACKAGE_PIN AE22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[3]}]

set_property -dict {PACKAGE_PIN AF22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[4]}]

set_property -dict {PACKAGE_PIN AE21 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[5]}]

set_property -dict {PACKAGE_PIN AE20 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[6]}]

set_property -dict {PACKAGE_PIN AF20 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[7]}]

set_property -dict {PACKAGE_PIN Y26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[8]}]

set_property -dict {PACKAGE_PIN W25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[9]}]

set_property -dict {PACKAGE_PIN W26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[10]}]

set_property -dict {PACKAGE_PIN V24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[11]}]

set_property -dict {PACKAGE_PIN V26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[12]}]

set_property -dict {PACKAGE_PIN U25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[13]}]

set_property -dict {PACKAGE_PIN U26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[14]}]

set_property -dict {PACKAGE_PIN U24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[15]}]

set_property -dict {PACKAGE_PIN AB16 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[16]}]

set_property -dict {PACKAGE_PIN AC19 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[17]}]

set_property -dict {PACKAGE_PIN AB17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[18]}]

set_property -dict {PACKAGE_PIN AC18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[19]}]

set_property -dict {PACKAGE_PIN AD18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[20]}]

set_property -dict {PACKAGE_PIN AC16 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[21]}]

set_property -dict {PACKAGE_PIN Y15 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[22]}]

set_property -dict {PACKAGE_PIN AA15 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[23]}]

set_property -dict {PACKAGE_PIN AD17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[24]}]

set_property -dict {PACKAGE_PIN AC17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[25]}]

set_property -dict {PACKAGE_PIN AD20 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[26]}]

set_property -dict {PACKAGE_PIN AB21 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[27]}]

set_property -dict {PACKAGE_PIN AD21 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[28]}]

set_property -dict {PACKAGE_PIN AC21 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[29]}]

set_property -dict {PACKAGE_PIN AA19 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[30]}]

set_property -dict {PACKAGE_PIN AC23 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[31]}]

set_property -dict {PACKAGE_PIN AD23 IOSTANDARD LVCMOS33} [get_ports ext_ram_ce_n]

set_property -dict {PACKAGE_PIN AB19 IOSTANDARD LVCMOS33} [get_ports ext_ram_oe_n]

set_property -dict {PACKAGE_PIN AD19 IOSTANDARD LVCMOS33} [get_ports ext_ram_we_n]

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

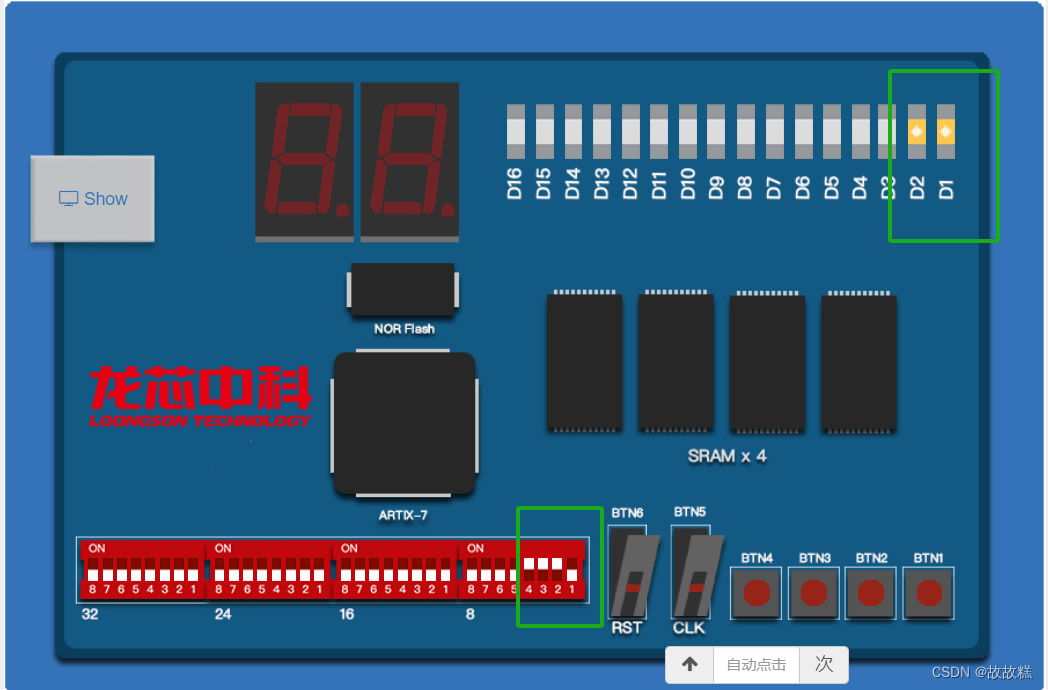

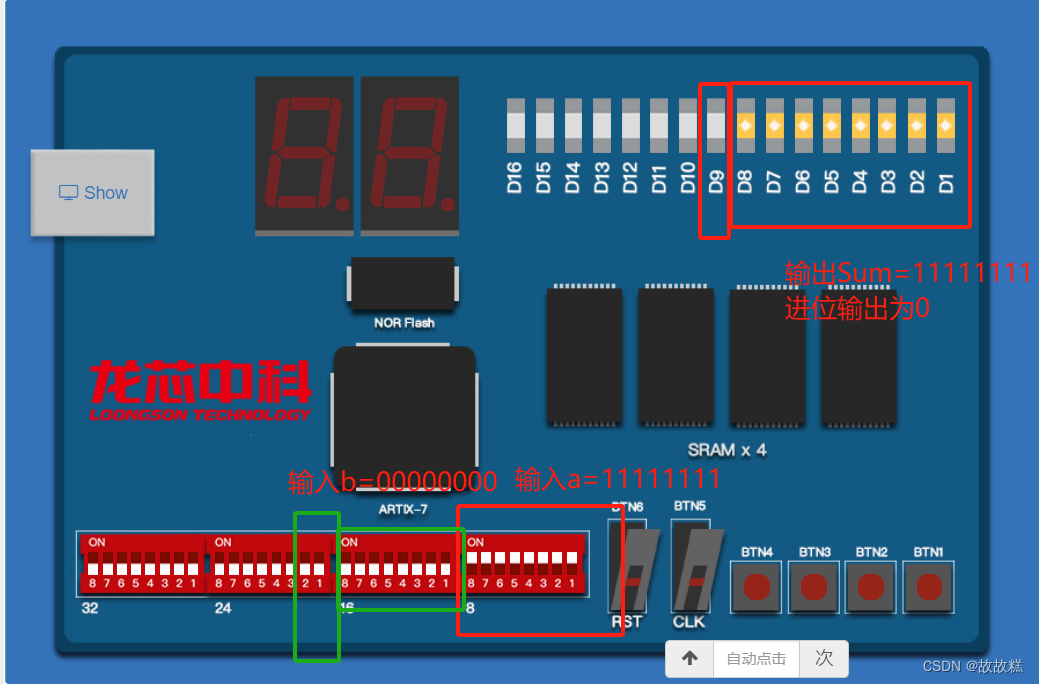

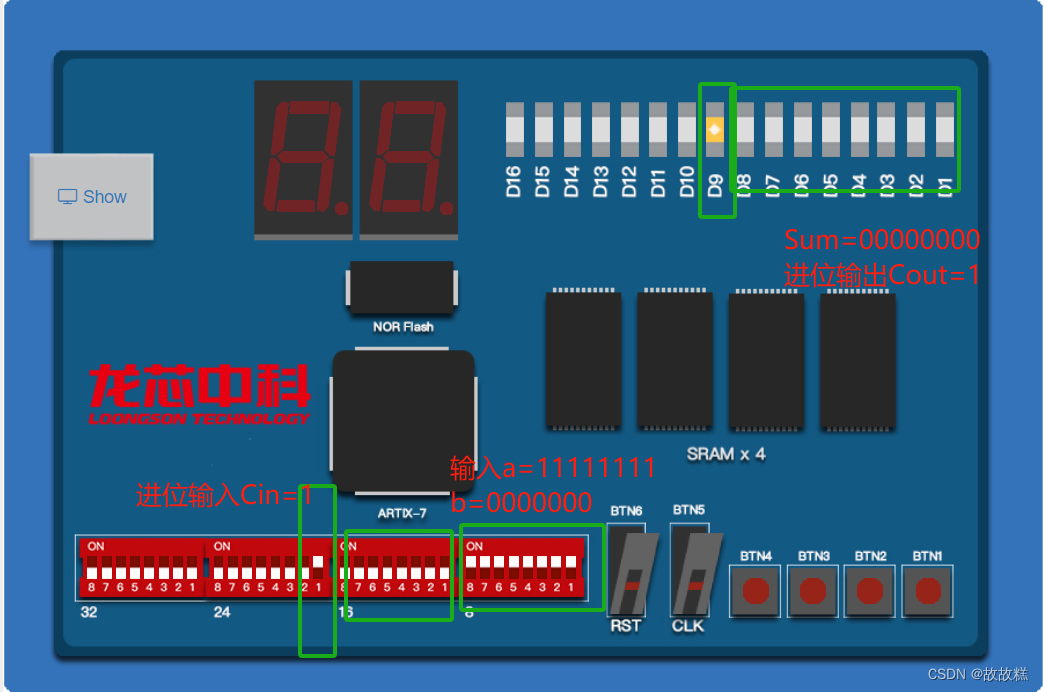

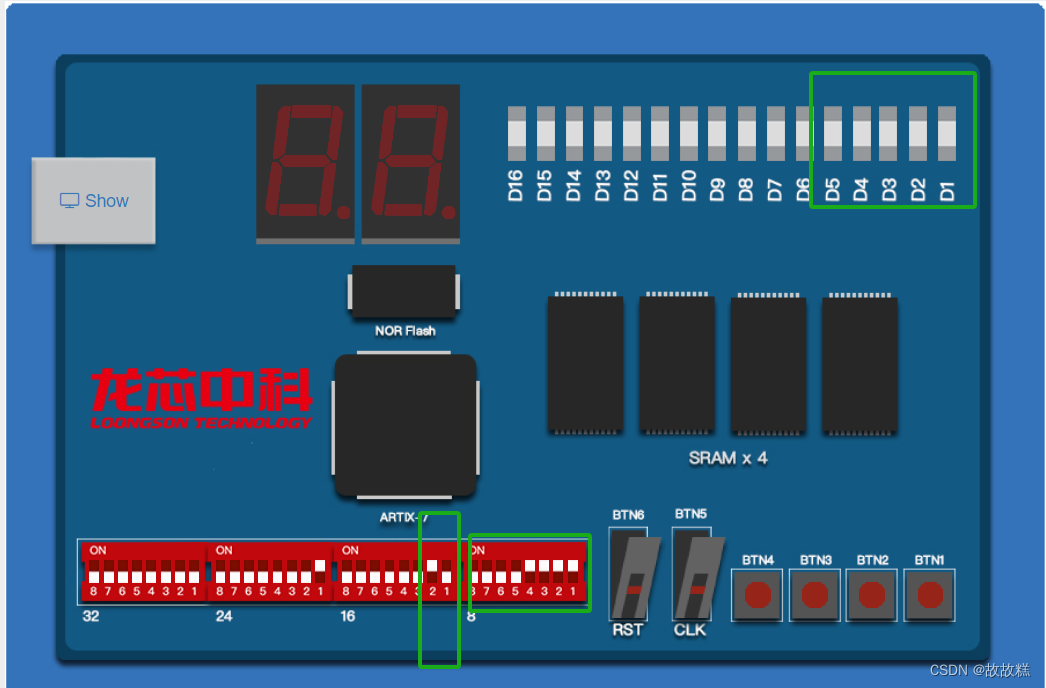

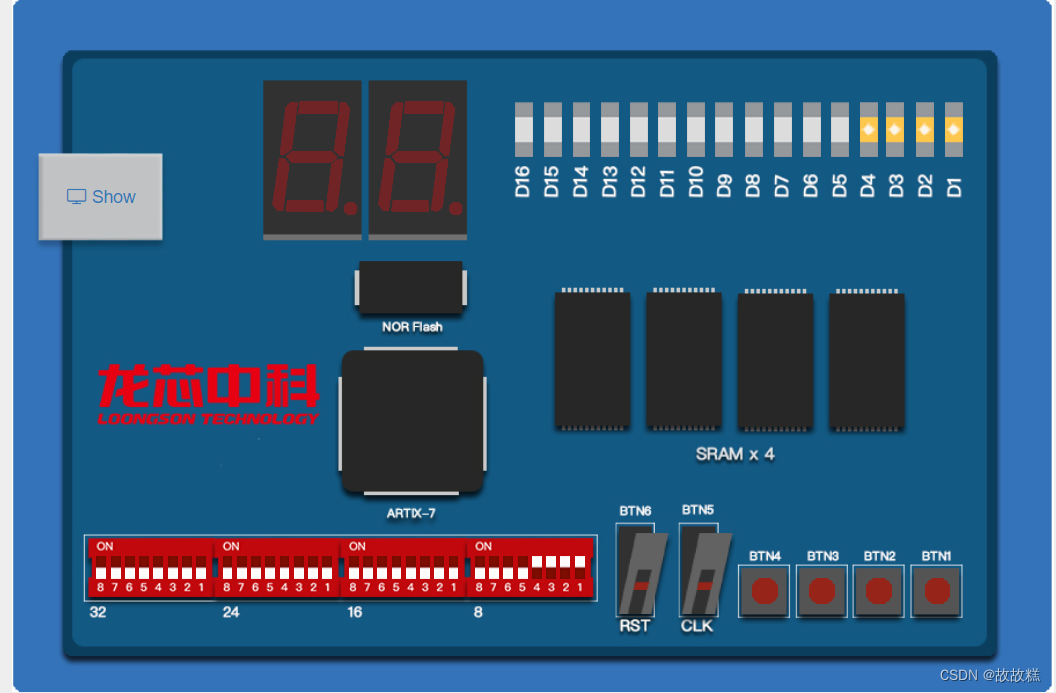

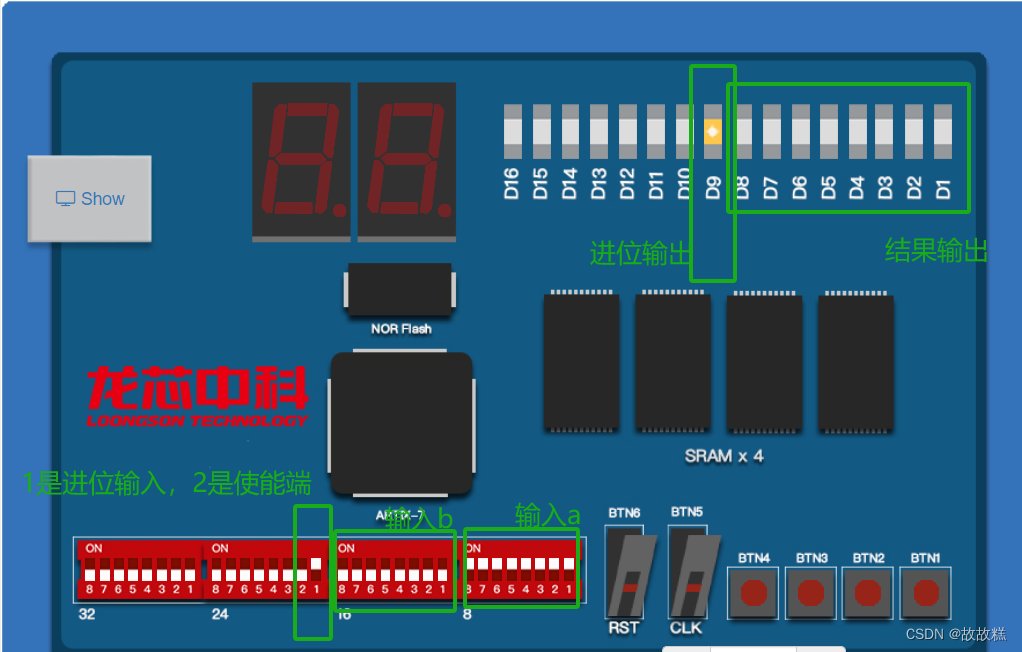

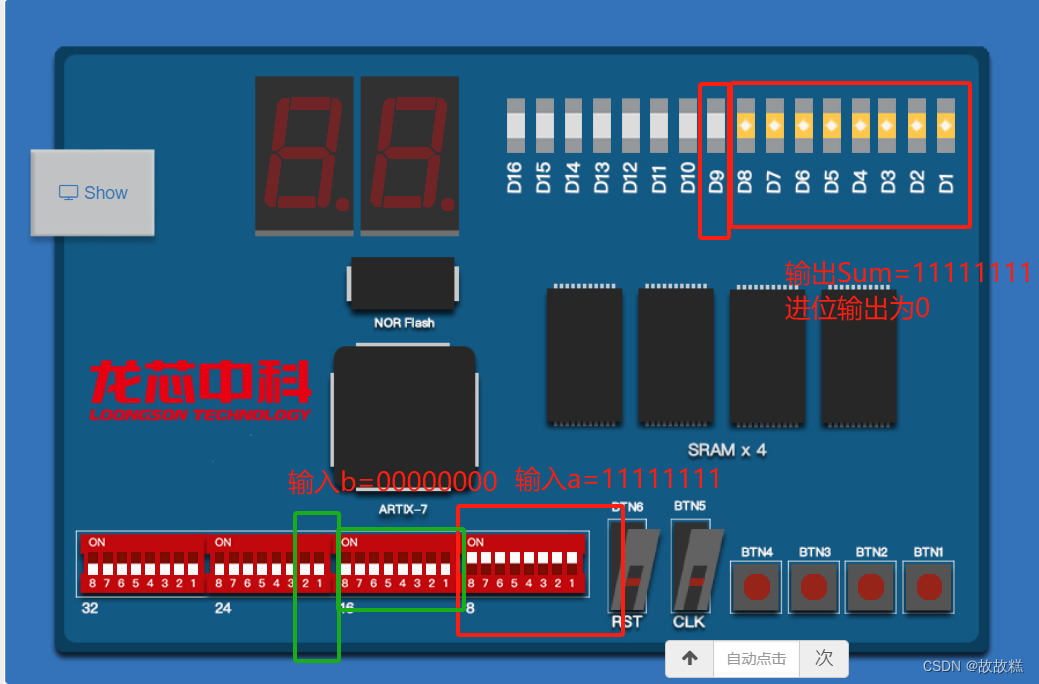

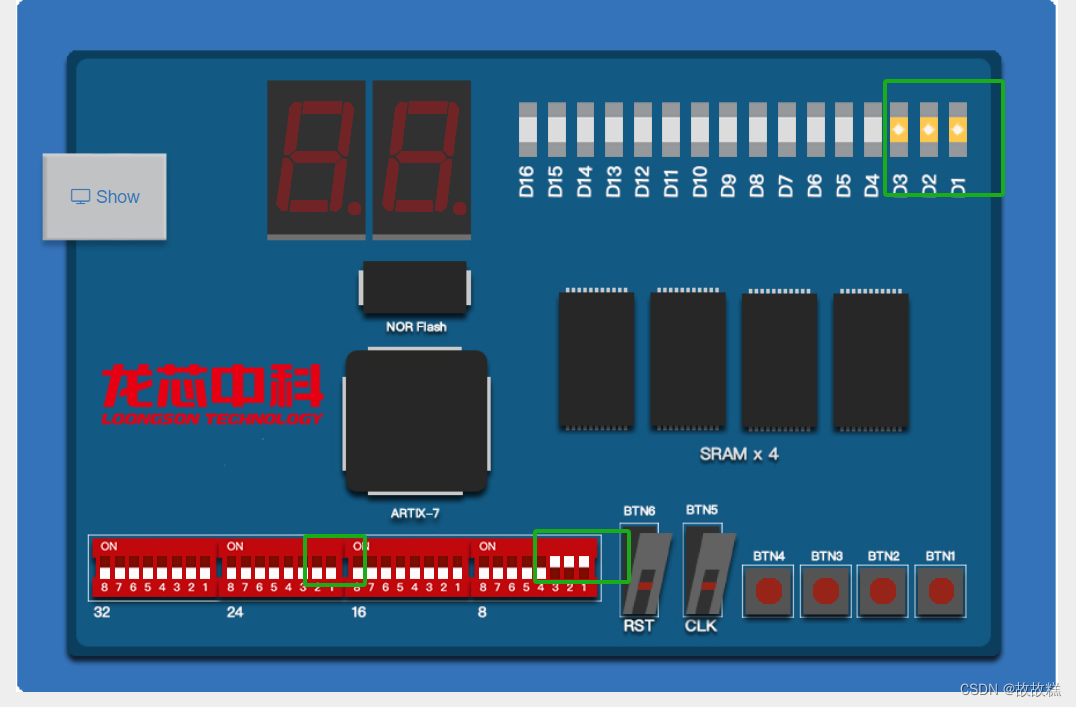

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]测试图

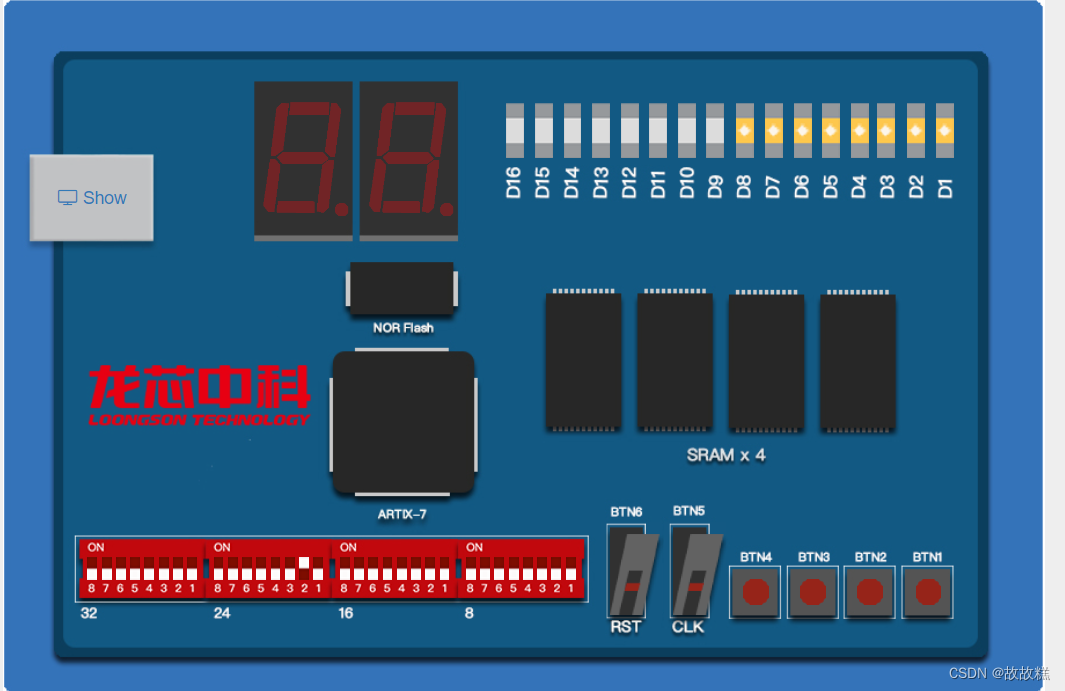

比如使能端2号按钮拨上边,代表此时加法器不工作,输出高阻态:8个灯全亮

当使能端有效的情况下,进位输入为0(按钮1拨下边)输入a=11111111,b=00000000,此时输出Sum=11111111,进位输出Cout=0,所以D1到D8的灯亮,D9灯不亮:

当使能端有效的情况下,进位输入为1(按钮1拨下、上边)输入a=11111111,b=00000000,此时输出Sum=00000000,进位输出Cout=1,所以D1到D8的不亮,D9灯亮:

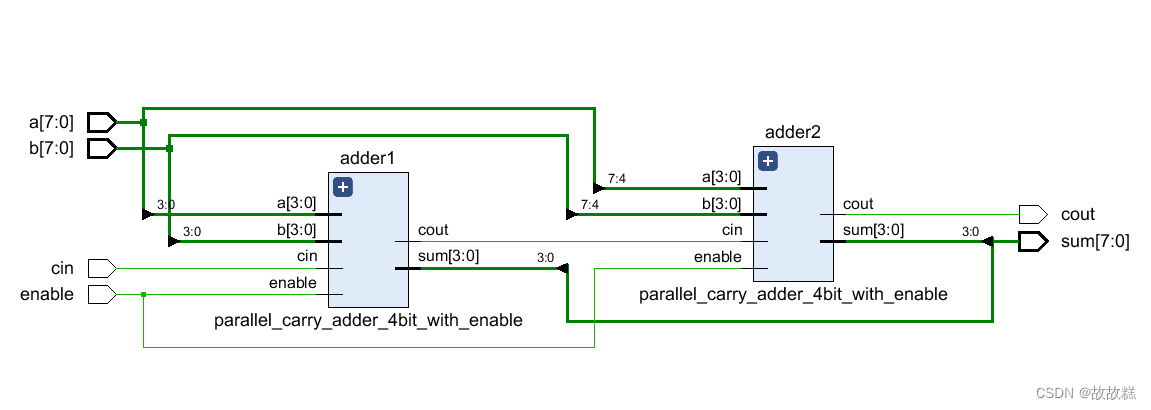

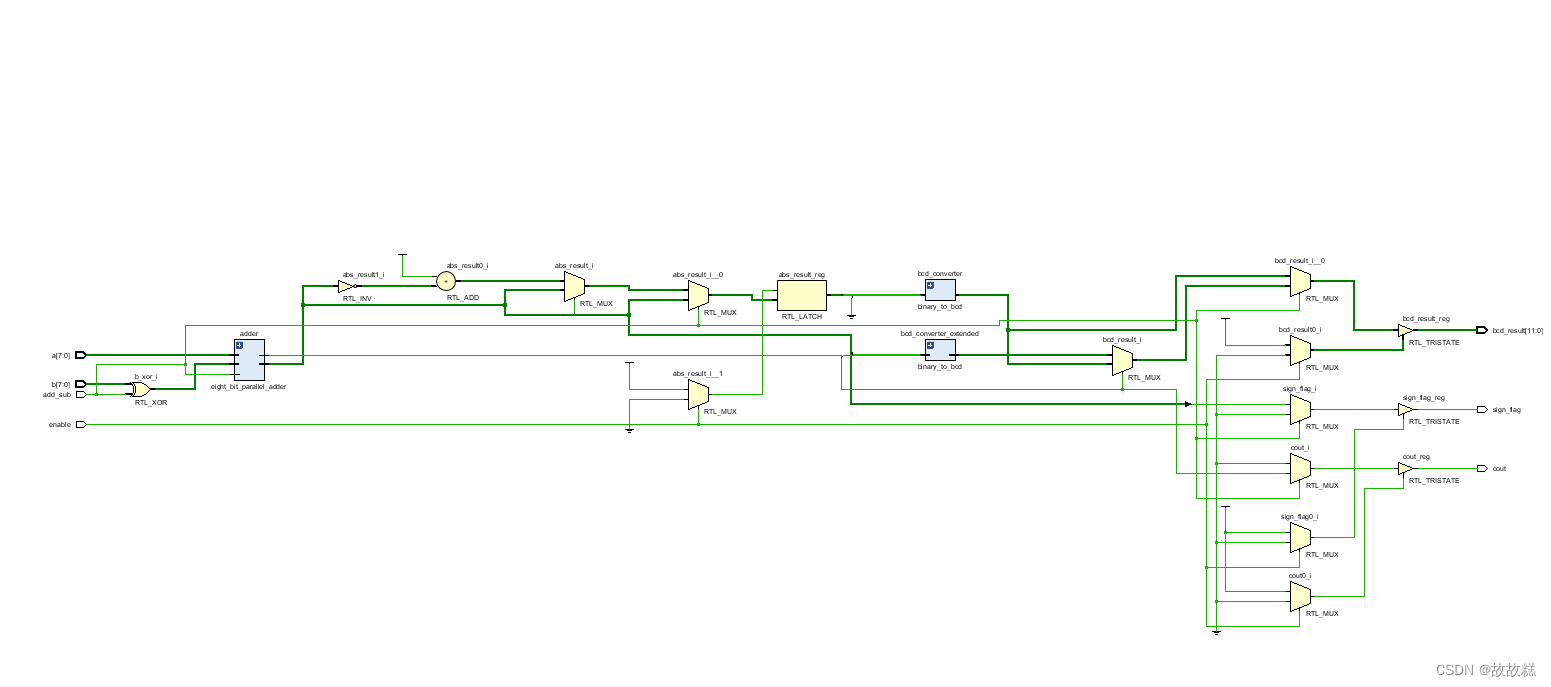

2. 扩展任务

(1)(a)4位并行加法器的设计:

设计原理:

定义两个4位宽的输入端口A和B,分别代表两个加数。

定义一个进位输入端口Cin,用于接收来自更低位的进位信号(对于4位全加器的最低位,Cin通常是0)。

定义一个4位宽的输出端口Sum,用于输出加法结果。

定义一个输出端口Cout,用于输出最高位的进位信号。

然后先计算各个加法器的进位,然后将进位直接给1位全加器

Verilog源程序:

`timescale 1ns / 1ps

module parallel_carry_adder_4bit_with_enable(

input [3:0] a,

input [3:0] b,

input cin,

input enable,

output [3:0] sum,

output cout

);

// 进位生成和进位传播信号

wire [2:0] g, p;

wire [3:0] c;

wire[3:0]tempsum;

// 计算进位生成和进位传播

assign g[0] = a[0] & b[0];

assign p[0] = a[0] | b[0];

assign g[1] = a[1] & b[1];

assign p[1] = a[1] | b[1];

assign g[2] = a[2] & b[2];

assign p[2] = a[2] | b[2];

// 进位计算

assign c[0] = cin;

assign c[1] = g[0] | (p[0] & cin);

assign c[2] = g[1] | (p[1] & g[0]) | (p[1] & p[0] & cin);

assign c[3] = g[2] | (p[2] & (g[1] | (p[1] & g[0]))) | (p[2] & p[1] & p[0] & cin);

// 实例化全加器

full_adder_with_enable fa0(.a(a[0]), .b(b[0]), .cin(cin), .enable(enable), .sum(tempsum[0]), .cout());

full_adder_with_enable fa1(.a(a[1]), .b(b[1]), .cin(c[1]), .enable(enable), .sum(tempsum[1]), .cout());

full_adder_with_enable fa2(.a(a[2]), .b(b[2]), .cin(c[2]), .enable(enable), .sum(tempsum[2]), .cout());

full_adder_with_enable fa3(.a(a[3]), .b(b[3]), .cin(c[3]), .enable(enable), .sum(tempsum[3]), .cout(cout));

assign sum= enable ? 4'bz: tempsum;

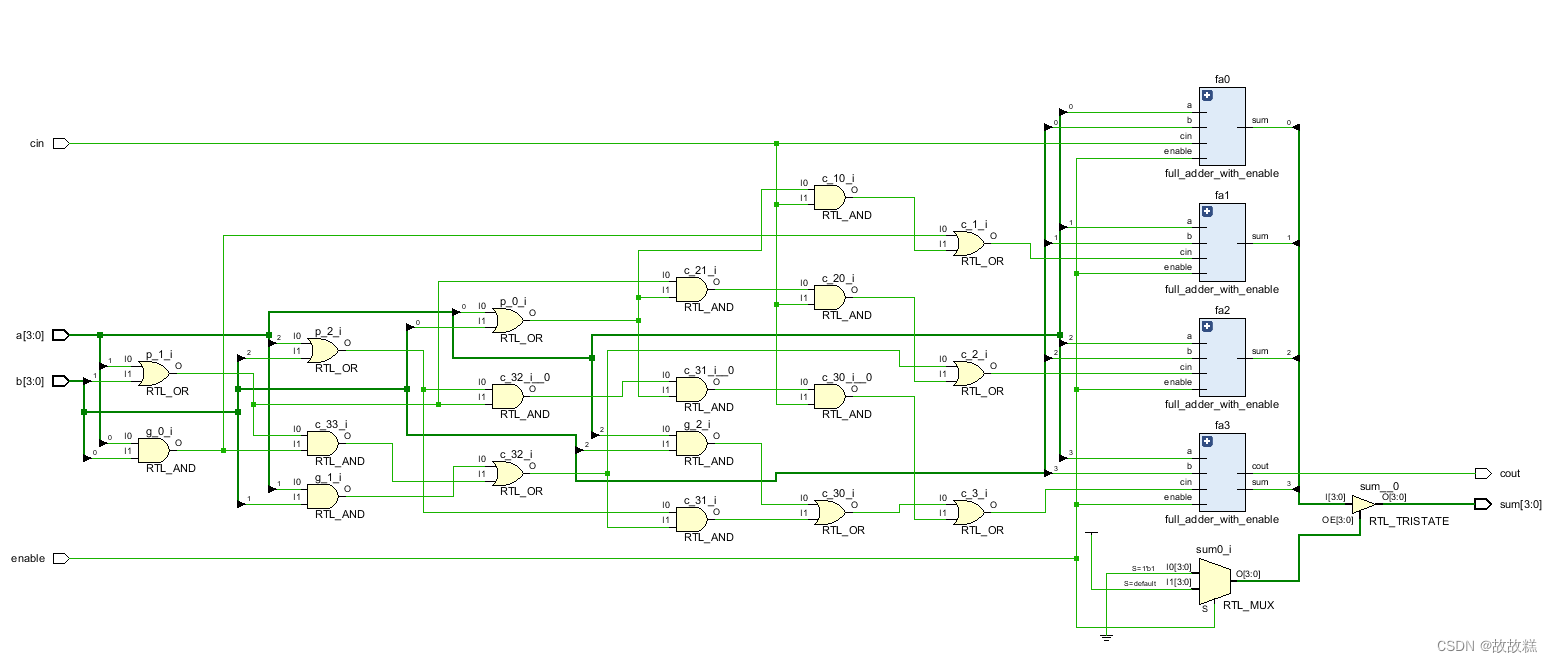

endmoduleRTL视图:

Modelsim仿真源程序:

`timescale 1ns / 1ps

module parallel_carry_adder_4bit_with_enable_tb;

// 定义输入和输出

reg [3:0] a, b;

reg cin, enable;

wire [3:0] sum;

wire cout;

// 实例化并行进位加法器

parallel_carry_adder_4bit_with_enable u1 (

.a(a),

.b(b),

.cin(cin),

.enable(enable),

.sum(sum),

.cout(cout)

);

// 初始化输入和调用测试

initial begin

enable = 1; a = 4'b1111; b = 4'b0000;cin = 0; #10;

$display("enable = %b, sum = %b, cout = %b", enable ,sum, cout);

enable = 0; a = 4'b0000; b = 4'b0000;cin = 1; #10;

$display("enable = %b, sum = %b, cout = %b", enable ,sum, cout);

enable = 0; a = 4'b0000; b = 4'b1111;cin = 0; #10;

$display("enable = %b, sum = %b, cout = %b", enable ,sum, cout);

enable = 0; a = 4'b0000; b = 4'b1111;cin = 1; #10;

$display("enable = %b, sum = %b, cout = %b", enable ,sum, cout);

enable = 1; a = 4'b1111; b = 4'b0000;cin = 0; #10;

$display("enable = %b, sum = %b, cout = %b", enable ,sum, cout);

$finish;

end

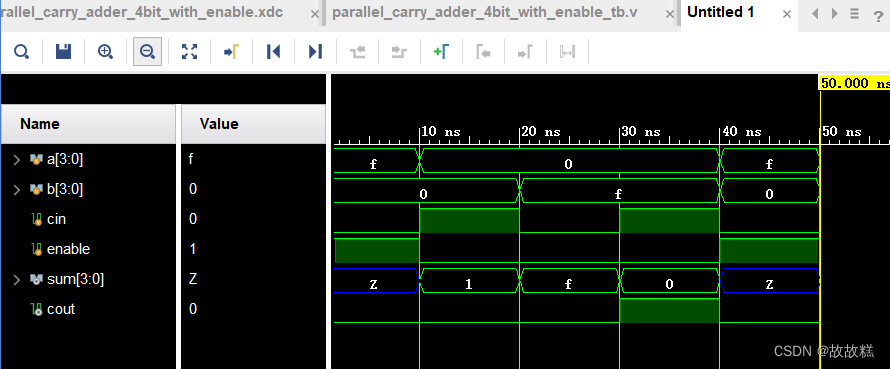

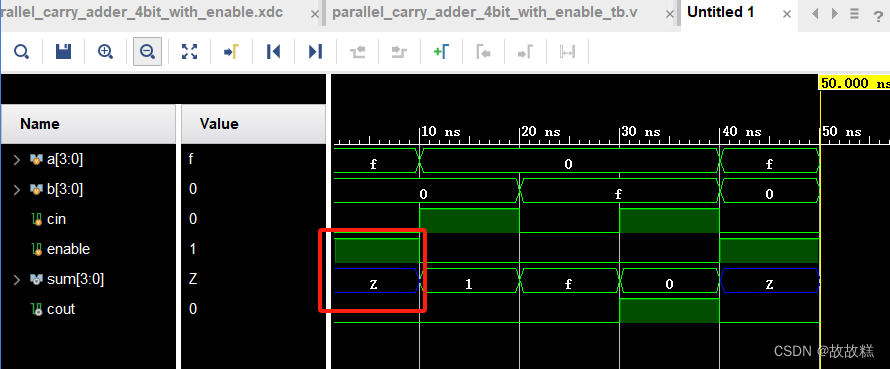

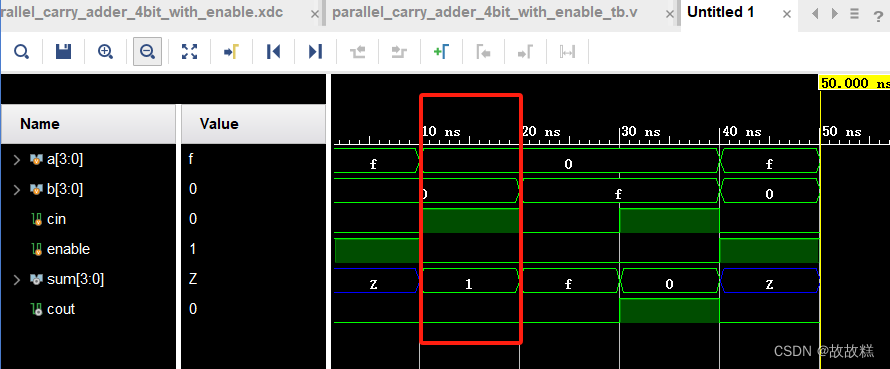

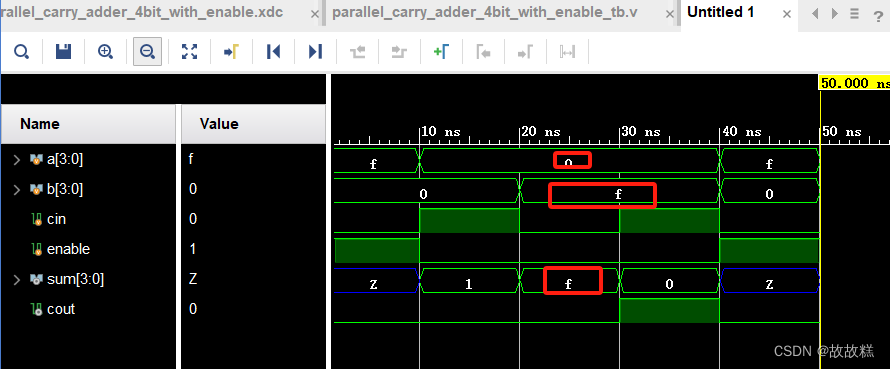

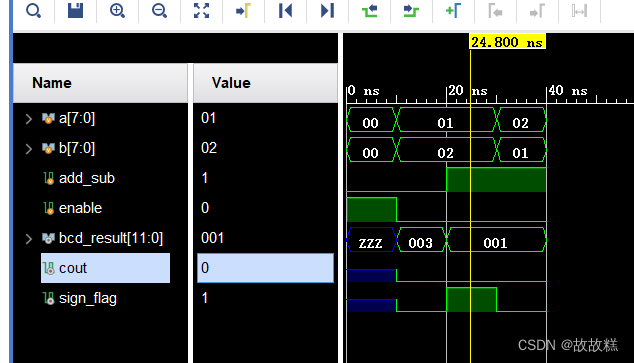

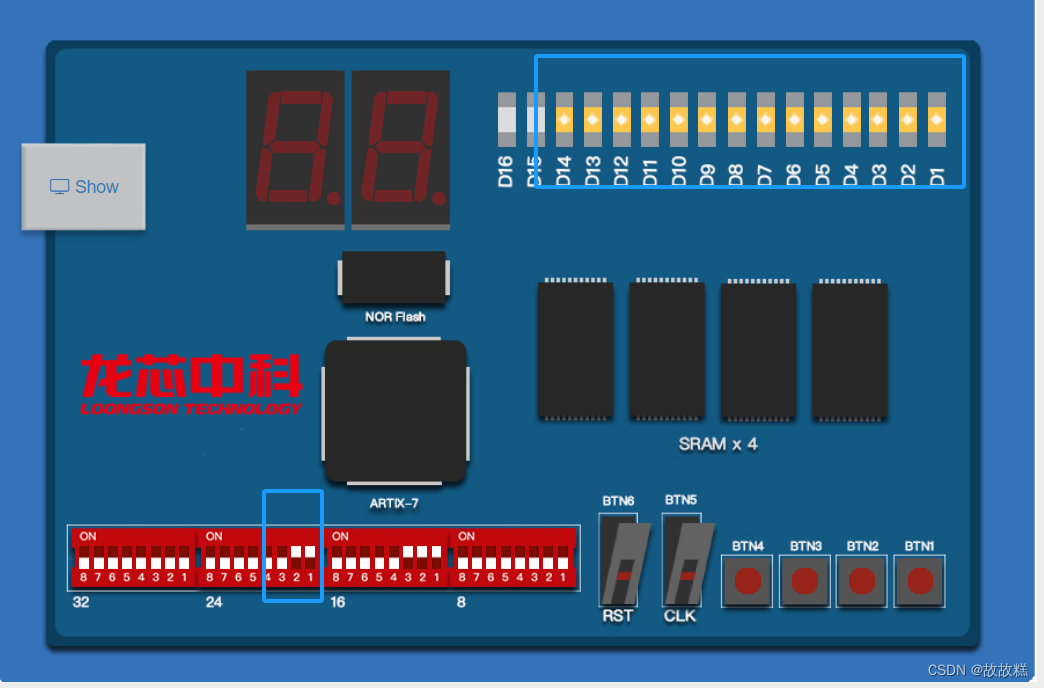

endmoduleModelsim仿真结果:

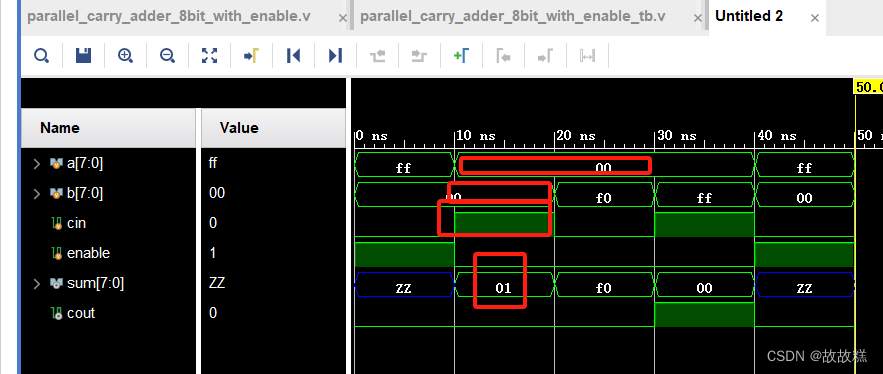

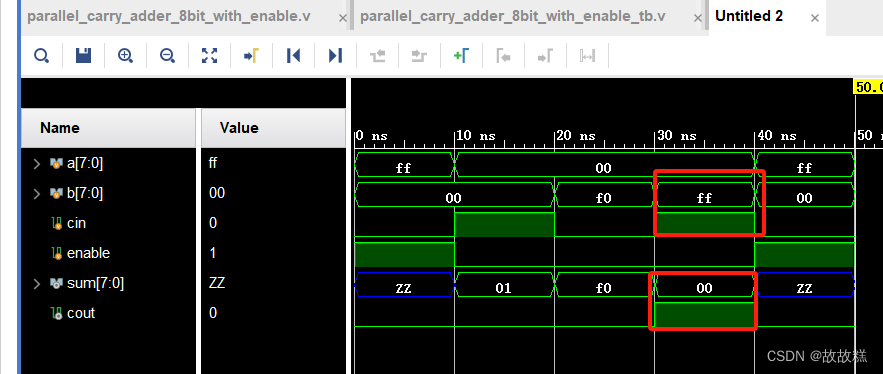

a b分别是两个4位二进制的输入,enable代表使能端,cin代表进位输入,Sum表示和,cout代表高位进位输出

下面是分析:我们在代码中分别让:

(1)enable = 1; a = 4'b1111; b = 4'b0000;cin = 0; #10;

因为enable=1,加法器处于不工作的状态,所以输出为高阻态

(2) enable = 0; a = 4'b0000; b = 4'b0000;cin = 1; #10;

Enable=0,加法器工作,sum=a+b+cin=0001,cout=0,所以sum那一行显示为1,而Cout为低电平表示输出0

(3) enable = 0; a = 4'b0000; b = 4'b1111;cin = 0; #10;

Enable=0,加法器工作,sum=a+b+cin=1111,cout=0,所以sum那一行显示为f,而Cout为低电平表示输出0

(4) enable = 0; a = 4'b0000; b = 4'b1111;cin = 1; #10;

Enable=0,加法器工作,sum=a+b+cin=0000,cout=1,所以sum那一行显示为0,而Cout为高电平表示输出1

下载测试结果管脚配置:

#Clock

set_property -dict {PACKAGE_PIN K21 IOSTANDARD LVCMOS33} [get_ports clk_50M] ;#50MHz main clock in

set_property -dict {PACKAGE_PIN H21 IOSTANDARD LVCMOS33} [get_ports clk_11M0592] ;#11.0592MHz clock for UART

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clk_11M0592_IBUF]

create_clock -period 20.000 -name clk_50M -waveform {0.000 10.000} [get_ports clk_50M]

create_clock -period 90.422 -name clk_11M0592 -waveform {0.000 45.211} [get_ports clk_11M0592]

#Touch Button

set_property -dict {PACKAGE_PIN T2 IOSTANDARD LVCMOS33} [get_ports touch_btn[0]] ;#BTN1

set_property -dict {PACKAGE_PIN M1 IOSTANDARD LVCMOS33} [get_ports touch_btn[1]] ;#BTN2

set_property -dict {PACKAGE_PIN P3 IOSTANDARD LVCMOS33} [get_ports touch_btn[2]] ;#BTN3

set_property -dict {PACKAGE_PIN U2 IOSTANDARD LVCMOS33} [get_ports touch_btn[3]] ;#BTN4

set_property -dict {PACKAGE_PIN U1 IOSTANDARD LVCMOS33} [get_ports clock_btn] ;#BTN5

set_property -dict {PACKAGE_PIN U5 IOSTANDARD LVCMOS33} [get_ports reset_btn] ;#BTN6

#required if touch button used as manual clock source

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clock_btn_IBUF]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets reset_btn_IBUF]

#CPLD GPIO 12-16

#set_property -dict {PACKAGE_PIN J14 IOSTANDARD LVCMOS33} [get_ports {uart_wrn}]

#set_property -dict {PACKAGE_PIN L14 IOSTANDARD LVCMOS33} [get_ports {uart_rdn}]

#set_property -dict {PACKAGE_PIN J15 IOSTANDARD LVCMOS33} [get_ports {uart_tbre}]

#set_property -dict {PACKAGE_PIN K15 IOSTANDARD LVCMOS33} [get_ports {uart_tsre}]

#set_property -dict {PACKAGE_PIN L15 IOSTANDARD LVCMOS33} [get_ports {uart_dataready}]

#Ext serial

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN H18} [get_ports txd] ;#GPIO5

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN J20} [get_ports rxd] ;#GPIO6

#Digital Video

set_property -dict {PACKAGE_PIN H22 IOSTANDARD LVCMOS33} [get_ports video_clk]

set_property -dict {PACKAGE_PIN E26 IOSTANDARD LVCMOS33} [get_ports {video_red[2]}]

set_property -dict {PACKAGE_PIN F24 IOSTANDARD LVCMOS33} [get_ports {video_red[1]}]

set_property -dict {PACKAGE_PIN K23 IOSTANDARD LVCMOS33} [get_ports {video_red[0]}]

set_property -dict {PACKAGE_PIN F23 IOSTANDARD LVCMOS33} [get_ports {video_green[2]}]

set_property -dict {PACKAGE_PIN E23 IOSTANDARD LVCMOS33} [get_ports {video_green[1]}]

set_property -dict {PACKAGE_PIN K22 IOSTANDARD LVCMOS33} [get_ports {video_green[0]}]

set_property -dict {PACKAGE_PIN D25 IOSTANDARD LVCMOS33} [get_ports {video_blue[1]}]

set_property -dict {PACKAGE_PIN E25 IOSTANDARD LVCMOS33} [get_ports {video_blue[0]}]

set_property -dict {PACKAGE_PIN J24 IOSTANDARD LVCMOS33} [get_ports video_hsync]

set_property -dict {PACKAGE_PIN H24 IOSTANDARD LVCMOS33} [get_ports video_vsync]

set_property -dict {PACKAGE_PIN G24 IOSTANDARD LVCMOS33} [get_ports video_de]

#LEDS

set_property -dict {PACKAGE_PIN B24 IOSTANDARD LVCMOS33} [get_ports sum[0]]

set_property -dict {PACKAGE_PIN E21 IOSTANDARD LVCMOS33} [get_ports sum[1]]

set_property -dict {PACKAGE_PIN A24 IOSTANDARD LVCMOS33} [get_ports sum[2]]

set_property -dict {PACKAGE_PIN D23 IOSTANDARD LVCMOS33} [get_ports sum[3]]

set_property -dict {PACKAGE_PIN C22 IOSTANDARD LVCMOS33} [get_ports cout]

set_property -dict {PACKAGE_PIN C21 IOSTANDARD LVCMOS33} [get_ports {leds[5]}]

set_property -dict {PACKAGE_PIN E20 IOSTANDARD LVCMOS33} [get_ports {leds[6]}]

set_property -dict {PACKAGE_PIN B22 IOSTANDARD LVCMOS33} [get_ports {leds[7]}]

set_property -dict {PACKAGE_PIN C23 IOSTANDARD LVCMOS33} [get_ports {leds[8]}]

set_property -dict {PACKAGE_PIN A23 IOSTANDARD LVCMOS33} [get_ports {leds[9]}]

set_property -dict {PACKAGE_PIN D21 IOSTANDARD LVCMOS33} [get_ports {leds[10]}]

set_property -dict {PACKAGE_PIN A18 IOSTANDARD LVCMOS33} [get_ports {leds[11]}]

set_property -dict {PACKAGE_PIN D20 IOSTANDARD LVCMOS33} [get_ports {leds[12]}]

set_property -dict {PACKAGE_PIN A22 IOSTANDARD LVCMOS33} [get_ports {leds[13]}]

set_property -dict {PACKAGE_PIN A20 IOSTANDARD LVCMOS33} [get_ports {leds[14]}]

set_property -dict {PACKAGE_PIN B20 IOSTANDARD LVCMOS33} [get_ports {leds[15]}]

#DPY0

set_property -dict {PACKAGE_PIN B19 IOSTANDARD LVCMOS33} [get_ports {dpy0[0]}]

set_property -dict {PACKAGE_PIN D19 IOSTANDARD LVCMOS33} [get_ports {dpy0[1]}]

set_property -dict {PACKAGE_PIN B21 IOSTANDARD LVCMOS33} [get_ports {dpy0[2]}]

set_property -dict {PACKAGE_PIN A19 IOSTANDARD LVCMOS33} [get_ports {dpy0[3]}]

set_property -dict {PACKAGE_PIN E18 IOSTANDARD LVCMOS33} [get_ports {dpy0[4]}]

set_property -dict {PACKAGE_PIN C19 IOSTANDARD LVCMOS33} [get_ports {dpy0[5]}]

set_property -dict {PACKAGE_PIN B17 IOSTANDARD LVCMOS33} [get_ports {dpy0[6]}]

set_property -dict {PACKAGE_PIN C17 IOSTANDARD LVCMOS33} [get_ports {dpy0[7]}]

#DPY1

set_property -dict {PACKAGE_PIN A17 IOSTANDARD LVCMOS33} [get_ports {dpy1[0]}]

set_property -dict {PACKAGE_PIN D16 IOSTANDARD LVCMOS33} [get_ports {dpy1[1]}]

set_property -dict {PACKAGE_PIN E17 IOSTANDARD LVCMOS33} [get_ports {dpy1[2]}]

set_property -dict {PACKAGE_PIN F17 IOSTANDARD LVCMOS33} [get_ports {dpy1[3]}]

set_property -dict {PACKAGE_PIN E16 IOSTANDARD LVCMOS33} [get_ports {dpy1[4]}]

set_property -dict {PACKAGE_PIN G16 IOSTANDARD LVCMOS33} [get_ports {dpy1[5]}]

set_property -dict {PACKAGE_PIN F15 IOSTANDARD LVCMOS33} [get_ports {dpy1[6]}]

set_property -dict {PACKAGE_PIN G17 IOSTANDARD LVCMOS33} [get_ports {dpy1[7]}]

#DIP_SW

set_property -dict {PACKAGE_PIN T3 IOSTANDARD LVCMOS33} [get_ports a[0]]

set_property -dict {PACKAGE_PIN J3 IOSTANDARD LVCMOS33} [get_ports a[1]]

set_property -dict {PACKAGE_PIN M2 IOSTANDARD LVCMOS33} [get_ports a[2]]

set_property -dict {PACKAGE_PIN P1 IOSTANDARD LVCMOS33} [get_ports a[3]]

set_property -dict {PACKAGE_PIN P4 IOSTANDARD LVCMOS33} [get_ports b[0]]

set_property -dict {PACKAGE_PIN L5 IOSTANDARD LVCMOS33} [get_ports b[1]]

set_property -dict {PACKAGE_PIN L3 IOSTANDARD LVCMOS33} [get_ports b[2]]

set_property -dict {PACKAGE_PIN N6 IOSTANDARD LVCMOS33} [get_ports b[3]]

set_property -dict {PACKAGE_PIN M6 IOSTANDARD LVCMOS33} [get_ports cin]

set_property -dict {PACKAGE_PIN N7 IOSTANDARD LVCMOS33} [get_ports enable]

set_property -dict {PACKAGE_PIN M7 IOSTANDARD LVCMOS33} [get_ports {dip_sw[10]}]

set_property -dict {PACKAGE_PIN L7 IOSTANDARD LVCMOS33} [get_ports {dip_sw[11]}]

set_property -dict {PACKAGE_PIN M5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[12]}]

set_property -dict {PACKAGE_PIN K3 IOSTANDARD LVCMOS33} [get_ports {dip_sw[13]}]

set_property -dict {PACKAGE_PIN J1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[14]}]

set_property -dict {PACKAGE_PIN L2 IOSTANDARD LVCMOS33} [get_ports {dip_sw[15]}]

set_property -dict {PACKAGE_PIN K2 IOSTANDARD LVCMOS33} [get_ports {dip_sw[16]}]

set_property -dict {PACKAGE_PIN K1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[17]}]

set_property -dict {PACKAGE_PIN N3 IOSTANDARD LVCMOS33} [get_ports {dip_sw[18]}]

set_property -dict {PACKAGE_PIN L4 IOSTANDARD LVCMOS33} [get_ports {dip_sw[19]}]

set_property -dict {PACKAGE_PIN M4 IOSTANDARD LVCMOS33} [get_ports {dip_sw[20]}]

set_property -dict {PACKAGE_PIN N2 IOSTANDARD LVCMOS33} [get_ports {dip_sw[21]}]

set_property -dict {PACKAGE_PIN P6 IOSTANDARD LVCMOS33} [get_ports {dip_sw[22]}]

set_property -dict {PACKAGE_PIN N1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[23]}]

set_property -dict {PACKAGE_PIN P5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[24]}]

set_property -dict {PACKAGE_PIN R3 IOSTANDARD LVCMOS33} [get_ports {dip_sw[25]}]

set_property -dict {PACKAGE_PIN T4 IOSTANDARD LVCMOS33} [get_ports {dip_sw[26]}]

set_property -dict {PACKAGE_PIN R1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[27]}]

set_property -dict {PACKAGE_PIN R5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[28]}]

set_property -dict {PACKAGE_PIN T5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[29]}]

set_property -dict {PACKAGE_PIN R6 IOSTANDARD LVCMOS33} [get_ports {dip_sw[30]}]

set_property -dict {PACKAGE_PIN R2 IOSTANDARD LVCMOS33} [get_ports {dip_sw[31]}]

set_property -dict {PACKAGE_PIN C2 IOSTANDARD LVCMOS33} [get_ports {flash_a[0]}]

set_property -dict {PACKAGE_PIN H9 IOSTANDARD LVCMOS33} [get_ports {flash_a[1]}]

set_property -dict {PACKAGE_PIN H8 IOSTANDARD LVCMOS33} [get_ports {flash_a[2]}]

set_property -dict {PACKAGE_PIN G9 IOSTANDARD LVCMOS33} [get_ports {flash_a[3]}]

set_property -dict {PACKAGE_PIN H7 IOSTANDARD LVCMOS33} [get_ports {flash_a[4]}]

set_property -dict {PACKAGE_PIN F8 IOSTANDARD LVCMOS33} [get_ports {flash_a[5]}]

set_property -dict {PACKAGE_PIN G8 IOSTANDARD LVCMOS33} [get_ports {flash_a[6]}]

set_property -dict {PACKAGE_PIN K7 IOSTANDARD LVCMOS33} [get_ports {flash_a[7]}]

set_property -dict {PACKAGE_PIN G7 IOSTANDARD LVCMOS33} [get_ports {flash_a[8]}]

set_property -dict {PACKAGE_PIN F7 IOSTANDARD LVCMOS33} [get_ports {flash_a[9]}]

set_property -dict {PACKAGE_PIN E6 IOSTANDARD LVCMOS33} [get_ports {flash_a[10]}]

set_property -dict {PACKAGE_PIN D6 IOSTANDARD LVCMOS33} [get_ports {flash_a[11]}]

set_property -dict {PACKAGE_PIN F5 IOSTANDARD LVCMOS33} [get_ports {flash_a[12]}]

set_property -dict {PACKAGE_PIN E3 IOSTANDARD LVCMOS33} [get_ports {flash_a[13]}]

set_property -dict {PACKAGE_PIN G5 IOSTANDARD LVCMOS33} [get_ports {flash_a[14]}]

set_property -dict {PACKAGE_PIN F4 IOSTANDARD LVCMOS33} [get_ports {flash_a[15]}]

set_property -dict {PACKAGE_PIN H6 IOSTANDARD LVCMOS33} [get_ports {flash_a[16]}]

set_property -dict {PACKAGE_PIN G4 IOSTANDARD LVCMOS33} [get_ports {flash_a[17]}]

set_property -dict {PACKAGE_PIN J6 IOSTANDARD LVCMOS33} [get_ports {flash_a[18]}]

set_property -dict {PACKAGE_PIN H4 IOSTANDARD LVCMOS33} [get_ports {flash_a[19]}]

set_property -dict {PACKAGE_PIN J5 IOSTANDARD LVCMOS33} [get_ports {flash_a[20]}]

set_property -dict {PACKAGE_PIN J4 IOSTANDARD LVCMOS33} [get_ports {flash_a[21]}]

set_property -dict {PACKAGE_PIN K6 IOSTANDARD LVCMOS33} [get_ports {flash_a[22]}]

set_property -dict {PACKAGE_PIN D4 IOSTANDARD LVCMOS33} [get_ports {flash_d[0]}]

set_property -dict {PACKAGE_PIN C1 IOSTANDARD LVCMOS33} [get_ports {flash_d[1]}]

set_property -dict {PACKAGE_PIN D1 IOSTANDARD LVCMOS33} [get_ports {flash_d[2]}]

set_property -dict {PACKAGE_PIN E1 IOSTANDARD LVCMOS33} [get_ports {flash_d[3]}]

set_property -dict {PACKAGE_PIN G1 IOSTANDARD LVCMOS33} [get_ports {flash_d[4]}]

set_property -dict {PACKAGE_PIN A2 IOSTANDARD LVCMOS33} [get_ports {flash_d[5]}]

set_property -dict {PACKAGE_PIN C3 IOSTANDARD LVCMOS33} [get_ports {flash_d[6]}]

set_property -dict {PACKAGE_PIN B4 IOSTANDARD LVCMOS33} [get_ports {flash_d[7]}]

set_property -dict {PACKAGE_PIN D3 IOSTANDARD LVCMOS33} [get_ports {flash_d[8]}]

set_property -dict {PACKAGE_PIN E2 IOSTANDARD LVCMOS33} [get_ports {flash_d[9]}]

set_property -dict {PACKAGE_PIN F3 IOSTANDARD LVCMOS33} [get_ports {flash_d[10]}]

set_property -dict {PACKAGE_PIN F2 IOSTANDARD LVCMOS33} [get_ports {flash_d[11]}]

set_property -dict {PACKAGE_PIN G2 IOSTANDARD LVCMOS33} [get_ports {flash_d[12]}]

set_property -dict {PACKAGE_PIN B2 IOSTANDARD LVCMOS33} [get_ports {flash_d[13]}]

set_property -dict {PACKAGE_PIN A3 IOSTANDARD LVCMOS33} [get_ports {flash_d[14]}]

set_property -dict {PACKAGE_PIN A4 IOSTANDARD LVCMOS33} [get_ports {flash_d[15]}]

set_property -dict {PACKAGE_PIN B1 IOSTANDARD LVCMOS33} [get_ports flash_byte_n]

set_property -dict {PACKAGE_PIN E5 IOSTANDARD LVCMOS33} [get_ports flash_ce_n ]

set_property -dict {PACKAGE_PIN A5 IOSTANDARD LVCMOS33} [get_ports flash_oe_n ]

set_property -dict {PACKAGE_PIN G6 IOSTANDARD LVCMOS33} [get_ports flash_rp_n ]

set_property -dict {PACKAGE_PIN D5 IOSTANDARD LVCMOS33} [get_ports flash_vpen ]

set_property -dict {PACKAGE_PIN B5 IOSTANDARD LVCMOS33} [get_ports flash_we_n ]

set_property -dict {PACKAGE_PIN T19 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[0]}]

set_property -dict {PACKAGE_PIN V18 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[1]}]

set_property -dict {PACKAGE_PIN T18 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[2]}]

set_property -dict {PACKAGE_PIN V17 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[3]}]

set_property -dict {PACKAGE_PIN U17 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[4]}]

set_property -dict {PACKAGE_PIN R20 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[5]}]

set_property -dict {PACKAGE_PIN R23 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[6]}]

set_property -dict {PACKAGE_PIN T23 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[7]}]

set_property -dict {PACKAGE_PIN U22 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[8]}]

set_property -dict {PACKAGE_PIN Y22 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[9]}]

set_property -dict {PACKAGE_PIN AB24 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[10]}]

set_property -dict {PACKAGE_PIN AA23 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[11]}]

set_property -dict {PACKAGE_PIN Y21 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[12]}]

set_property -dict {PACKAGE_PIN Y20 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[13]}]

set_property -dict {PACKAGE_PIN AA22 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[14]}]

set_property -dict {PACKAGE_PIN W19 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[15]}]

set_property -dict {PACKAGE_PIN W21 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[16]}]

set_property -dict {PACKAGE_PIN W20 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[17]}]

set_property -dict {PACKAGE_PIN W18 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[18]}]

set_property -dict {PACKAGE_PIN V19 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[19]}]

set_property -dict {PACKAGE_PIN L22 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[1]}]

set_property -dict {PACKAGE_PIN L20 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[0]}]

set_property -dict {PACKAGE_PIN K25 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[3]}]

set_property -dict {PACKAGE_PIN L23 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[2]}]

set_property -dict {PACKAGE_PIN L24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[0]}]

set_property -dict {PACKAGE_PIN L25 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[1]}]

set_property -dict {PACKAGE_PIN M26 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[2]}]

set_property -dict {PACKAGE_PIN M25 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[3]}]

set_property -dict {PACKAGE_PIN N26 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[4]}]

set_property -dict {PACKAGE_PIN P24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[5]}]

set_property -dict {PACKAGE_PIN P26 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[6]}]

set_property -dict {PACKAGE_PIN P25 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[7]}]

set_property -dict {PACKAGE_PIN AA24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[8]}]

set_property -dict {PACKAGE_PIN Y23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[9]}]

set_property -dict {PACKAGE_PIN V21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[10]}]

set_property -dict {PACKAGE_PIN W24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[11]}]

set_property -dict {PACKAGE_PIN W23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[12]}]

set_property -dict {PACKAGE_PIN V22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[13]}]

set_property -dict {PACKAGE_PIN V23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[14]}]

set_property -dict {PACKAGE_PIN U21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[15]}]

set_property -dict {PACKAGE_PIN P21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[16]}]

set_property -dict {PACKAGE_PIN M21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[17]}]

set_property -dict {PACKAGE_PIN P23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[18]}]

set_property -dict {PACKAGE_PIN P19 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[19]}]

set_property -dict {PACKAGE_PIN N19 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[20]}]

set_property -dict {PACKAGE_PIN M20 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[21]}]

set_property -dict {PACKAGE_PIN N24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[22]}]

set_property -dict {PACKAGE_PIN N21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[23]}]

set_property -dict {PACKAGE_PIN T22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[24]}]

set_property -dict {PACKAGE_PIN R22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[25]}]

set_property -dict {PACKAGE_PIN R21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[26]}]

set_property -dict {PACKAGE_PIN P20 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[27]}]

set_property -dict {PACKAGE_PIN N22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[28]}]

set_property -dict {PACKAGE_PIN N23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[29]}]

set_property -dict {PACKAGE_PIN M24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[30]}]

set_property -dict {PACKAGE_PIN M22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[31]}]

set_property -dict {PACKAGE_PIN U19 IOSTANDARD LVCMOS33} [get_ports base_ram_ce_n]

set_property -dict {PACKAGE_PIN T20 IOSTANDARD LVCMOS33} [get_ports base_ram_oe_n]

set_property -dict {PACKAGE_PIN U20 IOSTANDARD LVCMOS33} [get_ports base_ram_we_n]

set_property -dict {PACKAGE_PIN AF25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[0]}]

set_property -dict {PACKAGE_PIN AE25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[1]}]

set_property -dict {PACKAGE_PIN AE26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[2]}]

set_property -dict {PACKAGE_PIN AD25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[3]}]

set_property -dict {PACKAGE_PIN AD26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[4]}]

set_property -dict {PACKAGE_PIN AC22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[5]}]

set_property -dict {PACKAGE_PIN Y17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[6]}]

set_property -dict {PACKAGE_PIN AA18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[7]}]

set_property -dict {PACKAGE_PIN AA17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[8]}]

set_property -dict {PACKAGE_PIN Y25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[9]}]

set_property -dict {PACKAGE_PIN AA25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[10]}]

set_property -dict {PACKAGE_PIN AB26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[11]}]

set_property -dict {PACKAGE_PIN AB25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[12]}]

set_property -dict {PACKAGE_PIN AC26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[13]}]

set_property -dict {PACKAGE_PIN AC24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[14]}]

set_property -dict {PACKAGE_PIN AF17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[15]}]

set_property -dict {PACKAGE_PIN AE17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[16]}]

set_property -dict {PACKAGE_PIN AF18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[17]}]

set_property -dict {PACKAGE_PIN AE18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[18]}]

set_property -dict {PACKAGE_PIN AF19 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[19]}]

set_property -dict {PACKAGE_PIN R25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[1]}]

set_property -dict {PACKAGE_PIN R26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[0]}]

set_property -dict {PACKAGE_PIN AB22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[3]}]

set_property -dict {PACKAGE_PIN AD24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[2]}]

set_property -dict {PACKAGE_PIN AF24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[0]}]

set_property -dict {PACKAGE_PIN AE23 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[1]}]

set_property -dict {PACKAGE_PIN AF23 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[2]}]

set_property -dict {PACKAGE_PIN AE22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[3]}]

set_property -dict {PACKAGE_PIN AF22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[4]}]

set_property -dict {PACKAGE_PIN AE21 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[5]}]

set_property -dict {PACKAGE_PIN AE20 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[6]}]

set_property -dict {PACKAGE_PIN AF20 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[7]}]

set_property -dict {PACKAGE_PIN Y26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[8]}]

set_property -dict {PACKAGE_PIN W25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[9]}]

set_property -dict {PACKAGE_PIN W26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[10]}]