FIFO verilogIP 包括深度为1的fifo

包括普通同步FIFO和异步FIFO,均为first word fall through模式,同步fifo三种写法,异步fifo三种写法,可参数化配置,接口为fifo的基础接口

提供基础的testbench,两种fifo均在fpga上进行了验证

FIFO Verilog IP技术分析与应用研究

引言 FIFO(First-In-First-Out)是一种存储数据的缓冲区,数据按照先进先出原则排列,应用广泛,尤其在数字电路领域中。Verilog HDL是数字电路设计最常用的语言之一,通过利用其强大的特性,可以方便地设计FIFO。本文将围绕着FIFO Verilog IP展开详细的技术分析与应用研究。

一、FIFO Verilog IP的概述

FIFO Verilog IP包括深度为1的FIFO,普通同步FIFO和异步FIFO,均为first word fall through模式,同步FIFO有三种写法,异步FIFO也有三种写法。此外,FIFO Verilog IP可参数化配置,接口为FIFO的基础接口。基础的testbench已经提供,两种FIFO均在FPGA上进行了验证。

二、同步FIFO的设计

同步FIFO一般分为三种写法:无可避免的溢出、无溢出、复位。无可避免的溢出指当FIFO满时,新数据会覆盖最早的数据。无溢出指当FIFO满时,新数据不会写入FIFO。复位指当FIFO满时,旧数据会被覆盖且FIFO的读写指针将被重置。同步FIFO的示意图如下所示。

同步FIFO的设计需要考虑时序问题,以及按照先进先出原则排列数据。在设计时需要注意时钟的输入,以及读写指针的更新。同时,为了保证同步FIFO的正确性,在设计时需要考虑到FIFO的深度和写入和读出数据的速度匹配,以及输入和输出的时序匹配。

三、异步FIFO的设计

异步FIFO一般分为三种写法:无可避免的溢出、无溢出、复位。无可避免的溢出指当FIFO满时,新数据会覆盖最早的数据。无溢出指当FIFO满时,新数据不会写入FIFO。复位指当FIFO满时,旧数据会被覆盖且FIFO的读写指针将被重置。异步FIFO的示意图如下所示。

异步FIFO的设计需要考虑异步数据的读写,以及数据的接收和发送,并保证数据的正确性。需要注意的是,在设计异步FIFO时需要考虑到时序问题以及需要采用同步复位的方式,以保证FIFO的正确性。

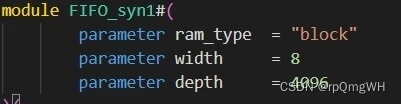

四、FIFO Verilog IP的参数化配置

FIFO Verilog IP提供很大的灵活性,使得用户可以根据需要进行参数化配置。可以通过修改FIFO的深度、写入接口和读出接口,实现FIFO Verilog IP的定制化配置。这样既可以满足不同的应用场景,也可以减少设计难度,提高设计效率。

五、FIFO Verilog IP的验证和应用

在FPGA上对FIFO Verilog IP进行了验证,结果表明FIFO Verilog IP的设计正确性和稳定性得到验证。在实际应用中,FIFO Verilog IP可以应用于不同的数字电路设计中,如数据传输、缓冲区等领域,为数字电路的设计和应用提供了方便、高效的解决方案。

六、总结

本文详细介绍了FIFO Verilog IP的概述、同步FIFO和异步FIFO的设计、参数化配置以及验证和应用。通过对FIFO Verilog IP的技术分析与应用研究,我们可以看出FIFO Verilog IP在数字电路设计中的重要作用和广泛应用前景。希望本文能够为数字电路设计人员提供有益的参考和帮助。

相关代码,程序地址:http://lanzouw.top/640501186835.html

2606

2606

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?