—— 因项目需要,苦学AD9361,制作不易,记得三连哦

——工程文件: 基于FPGA控制的AD9361载波信号发生器 提取码: miiu

硬件设备:Neptune SDR P210开发板

软件环境:vivado2018.3

频谱仪:AV4036A频谱分析仪

实验目的

针对传统载波信号发生器可配置性较差,难以更改信号参数,维护和升级困难等问题,本文对软件无线电(Software Defined Radio, SDR)和锁相环(phase-locked loop,PLL)的基础理论和电路展开研究,设计一种基于片上系统ZYNQ和射频收发捷变芯片AD9361的载波信号发生器。通过ZYNQ片上系统的PS端配置AD9361的锁相环参数,进行增益控制,数字滤波,数据接口设置等操作。通过PL端实现基带信号的数字化处理。

以2.4GHz的载波信号为例,基于FPGA控制的AD9361载波信号发生器设计通过成功发送2.4GHz频率的载波信号的情况,验证了载波信号发生器的功能。

一.理论分析

1. SDR无线收发系统结构

1.1 SDR无线收发机整体结构

SDR收发机主要由天线、射频前端、宽带A/D-D/A转换器、通用和专用数字信号处理器等各种模块组成,典型SDR收发机结构如图1.1.1所示。SDR的天线一般要覆盖比较宽的频段,例如1MHz~2GHz,要求每个频段的特性均匀。

图1.1.1 SDR收发机框图

射频前端由带通滤波器,放大器、混频器,本振、AGC控制电路等组成,在发射时主要完成上变频、滤波、功率放大等任务,接收时实现滤波、放大、下变频等功能。射频前端在中频进行数字化的结构框图1.1.2所示。由于SDR在中高频甚至是在射频进行数字化,这样可以减少模拟环节,使得前端引入的噪声更少,信号失真更小,电路更简洁。SDR和普通的窄带接收机相比,瞬时处理带宽更宽,动态范围更大、可扩展性更好。

图1.1.2 中频数字化框图

模拟信号进行数字化后的处理任务全由数字信号处理(Digital Signal Processing,DSP)软件承担。为了减轻通用DSP的处理压力,通常把A/D转换器传来的数字信号,经过专用数字信号处理器件(如数字下变频器,数字上变频器),降低数据流速率,并把信号变至基带后,再把数据送给通用DSP进行处理。通用DSP主要完成各种数据率相对较低的基带信号的处理,例如信号的调制解调,各种抗干扰,抗衰落。DSP的结构如图1.1.3所示。

图1.1.3 DSP框图

1.2 锁相环

锁相环(PLL)是一种闭环反馈系统,能够跟踪输出相位和参考时钟之间的固定相位关系。它广泛用于时钟恢复,作为 GPS 接收器中的频率合成器、抖动衰减器和芯片同步 [5,6]。PLL由鉴相器、环路滤波器和压控振荡器模块组成。这些模块相互连接,因此,输出信号的相位和频率被跟踪并反馈到鉴相器的输入端,在那里它与输入信号进行比较。这种互连的主要目的是将输出信号的相位和频率锁定到输入信号的相位和频率[7],锁相环的基本框图如图1.2.1所示。

鉴频鉴相器(PD-Phase Detector)通过比较输入信号和压控振荡器的输出信号的相位,输出一定的电压信号。输出的电压信号是关于这个信号相位差的函数。环路滤波器(LF-Loop Filter)可作为低通滤波器,滤除掉鉴相器输出电压中的高频分量和噪声,只保留低频分量。压控振荡器(Voltage-Controlled Oscillator,VCO)受环路滤波器输出电压的控制,压控振荡器的振荡频率向输出信号的频率靠拢,直到它们的频率相同。同时使VCO的输出信号和输入信号的相位保持着特定的关系,用来锁定相位。从VCO输出的信号通过反馈路径输入到相位比较器,与输入信号进行比较,形成反馈信号。反馈路径的目的是让系统试图保持输入信号和VCO输出信号的相位差稳定。

图1.2.1 锁相环的基本框图

AD9361含有两个完全相同的频率合成器,用于生成本振频率,一个用于接收器,一个用于发射器。锁相环(PLL)频率合成器采用分数分频,融入了完全集成式电压控制振荡器(VCO)和环路滤波器。在FDD模式下, TX PLL和RX PLL可以同时激活,发送和接收的频率可以相同或不同。AD9361的PLL合成频率框图如图1.2.2所示。

图1.2.2 AD9361的PLL频率合成框图

1.3 AD9361发送链路

AD9361发送部分由两个相同且独立控制的通道Tx Channel 1 和 Tx Channel 2 组成,同时共用一个通用型频率合成器。TX信号路径从数字接口接收IQ格式的12位补码数据,并且每个通道(I和Q)通过具有内插选项的完全可编程的128抽头FIR滤波器。之后进入到一系列附加的插值滤波器,这些滤波器在到达12位DAC之前提供附加的滤波和数据速率插值。转换为基带模拟信号时, I和Q信号将进行滤波,以移除采样伪像,然后进入上变频混频器使 I和Q信号将重新组合起来,并在载波频率下进行调制。组合信号还会通过模拟滤波器,进行额外的频带整形处理,然后再将信号传输至输出放大器。

发送器模块还为每个通道提供一个TX监控模块。该模块监视发送器输出,并通过一个未使用的接收器通道将其送回基带处理器(Baseband Processor,BBP),以实现信号监控。 TX监控器模块仅在接收器空闲的时分双工(Time Division Duplexing,TDD)模式下可用。当AD9361处于频分双工(Frequency Division Duplexing,FDD)模式时,FDD独立控制模式可以允许接收链和发射链独立使能。本次作品采用FDD模式,并未启动TX监控器模块。AD9361发送链框图如图1.3.1所示。

图1.3.1 AD9361发送链

1.4 LVDS数据接口

1.4.1低压差分信号模式

AD9361的数据传输路径采用低压差分信号(Low-Voltage Differential Signaling,LVDS)模式,与标准CMOS接口相比,在噪声环境中更具优势,能提供优越的开关性能和更高的数据速率。AD9361数据路径接口使用并行数据总线(P0和P1)在AD9361和BBP之间传输数据样本。总线传输使用简单的硬件握手信令来控制。在LVDS模式下,两条总线(P0和P1)都使用差分LVDS信号。AD9361的 LVDS接口便于连接具有LVDS功能的ASIC和FPGA。

AD9361在LVDS模式下的接口如图1.4.1所示。DATA_CLK是一个差分LVDS信号,作为接收数据路径的主时钟提供给BBP,BBP使用该主时钟作为接口数据传输和采样数据基带处理的时序参考。Rx_FRAME和Tx_FRAME高转换表示帧的开始,可以在突发开始时进行单个高电平转换,并在整个突发期间保持高电平。Rx_D[5:0]和Tx_D[5:0]是差分LVDS数据总线,由六个差分对组成。数据以成对数据字的形式在12位数据总线上传输。ENABLE 和TXNRX由BBP向AD9361驱动,以在TDD模式下提供数据传输突发控制。在正常FDD模式下,TXNRX信号被忽略,但必须保持在有效的逻辑电平。

图1.4.1 AD9361在LVDS模式下的接口框图

1.4.2 双端口全双工模式

双端口全双工LVDS模式通过SPI写寄存器来使能。在这种模式下,P0(Tx_D[5:0])和P1(Rx_D[5:0])均为LVDS信号,数据总线(D[11:0])被分成独立的子总线(Rx_D[5:0]和Tx_D[5:0])。每个子总线同时工作,允许BBP和AD9361之间全双工发送和接收数据。LVDS模式下的收发数据时序图如图1.4.2所示。

发送数据(Tx_D[5:0])、FB_CLK和Tx_FRAME由BBP驱动,FB_CLK和Tx_D[5:0]、Tx_FRAME之间的建立和保持时间足够以允许AD9361使用FB_CLK捕获Tx_D[5:0]和Tx_FRAME。Tx_D[5:0]采用二进制补码格式,每个数据包中的第一个6位字包含MSB,第二个6位字包含LSB。

接收数据(Rx_D[5:0])、DATA_CLK和Rx_FRAME由AD9361驱动,DATA_CLK和Rx_D[5:0]、Rx_FRAME之间的建立和保持时间足够以允许BBP使用DATA_CLK捕获Rx_D[5:0]和Rx_FRAME。接收采样数据采用二进制补码格式,每个数据包中的第一个6位字包含MSB,第二个6位字包含LSB。

图1.4.2 LVDS模式下的收发数据时序图

1.5 AD9361接收链路结构

AD9361接收部分有两个独立控制的通道Rx Channel 1 和 Rx Channel 2 可以接收来自不同来源的信号,从而允许该设备在共享通用频率合成器的同时在多输入多输出(Multiple Input Multiple Output,MIMO)系统中使用。每个通道具有三个输入,这些输入可以多路复用到信号链,从而使AD9361适用于具有多个天线输入的分集系统。接收链数据首先经过低噪声放大器(Low Noise Amplifier,LNA),然后是同相(I)和正交(Q)放大器,混频器和频带整形滤波器,可将接收到的信号下变频为基带以进行数字化。

AD9361 RX 信号路径将下变频信号(I 和 Q)传递到基带接收器部分,基带RX信号路径由两个可编程模拟低通滤波器,一个12位ADC和四级数字抽取滤波器组成。四个抽取滤波器中的每一个都可以被旁路,每个低通滤波器的转折频率是可编程的。当工作频率等于或低于3 GHz时,任何LNA输入端口都将提供最佳性能, 当工作频率高于3 GHz时,利用Rx1A和Rx2A LNA输入端口获得最佳性能,B和C端口在3 GHz以上时性能会下降,本作品要求工作频率为2.4GHz,因此我们采用工作在全频段性能较好的A端口。AD9361接收链结构如图所示。

二.发生器系统实现

2.1 发生器系统总体结构

2.1.1硬件设计

本次作品采用Neptune SDR P210开发板,开发板主要由XC7Z020+1个DDR3+AD9361+1个QSPIFLASH的最小系统构成。开发系统的总体结构如图所示。

2.1.2系统总体通信框图

系统总体通信框图如图2.1.2所示。

当前SoC芯片的复杂度越来越高,芯片内部集成的模块也越来越多,而总线 是这些模块之间互相通信必不可少的组件之一[8]。随着SoC性能的不断提高,对总线性能的要求也越来越高,传统的APB(Advanced PeripheraI Bus)、AHB(Advanced High Performance Bus)等总线无法满足总线传输中高速和低延时的要求[9]。AXI总线有五条独立的传输通道,具有读与写通道独立、地址与数据通道独立的优点,支持burst传输,支持非对齐传输,支持outstanding 传输和out of order传输。AXI总线具有高速、可支持突发传输、低延时等特征,架构和性能都有着很大的优势,非常适合用于 SoC 芯片总线设计[10]。

AD9361芯片的数字接口有3种,分别是串行外设接口(serial peripheral interface,SPI)、通用输入输出( general purpose inputloutput, GPIO)接口和高速数字接口,其中 SPI接口用于传输控制信息,GPIO接口用于读取AD9361 的工作状态并对 AD9361进行状态控制,高速数字接口用于和FPGA之间传输基带数据。使用 FPGA 的逻辑资源将GPIO,SPI等各个功能模块组装成带有AXI总线的知识产权( intellectual property,IP)核,并通过 FPGA 的I/O 接口完成与 AD9361射频芯片之间信息数据的交互[11]。

图2.1.2 系统总体通信框图

2.2 PL端实现原理

2.2.1AD9361数据流图

AD9361数据流图如图2.2.1所示。

将PS端生成2.4GHZ的载波信号,通过AXI总线交互传到PL端,然后利用DAC模块处理后生成frame(识别数据有效的标志位)和I/Q两路信号,通过ODDR模块转换成AD9361可识别的数据,最后利用FPGA将单端数据转换为以差分对传输的数据。

图2.2.1 AD9361数据流图

2.2.2Output Double Data Rate(ODDR)

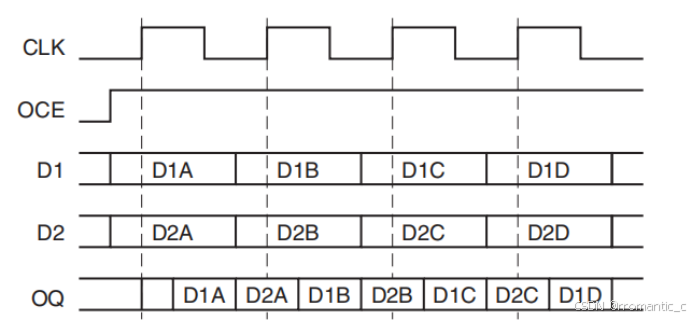

ODDR有两种工作模式,OPPOSITE_EDGE模式和SAME_EDGE模式。本次设计采用SAME_EDGE模式,SAME_EDGE模式的时序图如图2.6所示。在时钟CLK上升沿同时采集D1、D2的数据,OQ在时钟上升沿输出采集的D1数据,时钟的下降沿输出采集的D2数据。该模式可以在相同的时钟沿将数据送给IOB(Input/Output Block)可以避免建立时间违规,并允许用户使用最小的寄存器来执行更高的DDR频率来进行寄存器的延迟。

图2.6 ODDR在SAME_EDGE模式下的时序图

2.2.3直接数字频率合成(DDS)

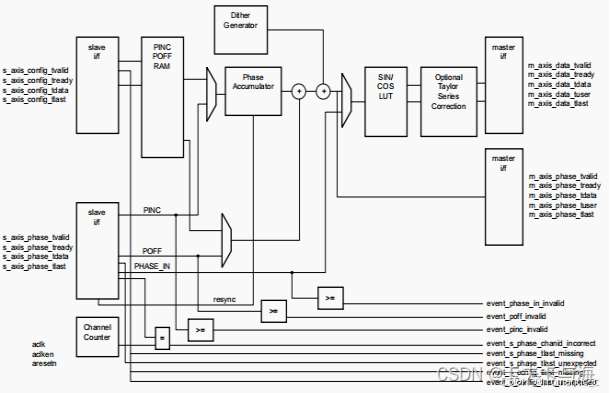

直接数字频率合成(Direct Digital Frequency Synthesizer,DDS)是一种基于全数字技术,从相位概念出发直接合成所需波形的频率合成技术,可以根据我们设定的参数,快速、准确地生成各种频率的正弦波、余弦波等波形信号。具有相对带宽大,频率转换时间短、分辨率高和相位连续性好等优点。较容易实现频率、相位以及幅度的数控调制,广泛应用于通信领域。Vivado 的DDS IP 核则是 AMD(Xilinx)公司在 Vivado 开发环境中提供的一个功能强大的 IP 核,用于实现 DDS 功能。

Vivado DDS IP 核的基本架构如图2.7所示。从图中我们可以看到DDS IP核主要由5部分组成,其中DDS核心为相位累加器(Phase Accumulator)和LUT查找表(SIN/Cos LUT)。相位累加器实现查找表地址的产生,LUT查找表用来存储输出波形。抖动产生器(Dither Generator)和泰勒级数矫正产生模块(Optional faylor Series Correction)主要用来改善无杂散动态范围(Spurious-Free Dynamic Range,SFDR)。抖动产生器通过产生随机的噪声来使得量化误差随机化,从而提高 SFDR,泰勒级数矫正则是利用泰勒级数展开的方法对相位误差进行矫正,提高信号的质量。AXI4接口实现相位累加字配置,多通道配置,相位累加器输出和波形数据输出。在需要同时生成多个不同频率的波形信号时,可以使用多通道输出模块(Channel Counte)。

图2.7 DDS IP核的基本架构

DDS IP核的配置如图2.8所示。

图2.8 DDS IP核的配置

2.2.4FPGA顶层模块框图

FPGA顶层模块框图如图2.9所示。

图2.9 FPGA顶层模块框图

2.2.5FPGA顶层设计

2.2.5.1FPGA顶层文件的代码

FPGA顶层文件的代码如下:

`timescale 1ns / 1ps

module system_top(

//zynq子系统

inout [14:0]DDR_addr ,

inout [2:0]DDR_ba ,

inout DDR_cas_n ,

inout DDR_ck_n ,

inout DDR_ck_p ,

inout DDR_cke ,

inout DDR_cs_n ,

inout [3:0]DDR_dm ,

inout [31:0]DDR_dq ,

inout [3:0]DDR_dqs_n ,

inout [3:0]DDR_dqs_p ,

inout DDR_odt ,

inout DDR_ras_n ,

inout DDR_reset_n ,

inout DDR_we_n ,

inout FIXED_IO_ddr_vrn ,

inout FIXED_IO_ddr_vrp ,

inout [53:0]FIXED_IO_mio ,

inout FIXED_IO_ps_clk ,

inout FIXED_IO_ps_porb ,

inout FIXED_IO_ps_srstb ,

.

.

.

.

.

.

.

代码太多

部分省略

.

.

.

.

.

.

.

assign mmcm_data_clk_160m = mmcm_clk_out_160m & mmcm_locked;

assign mmcm_data_clk_320m = mmcm_clk_out_320m & mmcm_locked;

endmodule

2.2.2.2AD9361接口文件代码

AD9361接口文件代码如下:

`timescale 1ns / 1ps

module ad9361_lvds(

// system signals

input wire cfg_done ,

output wire data_clk ,//(输出时钟信号)接收和发送数据的时钟

// ad936x rx path signals

input wire rx_clk_in_p ,//接收9361数据的时钟信号(差分)

input wire rx_clk_in_n ,

input wire [5:0] rx_data_in_p ,//接收来自9361的数据(每个data_clk边沿接收6bit数据)(差分)

input wire [5:0] rx_data_in_n ,

input wire rx_frame_in_p ,//rx frame接收控制信号(差分)

input wire rx_frame_in_n ,

// ad936x tx path signals

output wire tx_clk_out_p ,//发送数据时钟信号(差分)

output wire tx_clk_out_n ,

output wire tx_frame_out_p ,//tx frame 发送控制信号(差分)

output wire tx_frame_out_n ,

output wire [5:0] tx_data_out_p ,//发送的数据(差分)

output wire [5:0] tx_data_out_n ,

.

.

.

.

.

代码太多

部分省略

.

.

.

.

.

//2.将时钟 tx_clk 转化为差分时钟输出:tx_clk_out_p/n

OBUFDS #(

.IOSTANDARD("DEFAULT"), // Specify the output I/O standard

.SLEW("SLOW") // Specify the output slew rate

) OBUFDS_data_clk_inst (

.O(tx_clk_out_p), // Diff_p output (connect directly to top-level port)

.OB(tx_clk_out_n), // Diff_n output (connect directly to top-level port)

.I(tx_clk) // Buffer input

);

//tx_clk signal --- end

endmodule

2.3 PS端实现原理

2.3.1 PS端实现原理

Zynq-7020基于 Xilinx SoC架构,在单个设备上集成了功能丰富的双核 ARM CortexTM-A9 MPCore 处理系统(PS)和 Xilinx可编程逻辑(PL),实现了灵活性,可配置性和性能的完美结合。双核ARM Cortex-A9 MPCore 处理器是PS的核心,它还包括片内存储器、外部存储器接口和一组丰富的I/O外设。VIVADO内集成了ZYNQ7 Processing System的IP核,通过PS端配置寄存器组,进行GPIO,SPI,AD9361初始化,配置AD9361基本参数等操作,生成2.4GHZ的载波信号。

ZYNQ7 Processing System的IP核的配置如图2.3所示。

图2.3 ZYNQ7 Processing System的IP核配置

2.3.1 PS端/SDK代码

SDK代码如下:

void invalid();

void flush();

struct ad9361_rf_phy *ad9361_phy;

uint32_t sample_rate = 15.36e6; //******

uint64_t tx_lo_freq = 2400e6;//******

uint64_t rx_lo_freq = 2400e6;//*****

uint32_t bandwidth = 12e6; //*****

.

.

.

.

.

.

代码太多

部分省略

.

.

.

.

.

.

void invalid()

{

Xil_DCacheInvalidateRange(POSITION_INFO_BASEADDR, 18*4);

}

void flush()

{

Xil_DCacheFlushRange(POSITION_INFO_BASEADDR, 18*4);

}

三 仿真验证

本次作品采用的是Vivado的在线逻辑分析仪(Integrated Logic Analyzer,ILA),其借用了传统逻辑分析仪的理念以及大部分的功能,并利用FPGA中的逻辑资源,将这些功能植入到FPGA的设计当中。通过观察发送的I,Q两路信号,进而确认波形是否有明显失真。设置参数为dac_data_i1,dac_data_q1表示发送的I,Q两路信号。由图3.1可知,波形无明显失真。

图3.1 发送数据波形图

四. 实物验证

由图4.1可知,发送的频率为2.4GHz,该作品满足产生载波信号频率为2.4GHz的要求。

图4.1 发送频率的频谱图

参考文献

[1] 雷鹏;罗斐翔;张博诚等基于软件无线电的数字信号处理综合实验平台[J].工业和信息化教育,2016(07).

[2] 楼才义;;徐建良;;杨小牛.软件无线电原理与应用[M].电子工业出版社,2014.

[3] 王奇.基于GNURadio的软件无线电平台研究[D].哈尔滨工业大学,2011(05).

[4] 吕海清,颜凯,赵保磊,等.基于软件无线电的多载波信号发生器设计与实现[C]//天津市 电子学会.第三十七届中国(天津)2023’IT、网络、信息技术、电子、仪器仪表创新学术会议论文集.天津光电通信技术有限公司

,2023:4.DOI:10.26914/c.cnkihy.2023.022913.

[5] Razavi, B.: "Design of Analog CMOS Integrated Circuits," McGraw-HILL, 2001.

[6] A. Singhal, C. Madhu and V. Kumar, "Designs of All Digital Phase Locked Loop," 2014 Recent Advances in Engineering and Computational Sciences (RAECS), Chandigarh, India, 2014, pp. 1-5, doi: 10.1109/RAECS.2014.6799523.

[7] A. Godave, P. Choudhari and A. Jadhav, "Comparison and Simulation of Analog and Digital Phase Locked Loop," 2018 9th International Conference on Computing, Communication and Networking Technologies (ICCCNT), Bengaluru, India, 2018, pp. 1-4, doi: 10.1109/ICCCNT.2018.8494198.

[8] 马鹏;刘佩;张伟;.基于UVM的AMBA总线接口通用验证平台[J].计算机系统应 用,2021(07).

[9] 刘达;倪伟;徐春琳;.基于UVM的AXI总线验证IP设计[J].微电子学,2019(05).

[10] 李晨阳;宋澍申;王涛;黄坤超;.一种基于UVM的高层次化验证平台设计[J].微电子学 与计算机,2019(06).

[11] 禹永植,夏泽宇,刘宇.一种搭载FPGA和AD9361的软件无线电平台实现方法[J].应用科 技,2023,50(04):90-95.

6523

6523

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?