文章目录

88E1111 器件简介

88E1111 器件有三种应用场景:88E1111 Device used in Copper Application (RJ-45)、88E1111 Device used in Fiber Application (Fiber Optics)、88E1111 RGMII/GMII MAC to SGMII MAC Conversion (3-Speed SFP)。以下主要介绍第一种应用场景。如下图所示:

【注】

1000BASE-X 表示千兆光纤接口,1000BASE-T 表示千兆铜介质双绞线接口。

88E1111 器件支持 GMII、RGMII、SGMII、TBI 和 RTBI 接口,可以直接连接到 MAC/Switch 端口。

88E1111 Device MAC Interface Pins 如下表所示:

| 88E1111 Device Pins | GMII | RGMII | SGMII |

|---|---|---|---|

| GTX_CLK | GTX_CLK | TXC | |

| TX_CLK | |||

| TX_ER | TX_ER | ||

| TX_EN | TX_EN | TX_CTL | |

| TXD[7:0] | TXD[7:0] | TD[3:0] | |

| RX_CLK | RX_CLK | RXC | |

| RX_ER | RX_ER | ||

| RX_DV | RX_DV | RX_CTL | |

| RXD[7:0] | RXD[7:0] | RD[3:0] | |

| CRS | CRS | ||

| COL | COL | ||

| S_IN± | TX | ||

| S_CLK± | RXCLK | ||

| S_OUT± | RX |

【注】

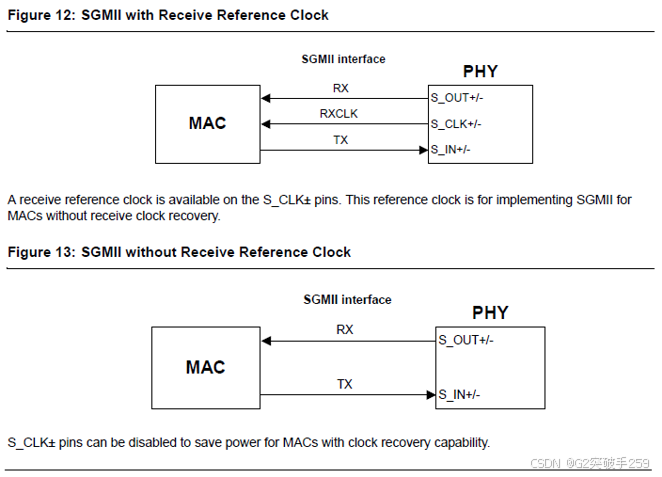

SGMII 模式下,88E1111 设备不需要 TX_CLK 输入,因为它从输入数据中恢复这个时钟。这种特性的优点是减少引脚数,电路板上的走线数量,以及 EMI 和噪声的产生。在接收端,有两种工作模式:一种是给 MAC 提供接收时钟,一种是不提供接收时钟。对于没有时钟恢复能力的 MAC,需要设置接收时钟。Intel FPGA Arria 10 器件的 MAC 有时钟恢复功能,所以不需要提供接收时钟。两种工作模式如下图所示:

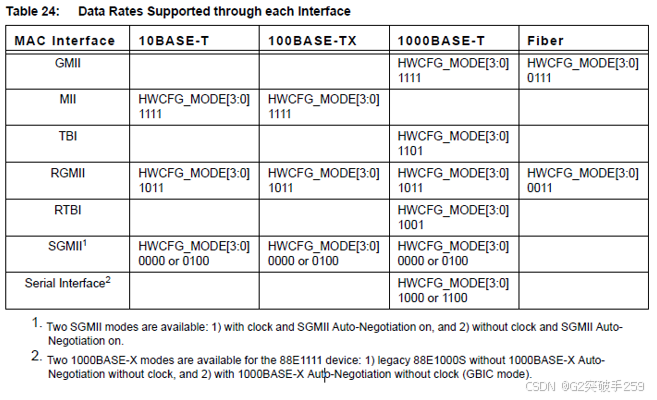

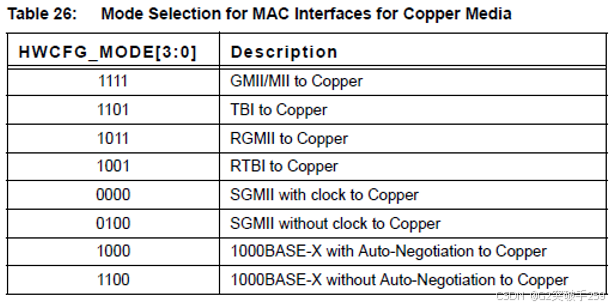

不同模式的 HWCFG_MODE[3:0] 寄存器配置如下图所示:

【注】

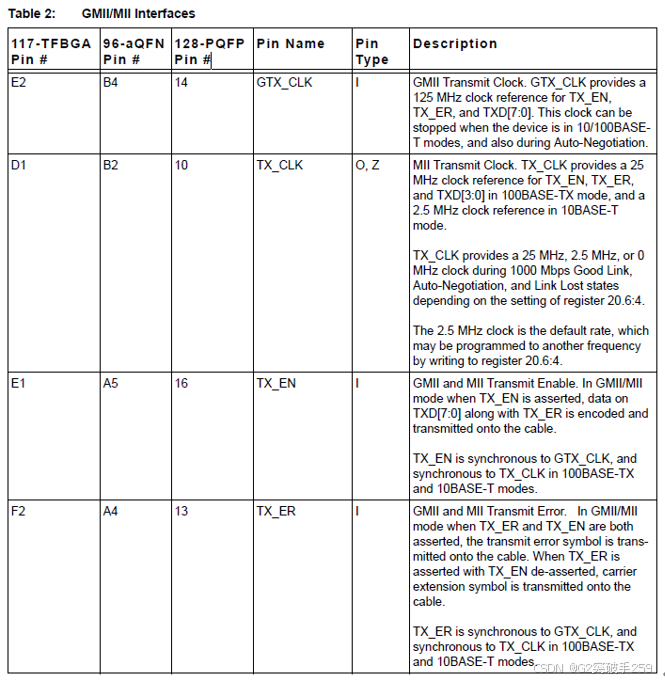

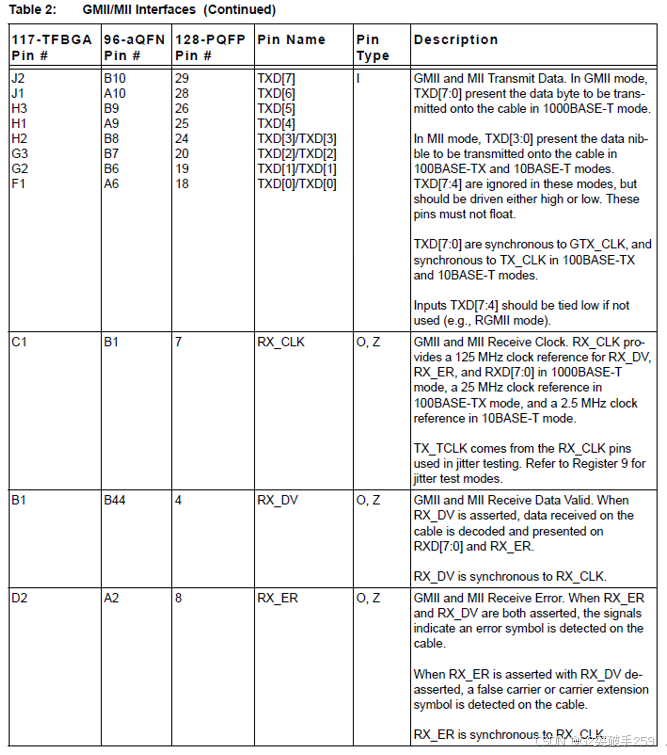

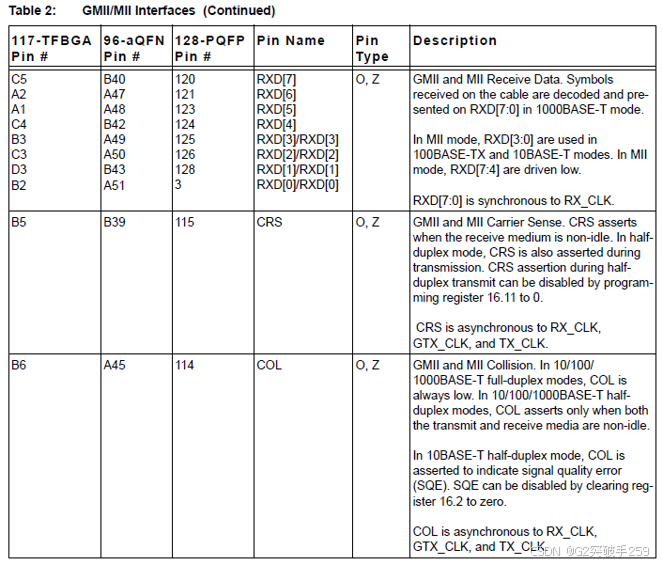

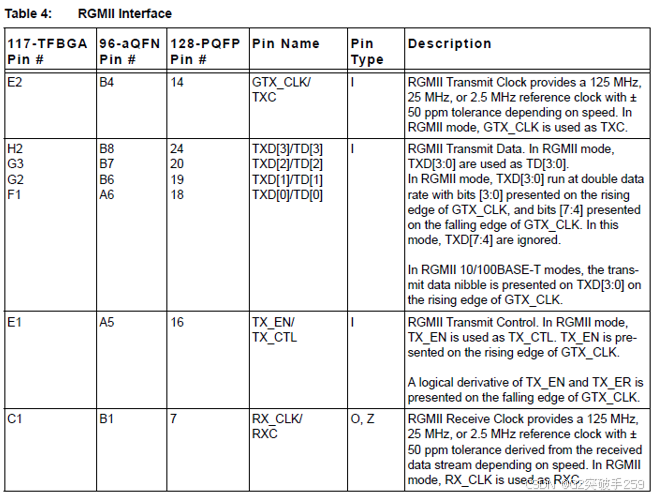

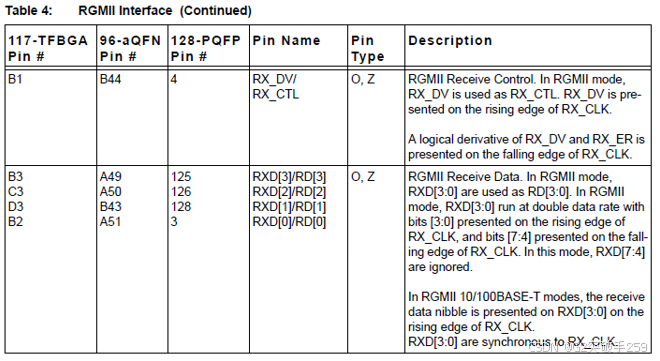

以下是 GMII、RGMII、SGMII 详细的接口介绍:

GMII Interface

RGMII Interface

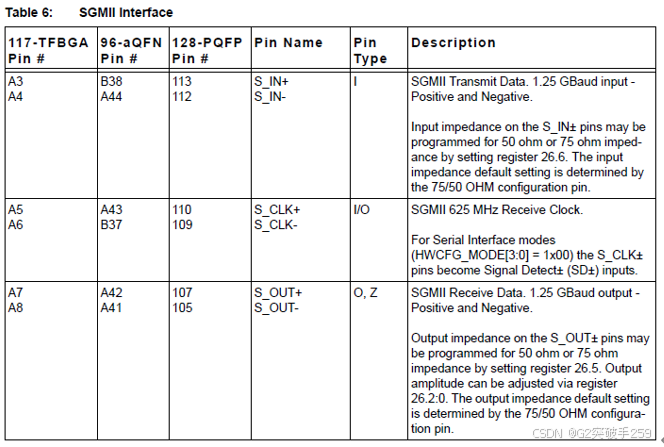

SGMII Interface

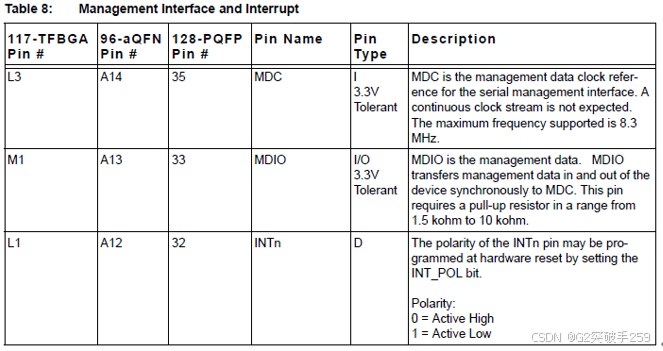

Management Interfaces and Interrupt

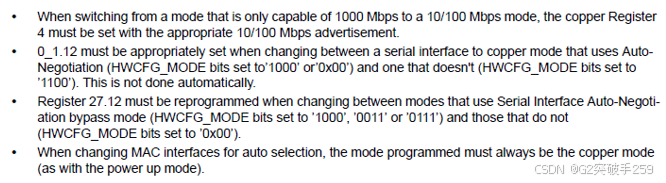

模式切换

上电时选择的工作模式可以通过写入寄存器来改变。任何模式更改都必须进行软件重置。当软件复位完成后,操作可以在新的模式下开始。但对于某些模式更改,需要进行额外的寄存器更改,这些更改不会自动完成。如下所示:

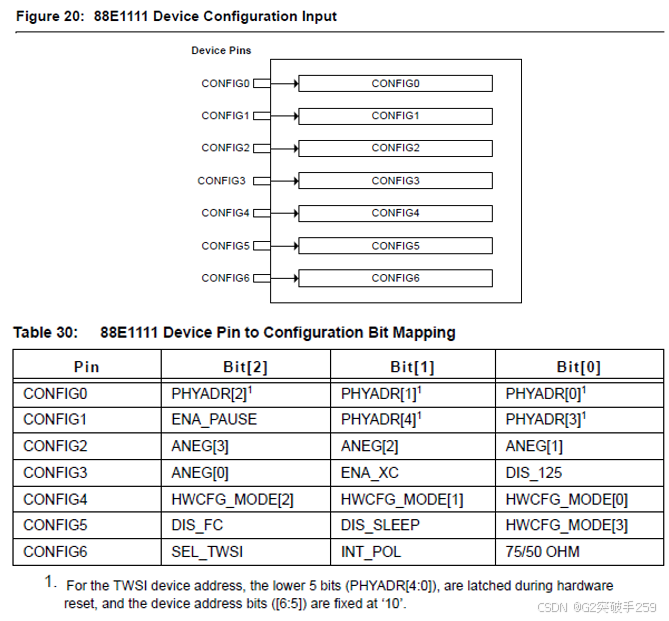

硬件配置

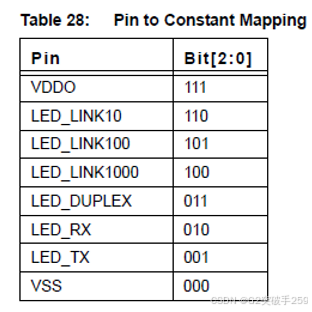

88E1111 如果硬件配置得当,正常来说是不需要软件进行再次配置的,硬件可以通过配置管脚配置选项,如物理地址、PHY 操作模式、自动协商、MDI 交叉(ENA XC)和物理连接类型等。CONFIG[6:0] 引脚必须绑定到表 28 中所示的一个引脚上,根据所选择的配置选项,它们不可以悬空。

根据数据手册可以看到,总共有七个 CONFIG 管脚可以对 PHY 芯片进行配置,每个管脚有 3bit 映射,每个 bit 都有不同的含义。

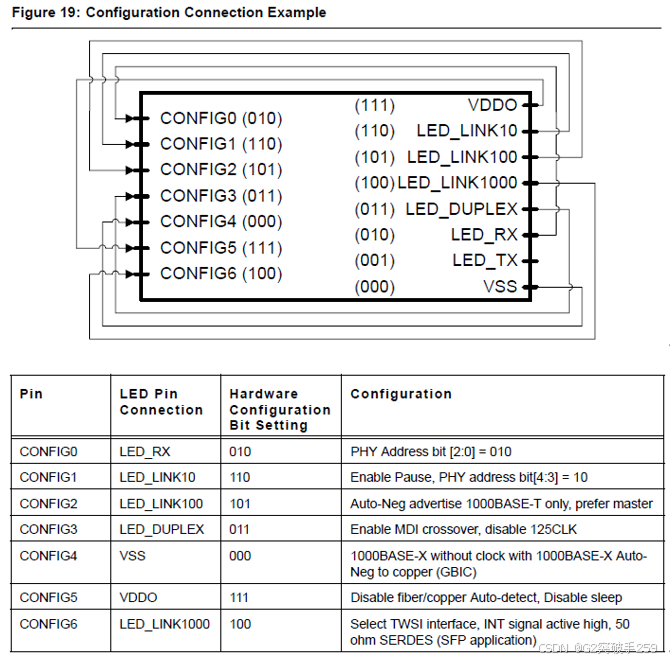

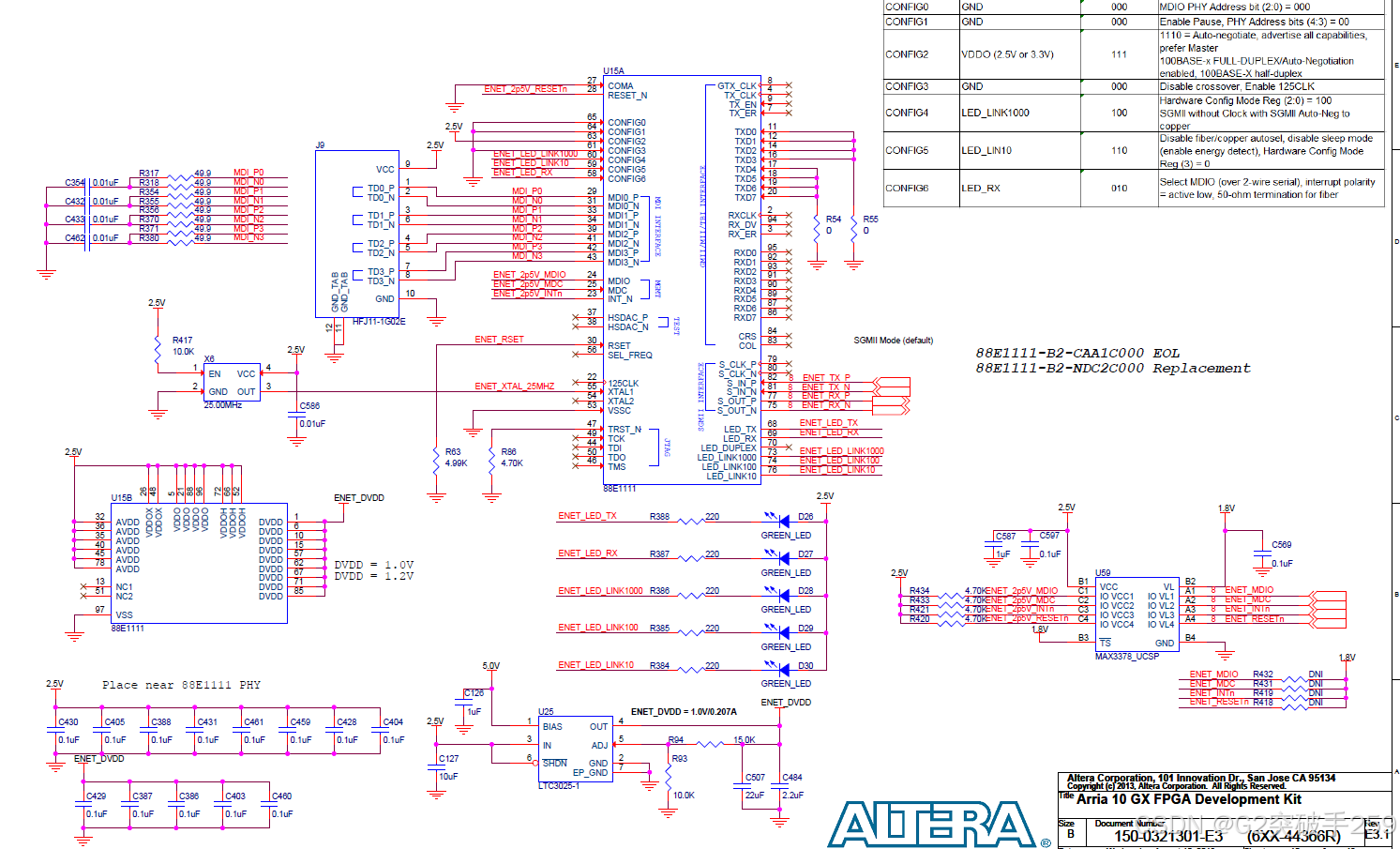

硬件通过将这 7 根 CONFIG 管脚接上表 28 中的不同的管脚,来配置管脚对应的 bit 值。88E1111 提供了一个映射表,不同的管脚对应不同的值。如下图所示:

将表 28 中对应不同值的管脚连接到 CONFIG[6:0] 上以后,就能对 PHY 芯片的模式进行硬件配置,88E1111 的数据手册上提供了一个例子,展示了该如何配置硬件配置管脚,将 CONFIG0 直接连接 LED_RX 管脚,就会将 PHY 地址 bit[2:0] 配置为 010,将 CONFIG2 接到 LED_LINK100 管脚就能将模式配置为自协商 1000BASE-T 的模式。

下表为 GMII、RGMII、SGMII 在 1000BASE-T 模式时 CONFIG[6:0] 管脚的配置方式。

| Pin | GMII | RGMII | SGMII(without CLK) |

|---|---|---|---|

| CONFIG0 | VDDO | VDDO | VDDO |

| CONFIG1 | VSS | VSS | VSS |

| CONFIG2 | LED_LINK100 | LED_LINK100 | LED_LINK100 |

| CONFIG3 | LED_RX | LED_RX | LED_RX |

| CONFIG4 | VDDO | LED_DUPLEX | LED_LINK1000 |

| CONFIG5 | VDDO | VDDO | LED_LINK10 |

| CONFIG6 | LED_RX | LED_RX | LED_RX |

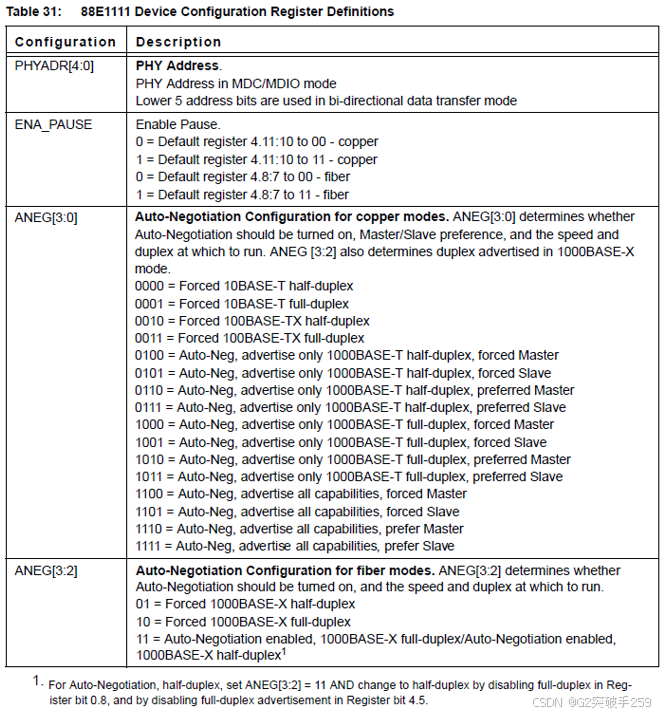

88E1111 设备配置寄存器的详细描述如下表所示:

PHYADR[4:0]

PHY Address(物理地址)。MDC/MDIO 模式下的 PHY 地址。低 5 位地址用于双向传输模式。如果只有一个 PHY 芯片,这个地址可以自己定义。

ENA_PAUSE

Enable Pause

本文讨论的是 Copper Application,所以是以下配置

0 = Default register 4.11.10 to 00 - copper

1 = Default register 4.11.10 to 11 - copper

这个是以太网 PAUSE 帧功能的关闭和开启使能。在 IEEE802.3 协议中规定中,PAUSE 帧是一种控制帧,用于控制数据流停止发送,在 MAC 发送侧产生,在 MAC 接收侧解析并执行。当此端设备输入数据量过大,无法及时处理时会在此端发送侧 MAC 产生 PAUSE 帧,发给对端,要求对端在一定时间内停止发送数据。PAUSE 帧操作实现了一种简单的停-等式流量控制机制。可以防止瞬时过载导致缓冲区溢出时不必要的帧丢失。在全双工 MAC 控制框架下,流量控制机制是通过 PAUSE 功能实现的。如果某个端口要停止帧的接收,可以发送一个带有时间参数的 PAUSE 帧,参数指示全双工链路对方在开始发送数据前需要等待的时间,收到 PAUSE 帧的设备通过简单的解析,就可以确定停止发送的时长。当链路对方接收到 PAUSE 帧后,在参数指定的时间内停止发送数据。当指定时间超出,或原拥塞端口重新发出操作参数为 0 的 PAUSE 帧,链路对方从暂停的位置继续发送数据帧。

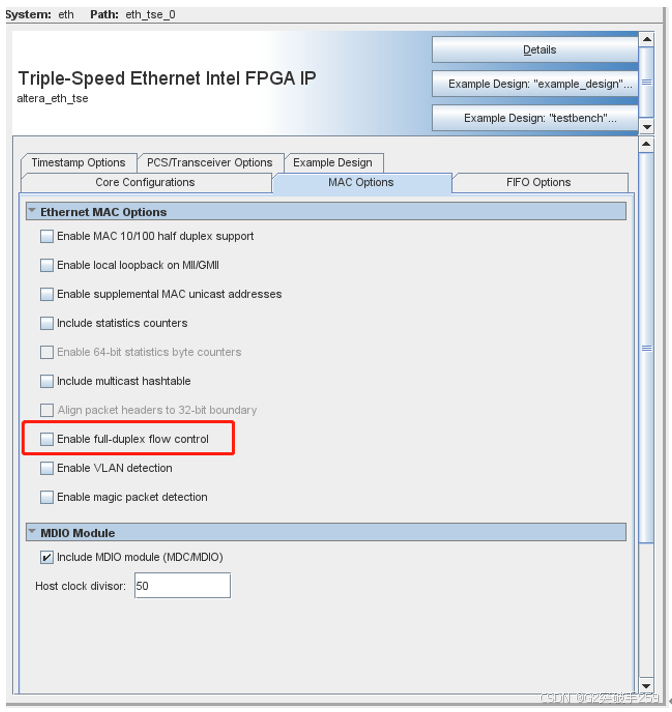

当 MAC 侧开启全双工流量控制时,此使能需要置 1,否则置 0。Intel FPGA IP 配置如下图所示:

此处没有开启全双工流量控制,所以 ENA_PAUSE 配置为 0。

如需开启此功能,具体配置方式和区别参考 Intel 官方 ug:

https://www.intel.com/content/www/us/en/docs/programmable/683402/15-0/introduction.html

ANEG[3:0]

此文档采用 1000BASE-T,Auto-Negotiation(自适应模式),全双工,preferred Master 和 preferred Slave 设置均可,PHY 和 MAC 会自动协商。默认将 PHY 芯片配置为主机,所以配置为以下值。

1010 = Auto-Neg, advertise only 1000BASE-T full-duplex, preferred Master

ENA_XC

Enable Crossover。ENA_XC 选择是否使能 MDI 交叉功能。如果关闭该功能,则设备采用 MDI 配置。

0 = disable

1 = enable

网线的标准分为 A 类接法(TIA/EIA-568-A)和 B 类接法(TIA/EIA-568-B)。直连网线(最常见的网线,又叫正线)是网线两头都是 A 类接法或者都是 B 类接法;交叉网线(又叫反线)是网线两头是用不同类的接法组成的。

MDI 是快速以太网 100BASE-T 定义的与介质有关接口(Media Dependent interface)。端口自动翻转(Auto MDI/MDIX)能让网络设备自动识别交叉线或者直连线,并能进行线序跳转,达到无视物理线序,能在不同设备间传输信号。

默认开启,置 1。

DIS_125

0 = 使能 125MHz 时钟

1 = 禁用 125MHz 时钟

88E1111 芯片 125CLK 引脚可以生成用于 MAC 设备的通用 125MHz 时钟参考。需要使用,置 0。

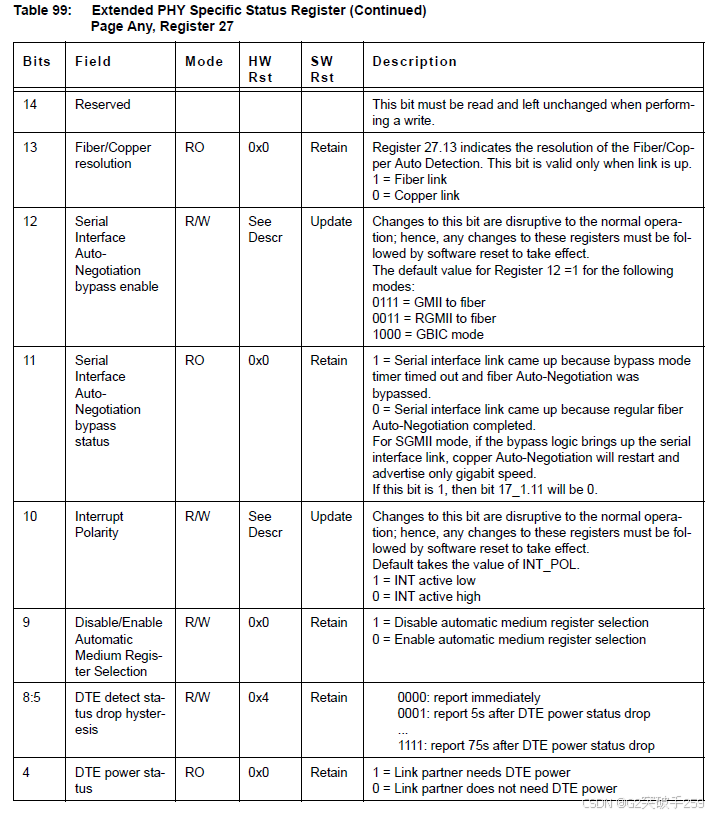

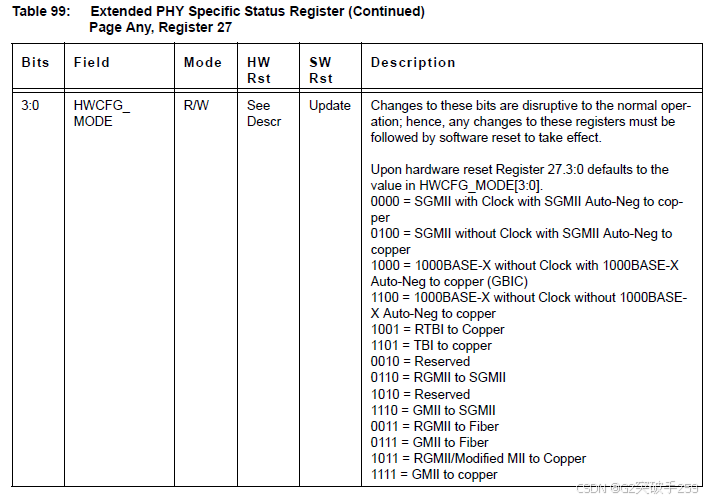

HWCFG MODE[3:0]

HWCFG_MODE[3:0] 表示 88E1111 的工作模式。GMII、RGMII、SGMII 的配置如下所示:

0100 = SGMll without Clock with SGMl Auto-Neg to copper

1011 = RGMll to copper

1111 = GMll to copper

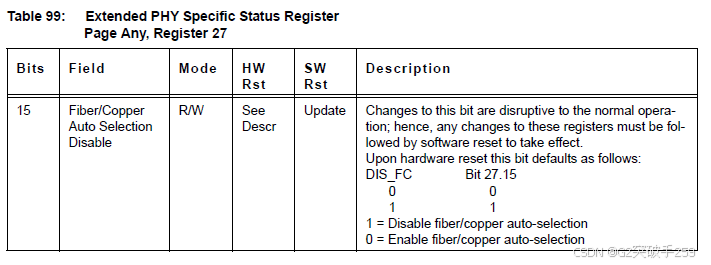

DIS_FC

Disable fiber/copper interface。DIS_FC 用于开启或关闭光纤/RJ-45 接口的自动选择功能(PHY 根据在这些线路上检测到的能量自动在光纤和 RJ-45 接口之间切换,如果 Auto-Negotiation(自适应)已经完成)。置 1。

0 = Enable fiber/copper auto selection

1 = Disable fiber/copper auto selection

DIS_SLEEP

Energy detect。DIS_SLEEP 用于开启或关闭能量检测。置 1。

0 = Enable energy detect

1 = Disable energy detect

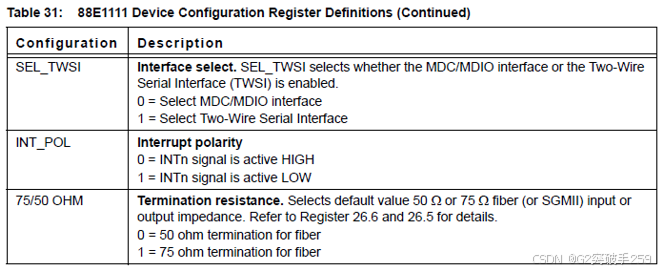

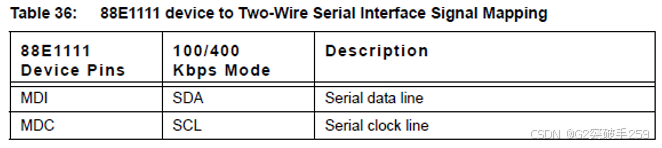

SEL_TWSI

Interface select。SEL_TWSI 选择是否启用 MDC/MDIO 接口或 TWSI(Two-Wire Serial Interface 两线串行接口)。置 0。

0 = Select MDC/MDIO interface

1 = Select Two-Wire Serial interface

INT_POL

Interrupt polarity(中断极性)调整使能逻辑。置 1。

0 = INTn signal is active HlGH

1 = INTn signal is active LOW

75/50 OHM

Termination resistance(终端电阻)。选择默认值 50Ω 或 75Ω 光纤(或SGMII)的输入或输出阻抗。详情请参阅手册寄存器 26.6 和寄存器 26。置 0。

0 = 50 ohm termination for fiber

1 = 75 ohm termination for fiber

硬件参考设计

Arria® 10 GX FPGA 开发套件主板原理图 DK-DEV-10AX115S-A

软件配置

查看 88E1111 的数据手册,我们可以看到,88E1111 可以通过两种方式进行寄存器配置,一种是 MDIO 协议,一种是 IIC 协议,IIC 支持 100K 或 400K 的速率,当软件寄存器写入以后,板卡需要进行软复位操作,PHY 地址默认使用五个 bit 表示,地址由硬件配置地址管脚高低电平来确定。

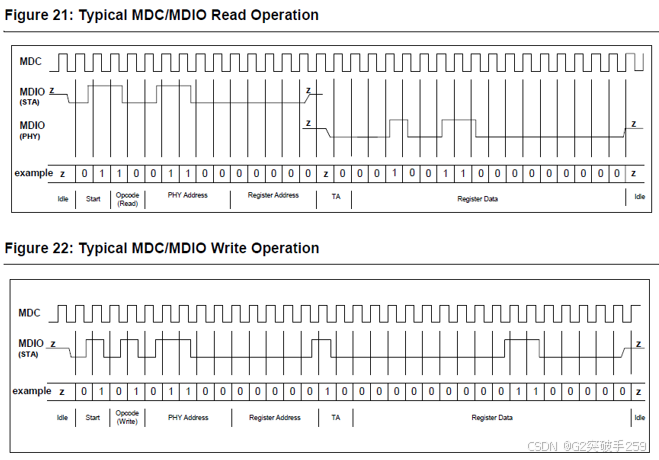

MDIO 协议配置

管理接口通过 MDC 和 MDIO 引脚提供对内部寄存器的访问,符合 IEEE 802.3u clause 22。MDC 是管理数据时钟输入,它可以从 DC 运行,最大速率为 8.3 MHz。在高 MDIO 扇出时,最大速率可能会根据输出负载而降低。MDIO 是管理数据的输入/输出,是一个双向信号,与 MDC 同步运行。MDIO 引脚需要一个在 1.5~10kohm 范围内的上拉电阻,该电阻在空闲期间将 MDIO 拉高,并且在硬件复位序列期间配置 PHY 地址。有关如何配置 PHY 地址的更多信息,请参阅第 63 页的“硬件配置”。管理接口上的典型读写操作如图 21 和图 22 所示。实现了所有必需的串行管理寄存器以及几个可选寄存器。寄存器的描述可以在寄存器描述中找到。

IIC 协议配置

88E1111 支持 TWSI(Two-wire Serial Interface)接口。TWSI 采用串行数据线(SDA)和串行时钟线(SCL),通过 CONNFIG6 bit 2 使能总线接口。并且,在数据传输过程中,MDC/MDIO 引脚被用作总线接口连接。对于 TWSI 设备地址,低 5 位(PHYADR[4:0])在硬件复位期间被锁存,设备地址位([6:5])固定在 ‘10’。SDA 是一条双向线,而 SCL 线则不是。SDA 需要一个 1.5 欧姆的上拉电阻。88E1111 设备作为总线接口的 Slave 端口运行,所有对 Slave 的引用都指向 88E1111 设备。88E1111 设备将在硬件复位后 5 毫秒可用于读/写操作。

88E1111 设备 TWSI 的特点是:

7 位设备地址/ 8 位数据传输

100 Kbps 模式

400 Kbps 模式

使用 TWSI 的多个设备可以共享和合并 MDC 和 MDIO 线路,并通过一个从 4.5kohm 到 10kohm 的电阻拉起来。88E1111 设备将在硬件复位后 5 毫秒可用于读/写操作。

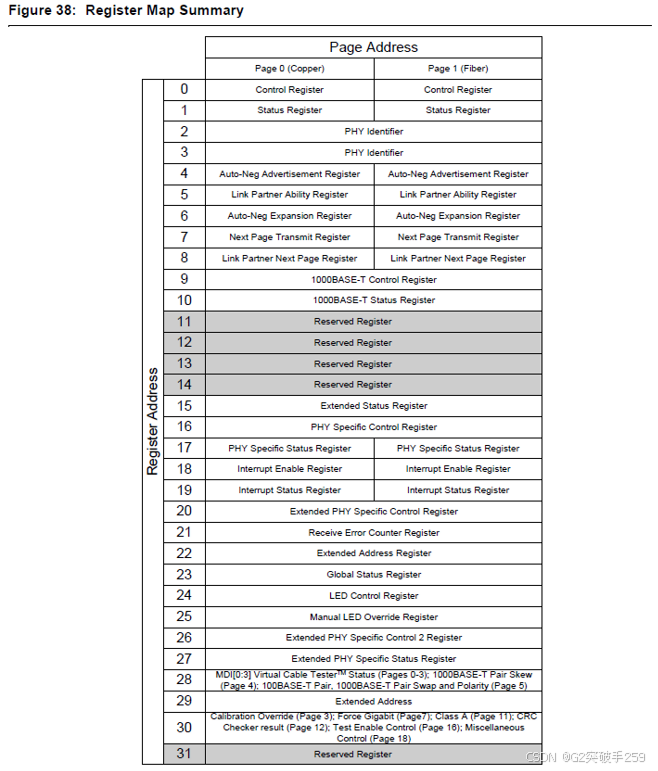

寄存器描述

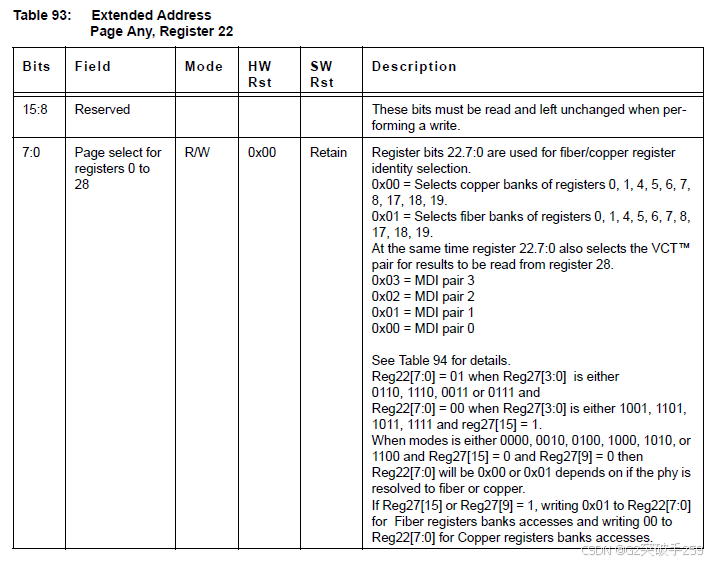

IEEE 为 PHY 只定义了 32 个寄存器地址空间,为了扩展可用的寄存器地址空间的数量,使用了分页机制。对于寄存器地址 0 ~ 21 和 23 ~ 28,用寄存器地址 22[7:0] 来指定页面。对于寄存器 30 和 31,寄存器地址 29[5:0] 用于指定页面。寄存器地址 22 和 29 没有分页。在本文档中,用于指定寄存器的简写形式为 register_page.bit:bit,register_page.bit,register.bit:bit,register.bit。

例如:

Register 0 page 1 bits 5 to 2 is specified as 0_1.5:2.

Register 0 page 1 bits 5 is specified as 0_1.5.

Register 2 bit 3 to 0 is specified as 2.3:0.

注意,在这种情况下,页面寄存器(寄存器 22)的设置不起作用。Register 2 bit 3 is specified as 2.3.

请注意,为了使分页机制正常工作,必须将寄存器 22.15 设置为 0 以禁用自动介质寄存器选择。

寄存器列表如下图所示:

寄存器具体表述请查看 88E1111 手册。

寄存器软件配置流程

-

写 R22 Extended Address 寄存器

根据上表可知,寄存器地址空间使用了分页机制,Page 0 为 Copper 模式,Page 1 为 Fiber 模式。通过配置 R22 Extended Address 寄存器可以配置 Page 0 或者 Page 0,用以切换不同的模式。

本文使用的是 Copper 模式。配置 R22 寄存器为 0x00,由于硬件复位后默认配置为 0x000,使用 Copper 模式时,此寄存器也可以忽略不配置。 -

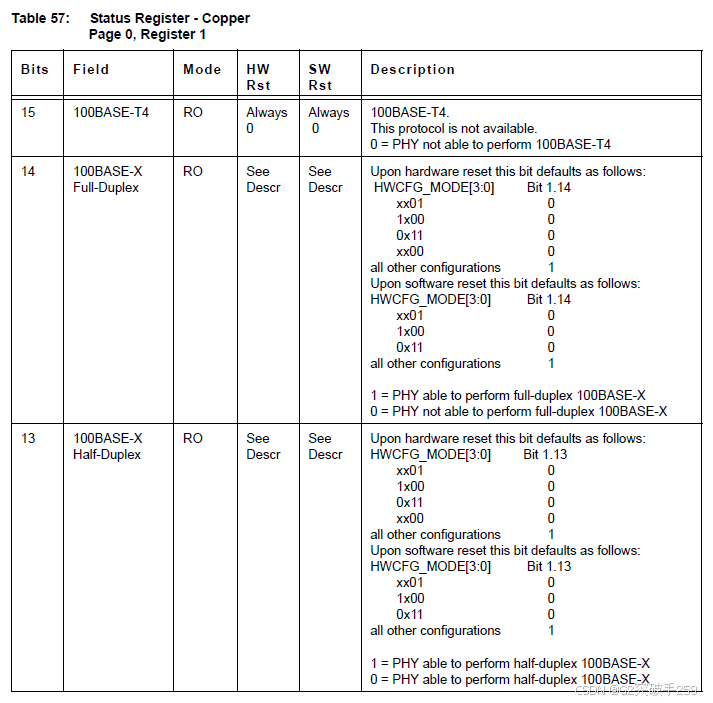

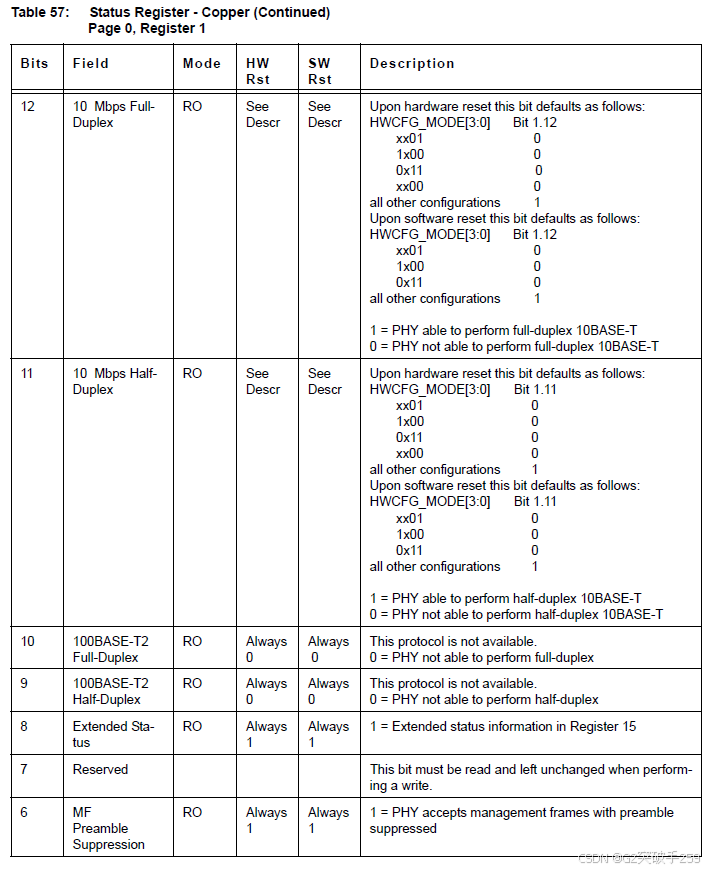

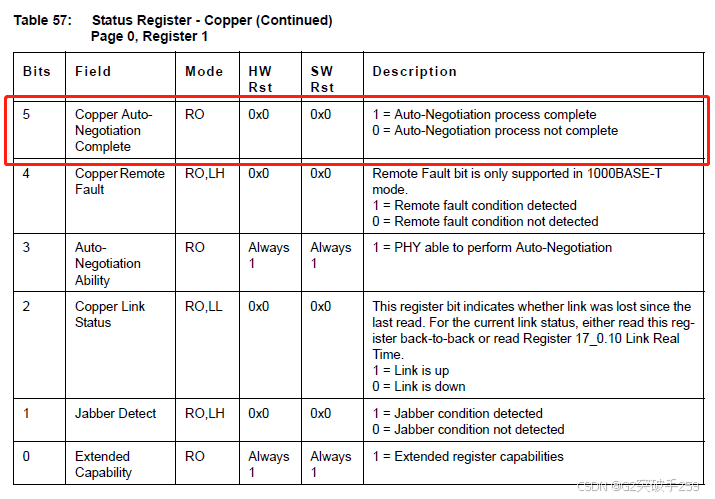

读 R1 Status Register 寄存器

通过查看 R1 Status Register 寄存器可以了解许多情况,有一个小技巧是,在读取 R17 PHY Specific Status Register 寄存器之前,可以先读一下 R1 Status Register 的 bit5,来确定 PHY 是否自协商完成。

-

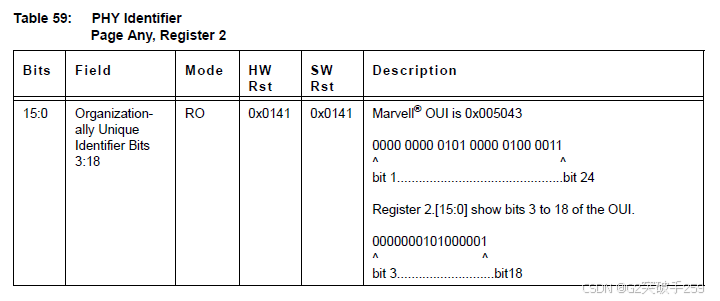

读 R2 PHY Identifier 寄存器

通过查看 R2 PHY Identifier 寄存器,可以获取到 PHY 的设备 ID,由下图可以看到,PHY 的 ID 是 0x0141,通过读取设备 ID 可以判断设备类型,以及 PHY 设备是否能正常访问。

-

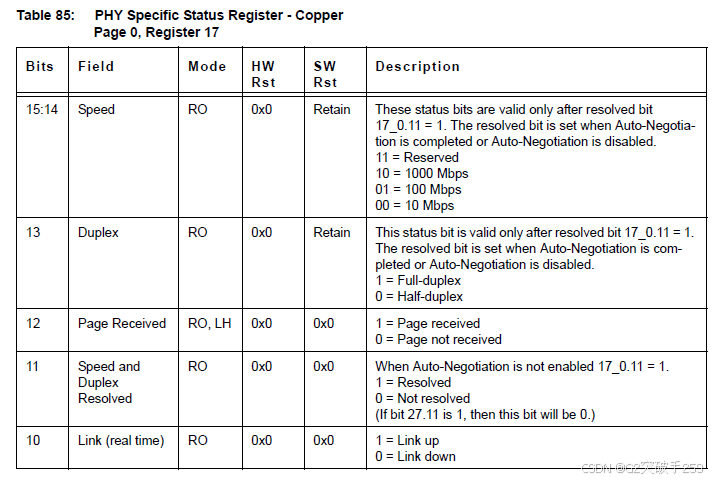

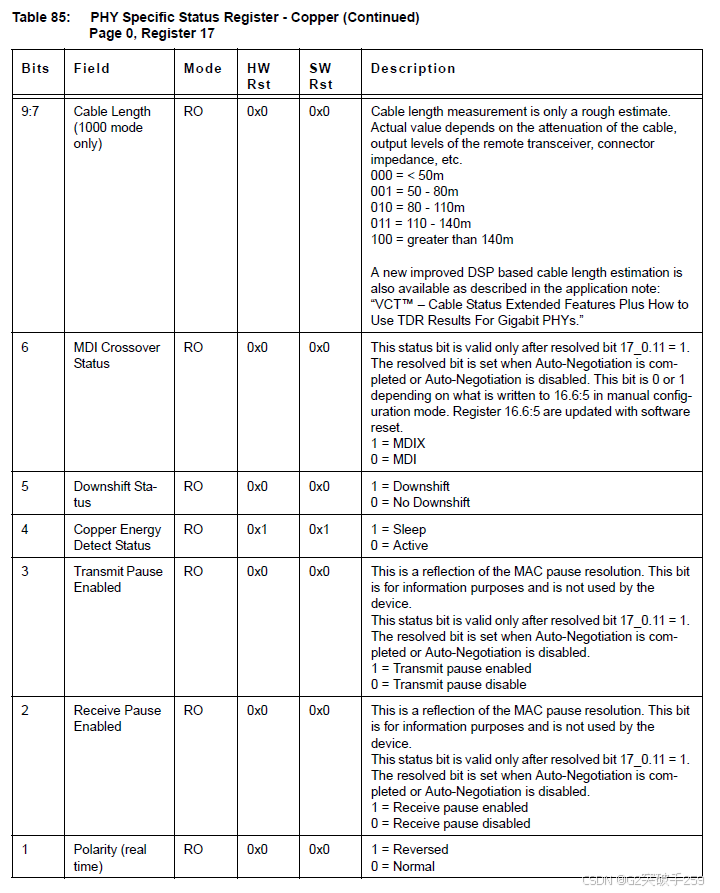

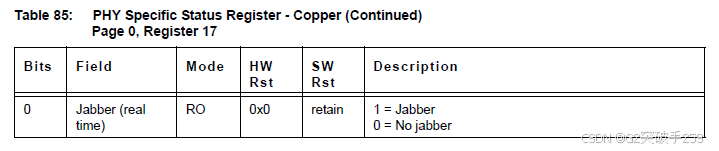

读 R17 PHY Specific Status Register 寄存器

通过查看 PHY 的 R17 PHY Specific Status Register 寄存器可以查看 PHY 的 Link 状态,速率,双工模式等状态。

-

读 R27 Extended PHY Specific Status Register 寄存器

先读 PHY 的 R27 Extended PHY Specific Status Register 寄存器的默认配置,然后再去写寄存器的 bit[3:0]。

-

写 R27 Extended PHY Specific Status Register 寄存器

通过修改 PHY 的 R27 Extended PHY Specific Status Register 寄存器的 bit[3:0],可以配置 PHY 的模式,等同于硬件上修改 HWCFG_MODE[3:0] ,可以配置 GMII,RGMII,SGMII 等模式。

GMII 模式,配置 R27 寄存器为 0xXXXF。

RGMII 模式,配置 R27 寄存器为 0xXXXD。

SGMII 模式,配置 R27 寄存器为 0xXXX4。 -

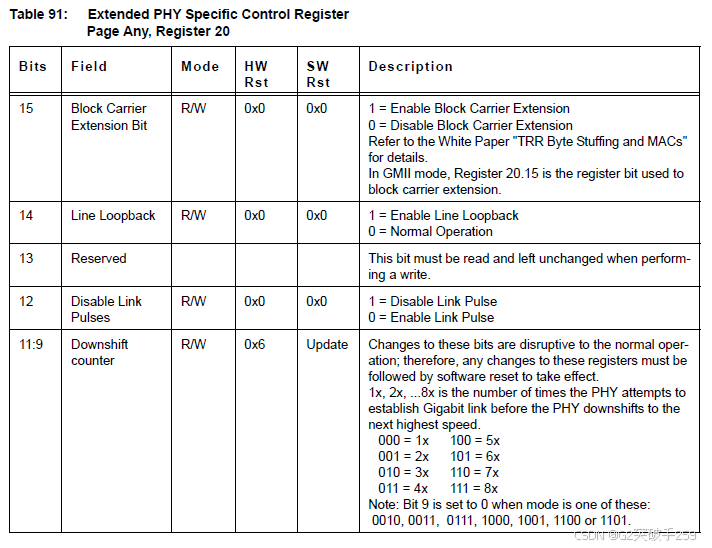

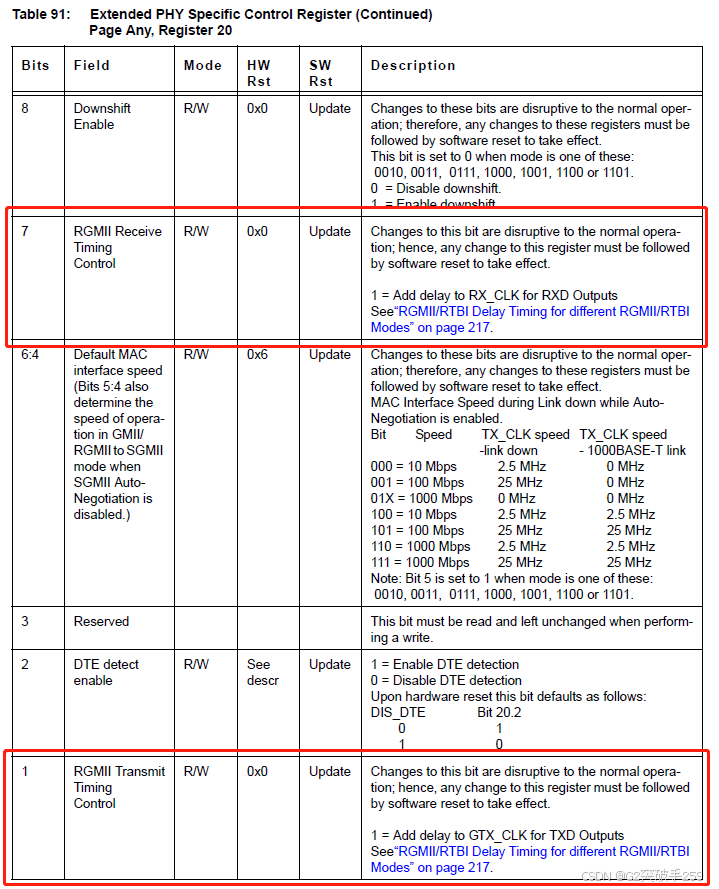

读 R20 Extended PHY Specific Control Register 寄存器

先读 PHY 的 R20 Extended PHY Specific Control Register 寄存器的默认配置,然后再去写寄存器的 bit7 和 bit1。

-

写 R20 Extended PHY Specific Control Register 寄存器

RGMII 模式下,Intel 建议将外部 PHY 的 TX 和 RX 延迟特性开启(90 度偏移),所以要将 Register 20.1 和 20.7 置 1。默认值为 0,需要软件配置!!GMII 模式和 SGMII 模式保持默认值 0。 -

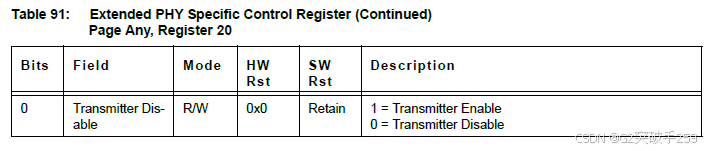

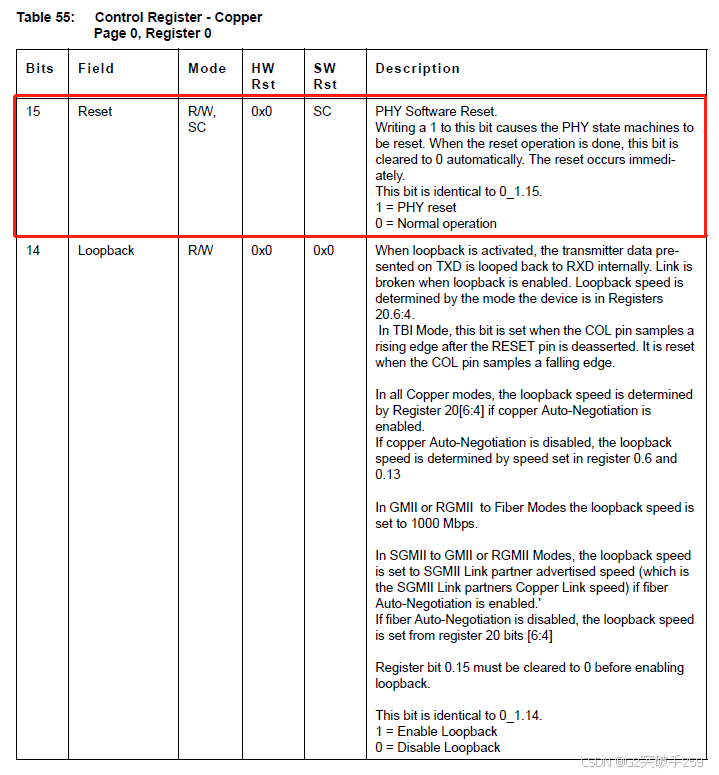

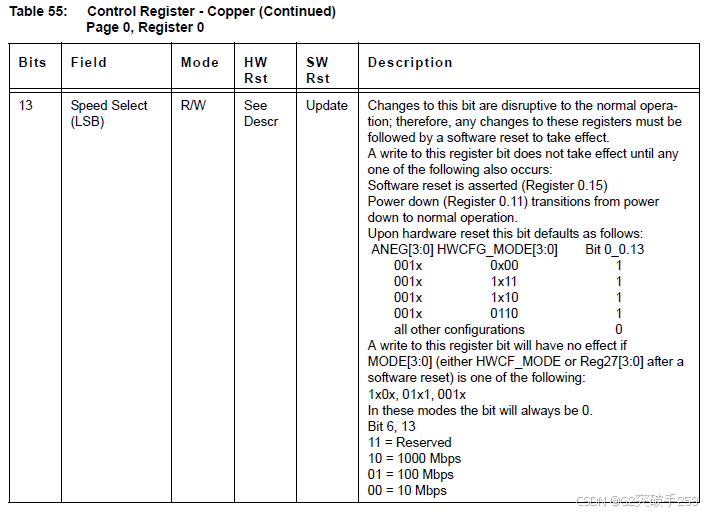

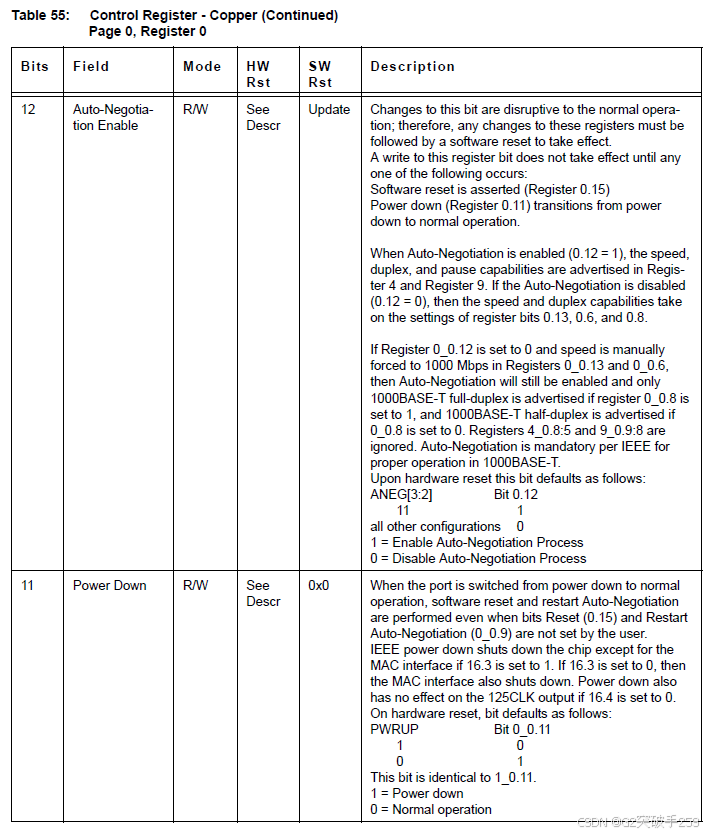

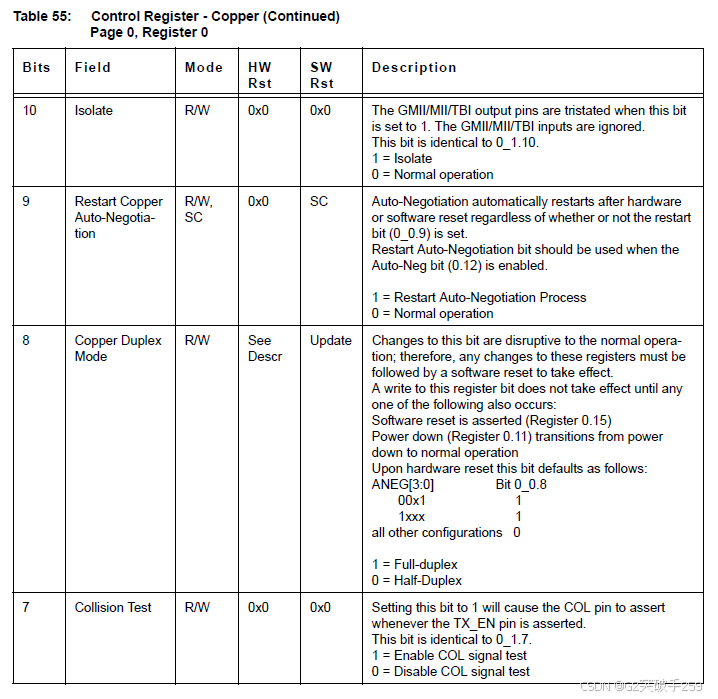

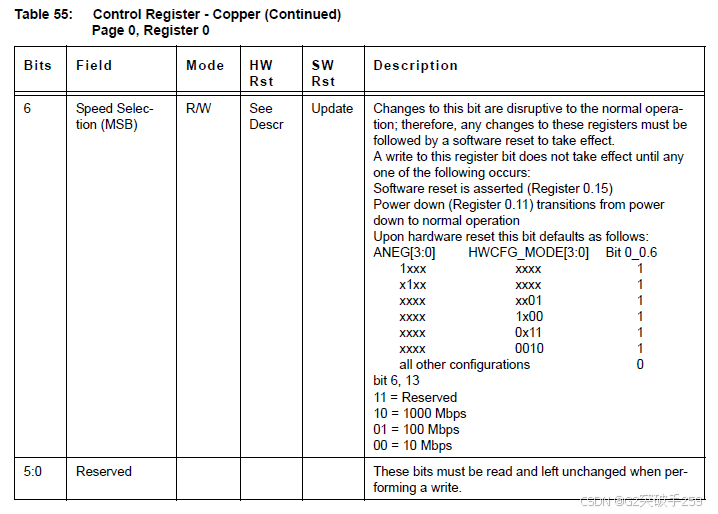

读 R0 Control Register 寄存器

先读 PHY 的 R0 Control Register 寄存器的默认配置,然后再去写寄存器的 bit15。

-

写 R0 Control Register 寄存器

对 PHY 寄存器进行配置以后,并不会立刻生效,需要对 PHY 进行软复位操作以后才能够生效。通过配置 R0 Control Register 寄存器可以配置自协商,双工等,同时也可以对 PHY 进行软复位操作。将 Register 0.15 置 1,当复位操作完成后,该位自动清除为0。重置立即发生。 -

读 R0 Control Register 寄存器

回读寄存器确认软复位生效。 -

读 R27 Extended PHY Specific Status Register 寄存器

回读寄存器确认配置生效。 -

读 R20 Extended PHY Specific Control Register 寄存器

回读寄存器确认配置生效。

注意事项:

- 88E1111 在上电以后,需要进行硬件复位操作,这样配置的参数才能得以启动。当开发人员操作软件寄存器对 PHY 进行二次配置,也需要去配置 R0 Control Register 寄存器去软复位一下 PHY 芯片,这样才能使寄存器的配置生效。

- Marvell 88E1111 最小的硬件复位时间为 10ms,某些国产替代料建议硬件复位时间不低于 100ms。

- Marvell 88E1111 的 MDC 最大时钟频率可以到 8.3MHz,某些国产替代料的 MDC 时钟频率建议不要超过 2.5MHz,否则会出现读写不正常的问题。

通过 Quartus 平台三速以太网 IP 对 PHY 芯片进行软件配置

在平台三速以太网 IP MAC Options 配置界面,勾选 Include MDIO module (MDC/MDIO) 选项,因为外部接入的 MAC 控制接口时钟频率为 125MHz,所以分频系数设置为 50,MDC 时钟频率为 125Mhz/50 = 2.5 MHz。

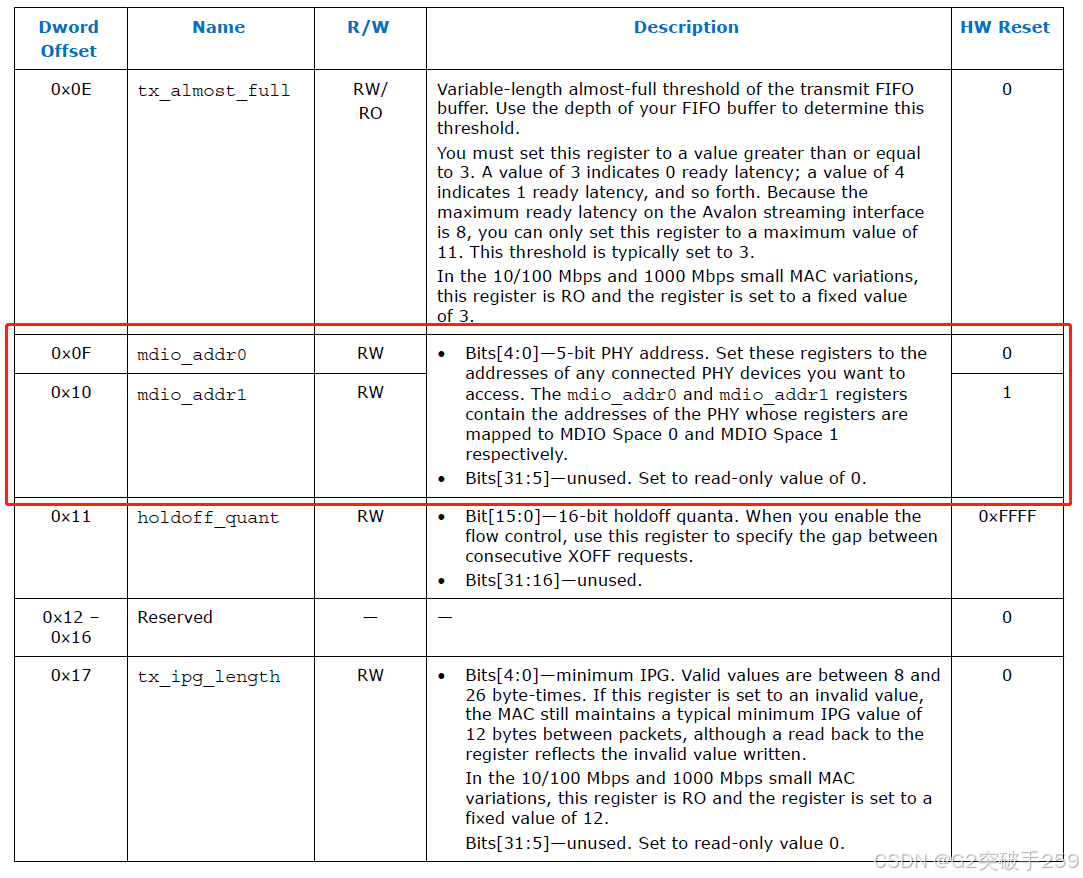

MDIO 地址寄存器

Bits[4:0] - 5 位 PHY 地址。将这些寄存器设置为您想要访问的任何连接的 PHY 设备的地址。mdio addr0 和 mdio addr1 寄存器包含 PHY 的地址,它们的寄存器分别映射到 mdio Space 0 和 mdio Space 1。由上文可知,PHY 设备的地址由硬件 CONFIG 管脚对 PHY 芯片进行配置。本文配置的 PHYADR[4:0] 值为 0x7。

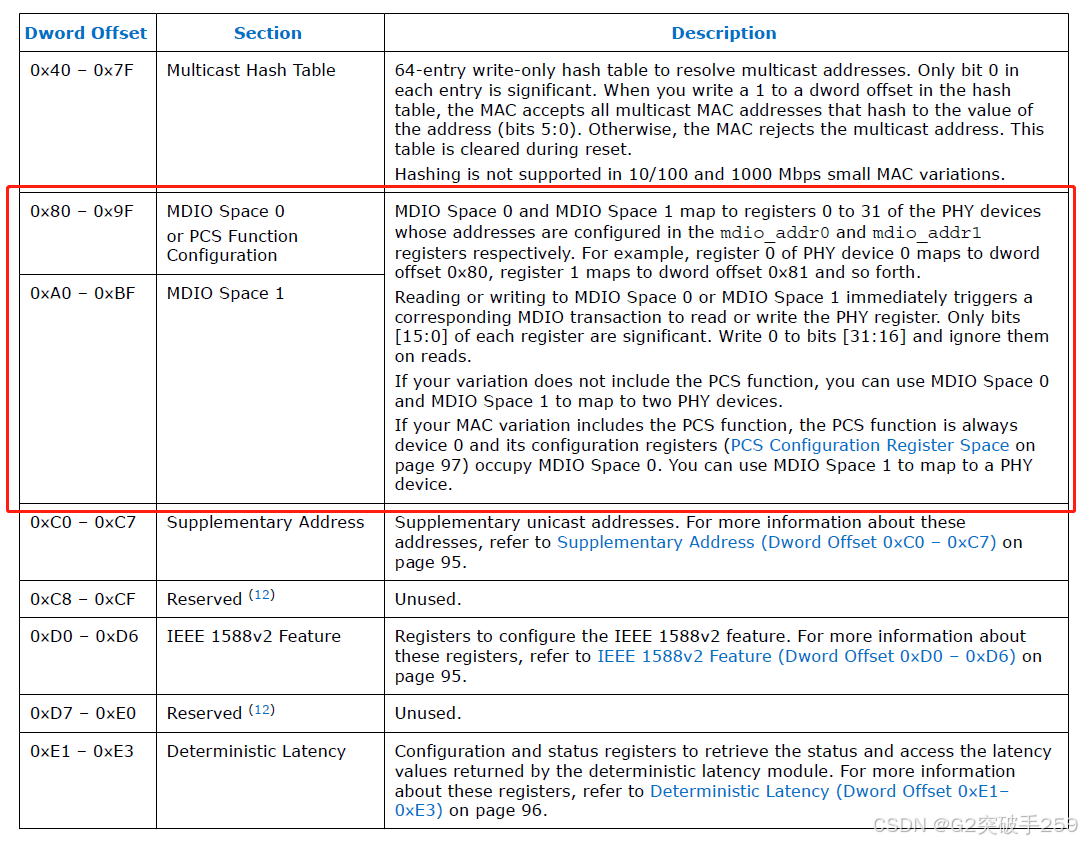

MDIO 空间寄存器

MDIO Space 0 和 MDIO Space 1 分别对应于 mdio_addr0 和 mdio_addr1 寄存器中配置地址的 PHY 设备的寄存器 0 ~ 31。例如,PHY 设备 0 的寄存器 0 映射到地址偏移量 0x80,寄存器 1 映射到地址偏移量 0x81,以此类推。

读取或写入 MDIO Space 0 和 MDIO Space 1 立即触发相应的 MDIO 事务来读取或写入 PHY 寄存器。每个寄存器中只有 bits[15:0] 是有效的。

如果你的 MAC 配置不包括 PCS 功能,你可以使用 MDIO Space 0 和 MDIO Space 1 来映射到两个 PHY 设备。

如果你的 MAC 配置包含 PCS 功能,则 PCS 功能始终是 device 0,其配置寄存器(第 97 页的 PCS 配置寄存器空间)占用 MDIO Space 0。您可以使用 MDIO Space 1 映射到外部 PHY 设备。

由于 SGMII 模式需要 MAC 配置包含 PCS 功能,所以统一使用 MDIO Space 1 来映射到外部 PHY 设备,以简化配置程序。

参考资料

https://www.intel.com/content/www/us/en/docs/programmable/683402/15-0/introduction.html

1762

1762

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?