FMC 简介

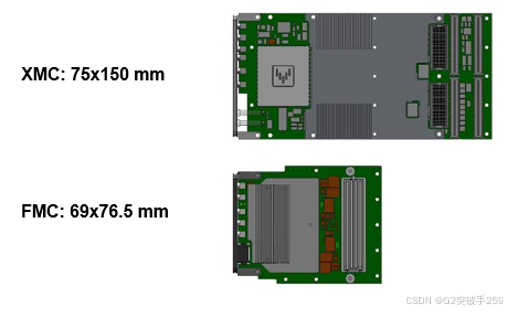

FPGA 对 I/O 需求的变化适应性很强。在重新配置 FPGA 以实现新协议之后,只需更换物理 I/O 组件和连接器即可。除非 I/O 组件在扩展卡模块,否则需要改变板级设计。为了避免与设计变更相关的成本和工作量,设计人员一直依赖于 PCI Mezzanine Card (PMC) 和 Switched Mezzanine Card (XMC) 标准。然而,这些标准是多年前为单板计算机(SBCs)等通用解决方案开发的,而不是 FPGA。2008 年 7 月,随着美国国家标准协会(ANSI)批准和发布 VITA 57 FPGA Mezzanine Card (FMC) 标准,这种情况发生了变化。

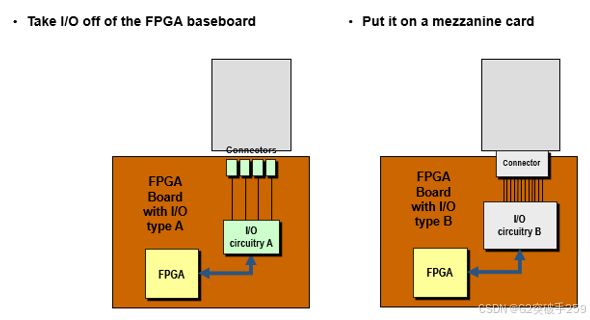

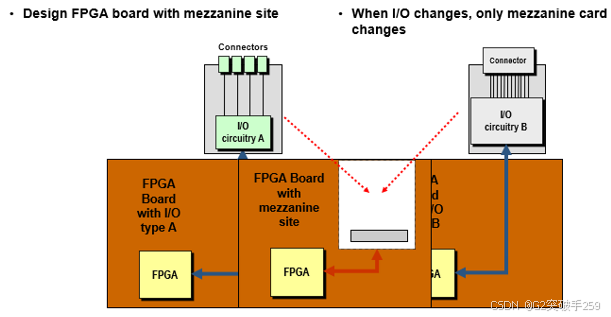

下图为普通板级设计和基于 FMC 扩展卡的设计的区别:

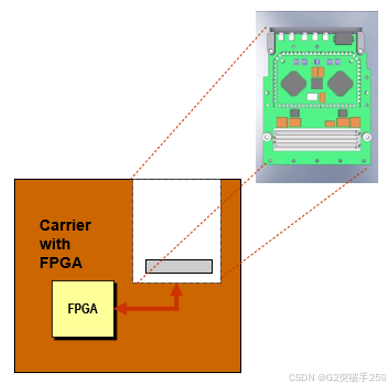

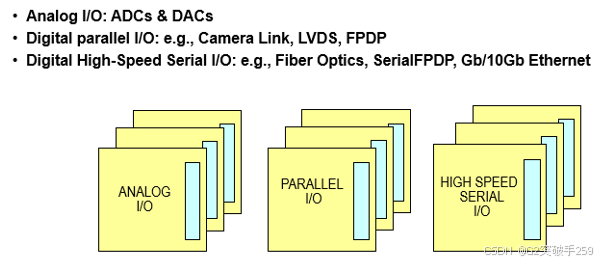

FMC 标准由从 FPGA 供应商到最终用户的公司联盟开发,旨在为位于基板(载卡)上的 FPGA 提供标准的扩展卡外形、连接器和模块化接口。以这种方式将 I/O 接口与 FPGA 解耦,简化了 I/O 接口模块设计,同时最大限度地提高了载卡的可重复使用能力。与使用 PCI、PCI-X、PCle 或 Serial RapidIO 等复杂接口的 PMC 和 XMC 标准不同,FMC 标准只需要直接连接到载卡上的 FPGA 的核心 I/O 和收发器电路。复杂接口标准在 FMC 扩展卡上实现。如下图所示,FMC 扩展卡可以支持以下接口标准:

- 模拟 I/O:ADC 和 DAC

- 数字并行 I/O:例如,Camera Link,LVDS,FPDP

- 数字高速串行 I/O:例如,光纤,串行 FPDP,Gb/10Gb 以太网

FMC 标准为电路板开发人员提供稳定,直接和兼容的标准。FMC 标准的优点如下:

- 减少对扩展卡上复杂协议逻辑的需求

- 最大限度地提高数据吞吐量

- 最大限度地降低延迟

- 降低 FPGA 设计复杂性

- 最大限度地减少系统开销

- 比 PMCI、XMC 扩展卡具有更好的散热性能

FMC 标准定义了单宽度(69mm x 76.5mm)和双宽度(139mm x 76.5mm)的外形标准。单宽度模块支持单个连接器连接到载卡。双宽度模块专为需要额外带宽、更多前面板空间或更大 PCB 面积的应用而设计,最多支持两个连接器。FMC 标准的两个外观标准提供了额外的灵活性,可以根据空间、I/O 需求优化电路板。

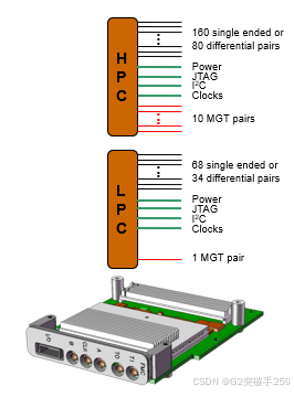

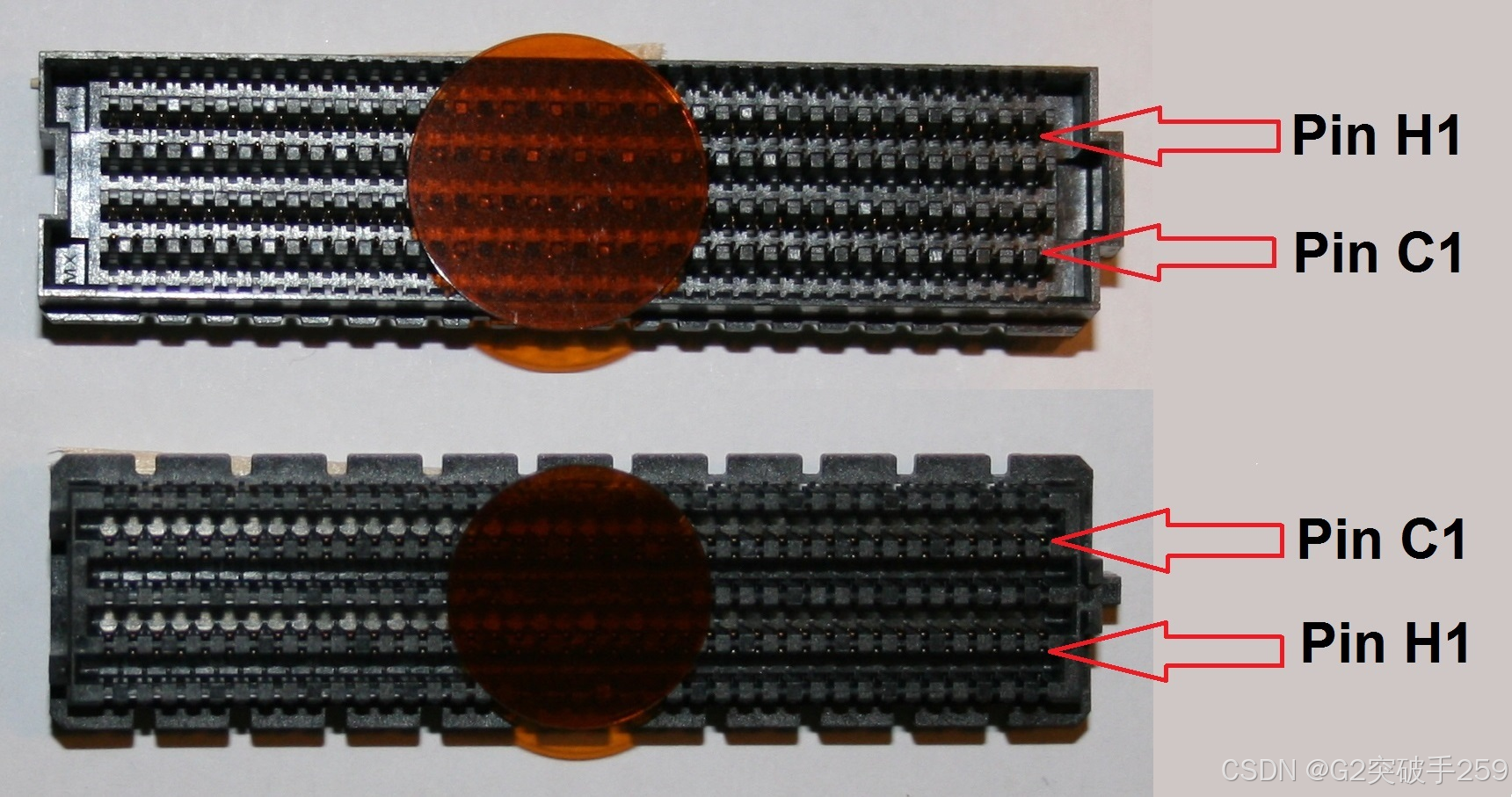

一旦选定了外形尺寸,电路板开发人员就可以从两种不同的连接器中进行选择,作为从 FMC 标准到载卡上 FPGA 的接口:具有 160 引脚的低引脚数(LPC)连接器和具有 400 引脚的高引脚数(HPC)连接器。两者都支持高达 2 Gb/s 的单端和差分信号,以及高达 10 Gb/s 的 FPGA 串行收发器信号。LPC 连接器提供 68 个用户定义的单端信号(或 34 个用户定义的差分信号)。它还提供了 1 对串行收发器信号、时钟、一个 JTAG 接口和一个 I2C 接口,作为对基本智能平台管理接口(IPMI)命令的可选支持。HPC 连接器提供 160 个用户定义的单端信号(或 80 个用户定义的差分信号),10 对串行收发器信号和额外的时钟。

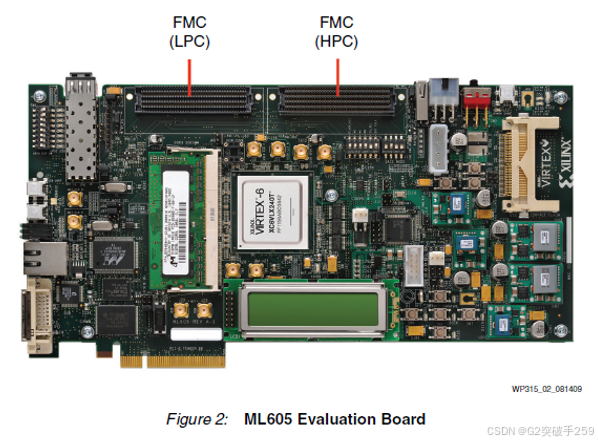

HPC 和 LPC 连接器使用相同的机械结构。唯一的区别是哪些信号是实际上被使用的。因此,具有LPC 连接器的扩展卡可以插入到 HPC 端子,并且如果设计得当,当插入到 LPC 端子时,具有 HPC 连接器的扩展卡可以提供功能的子集。下图显示了 Xilinx 的一个开发板,它具有 Virtex®-6 FPGA 和两个 FMC 连接器(一个 LPC 和一个 HPC)。

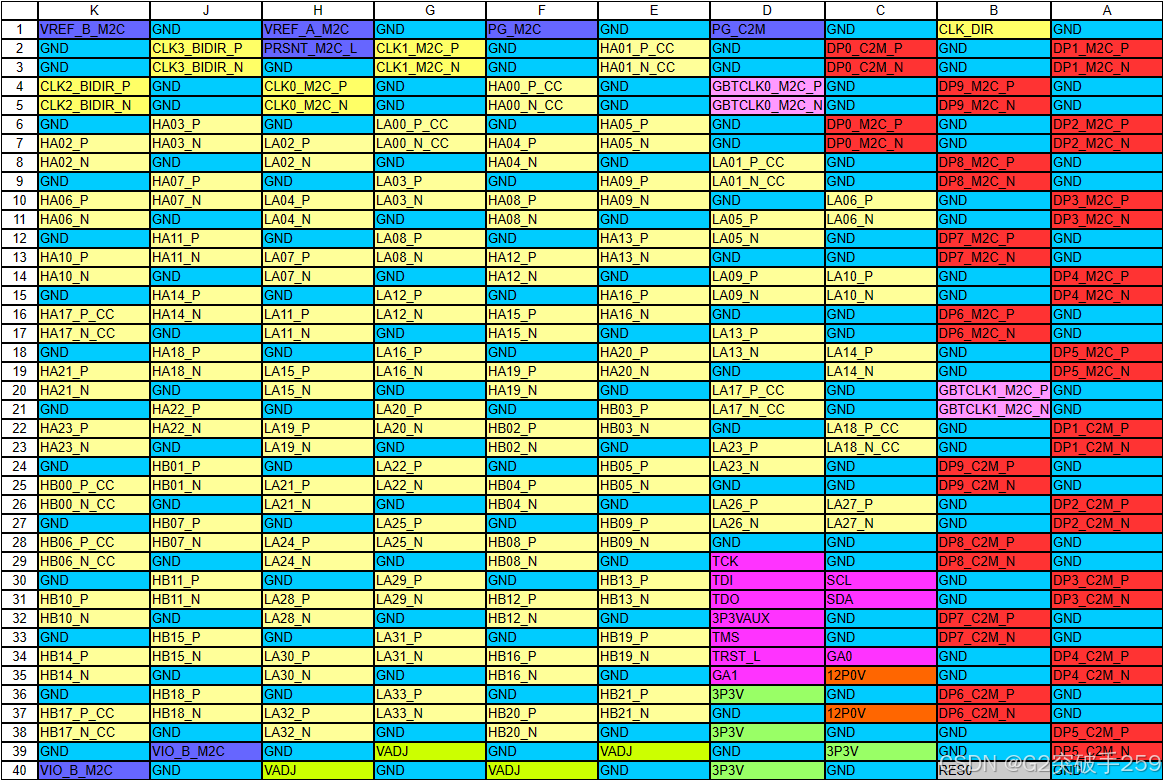

FMC 引脚输出定义

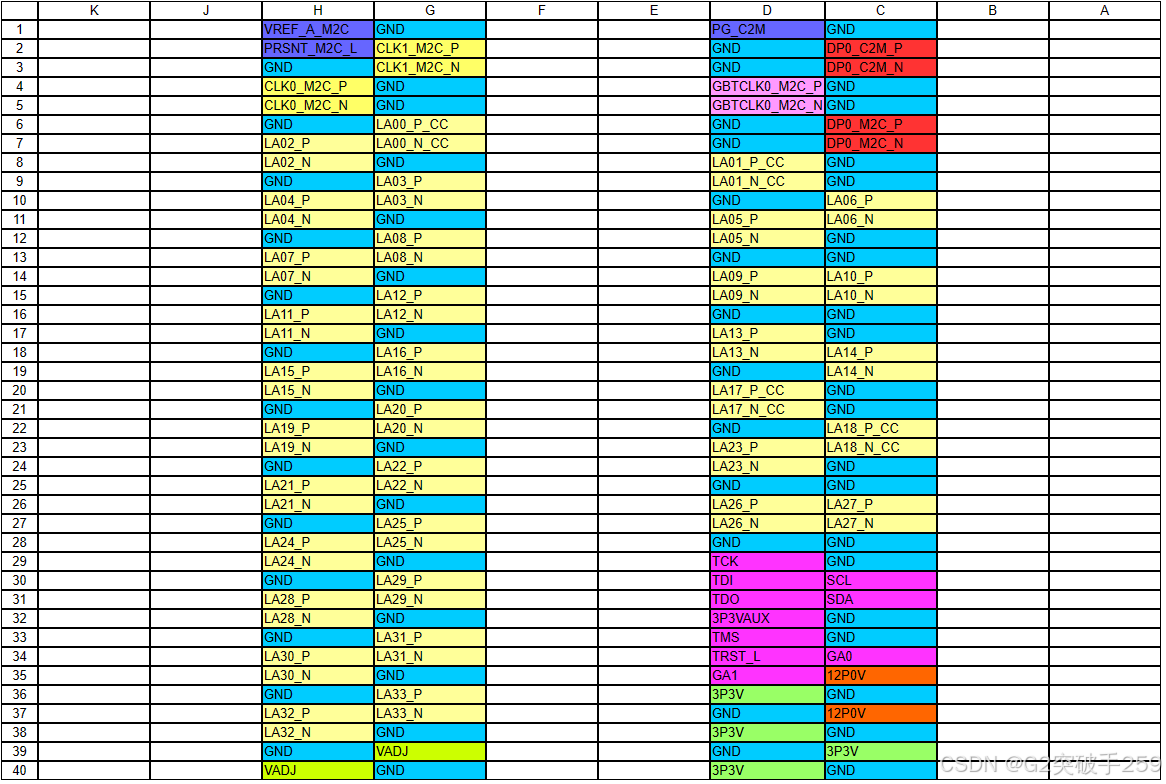

High-pin count (HPC) connector, HPC pinout

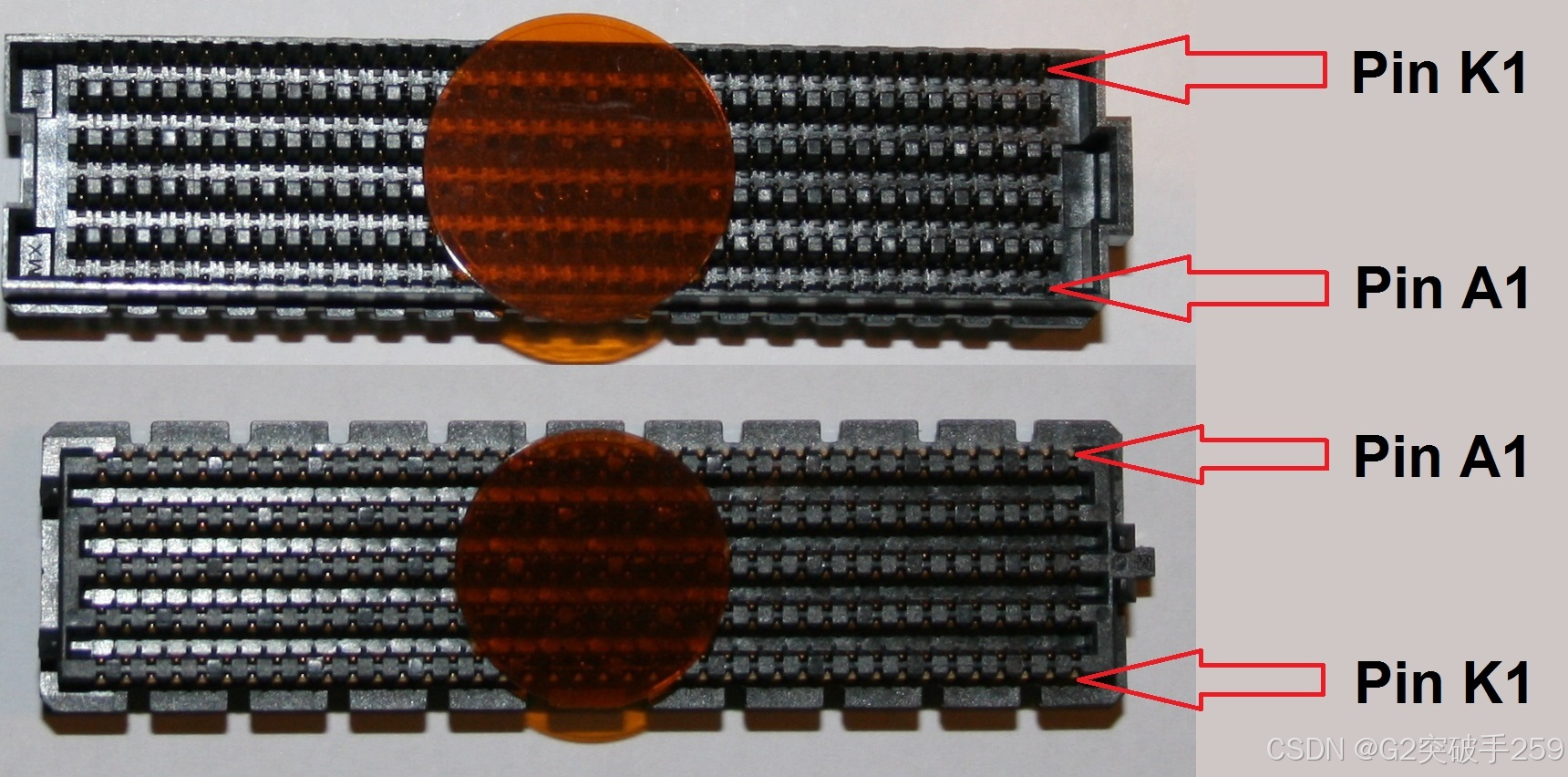

HPC 连接器有 10 排(A、B、C、D、E、F、G、H、J、K),每排 40Pin。下表总结了 HPC 连接器的引脚。

HPC connector pin summary

| General pin function | Pin count |

|---|---|

| Gigabit data | 40 |

| Gigabit clocks | 4 |

| User data | 160 |

| User clocks | 8 |

| I2C | 2 |

| JTAG | 5 |

| State flags | 5 |

| Power supply | 15 |

| Ground | 159 |

| Reserved | 2 |

Footprints can be viewed in Lib_Altium repository.

Low-pin count (LPC) connector, LPC pinout

LPC 连接器有 4 排(C, D, G, H),每排 40Pin。下表总结了 LPC 连接器的引脚。

LPC connector pin summary

| General pin function | Pin count |

|---|---|

| Gigabit data | 4 |

| Gigabit clocks | 2 |

| User data | 68 |

| User clocks | 4 |

| I2C | 2 |

| JTAG | 5 |

| State flags | 4 |

| Power supply | 10 |

| Ground | 61 |

Footprints can be viewed in Lib_Altium repository.

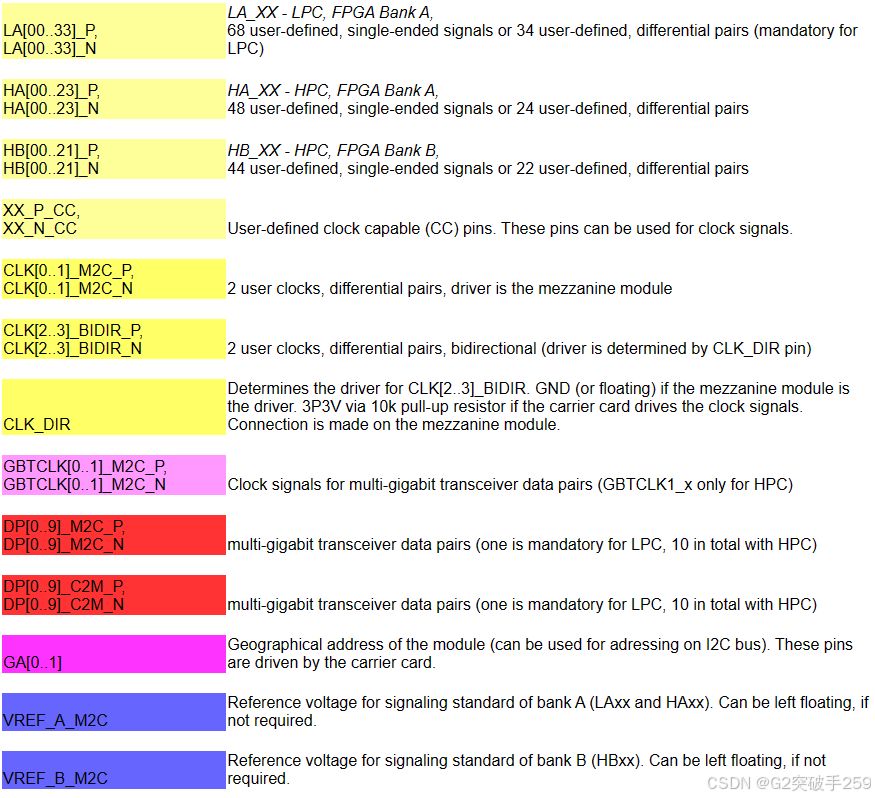

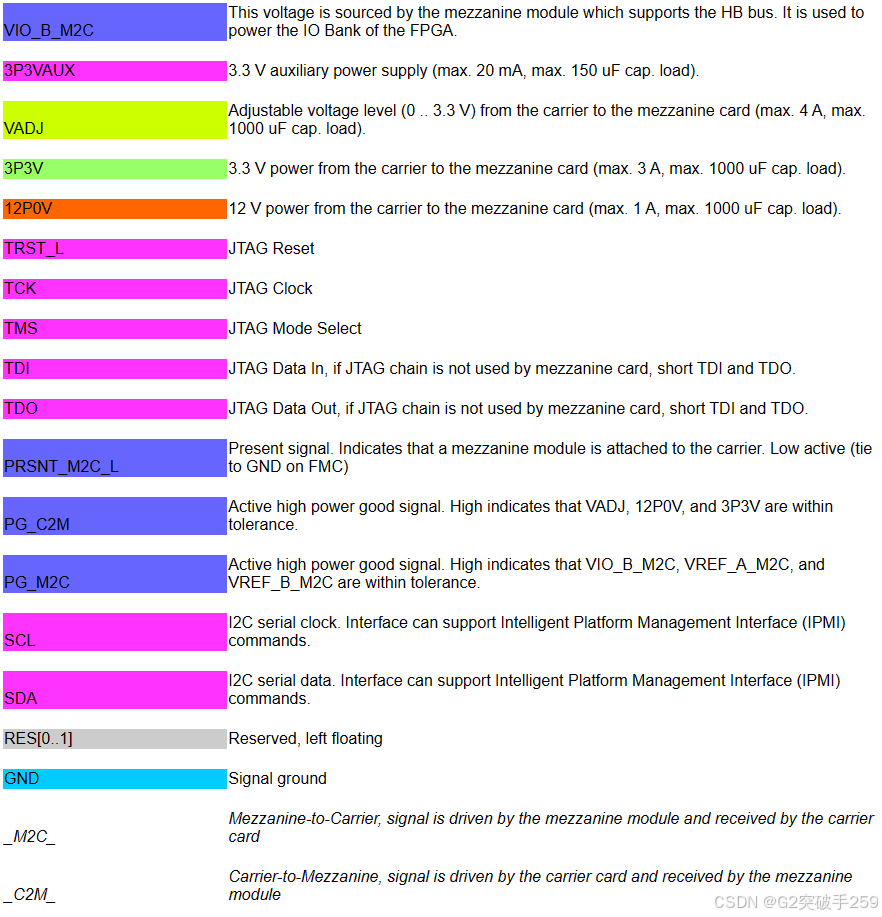

Pin and signal description

FMC+ 简介

FMC+ 是 FMC 的增强功能。它将 FPGA 串行收发器信号从 10 对增加到 32 对,数据速率高达 28Gbps。FMC+ 载卡允许向后兼容 FMC 扩展卡。FMC 要求由 ANSI/VITA 57.1 标准定义。FMC+ 要求由 ANSI/VITA57.4 标准定义。

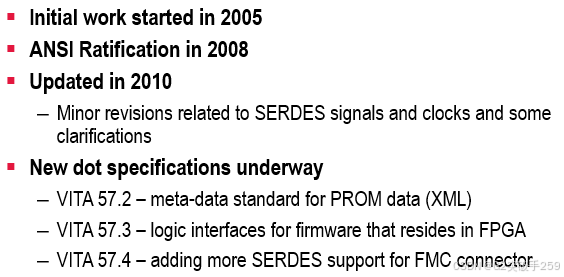

VITA57 标准更新历史

VITA57.4 标准推出的原因

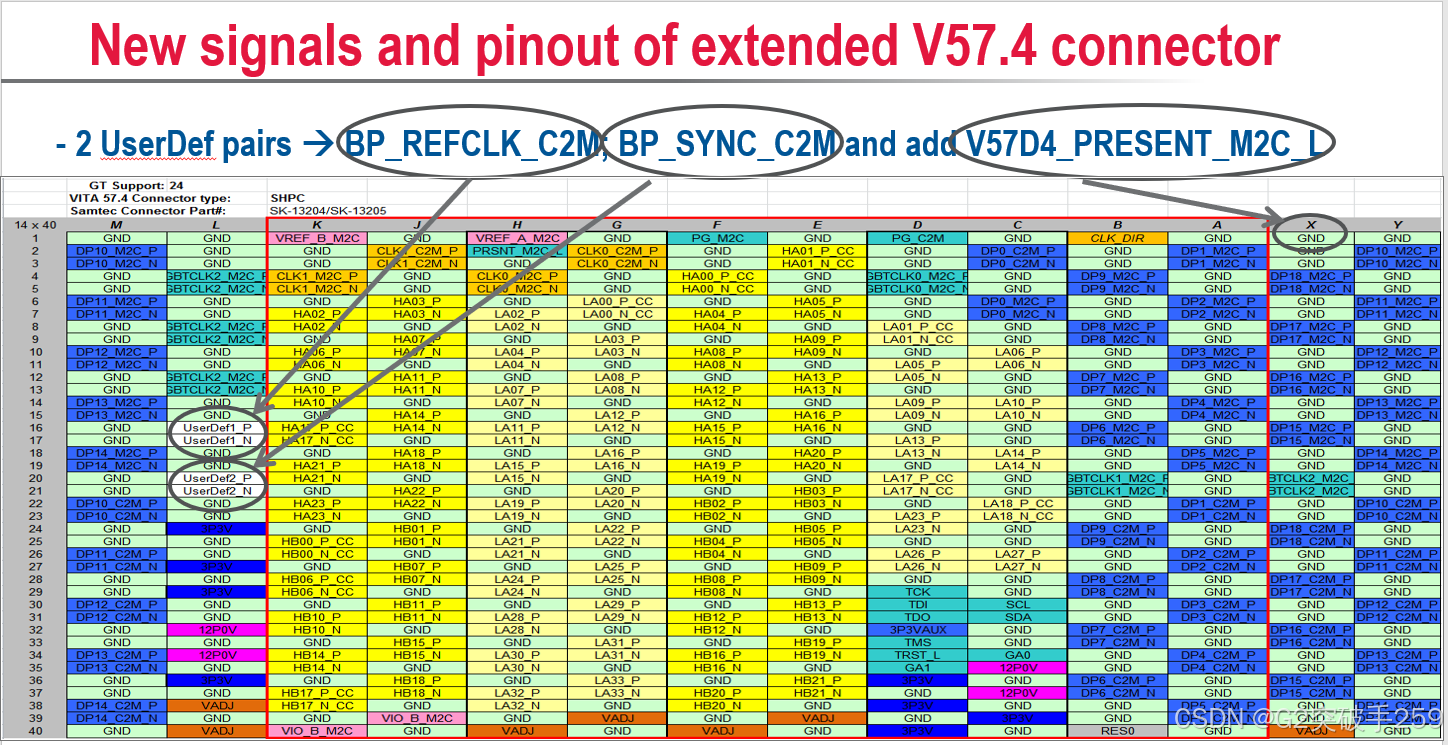

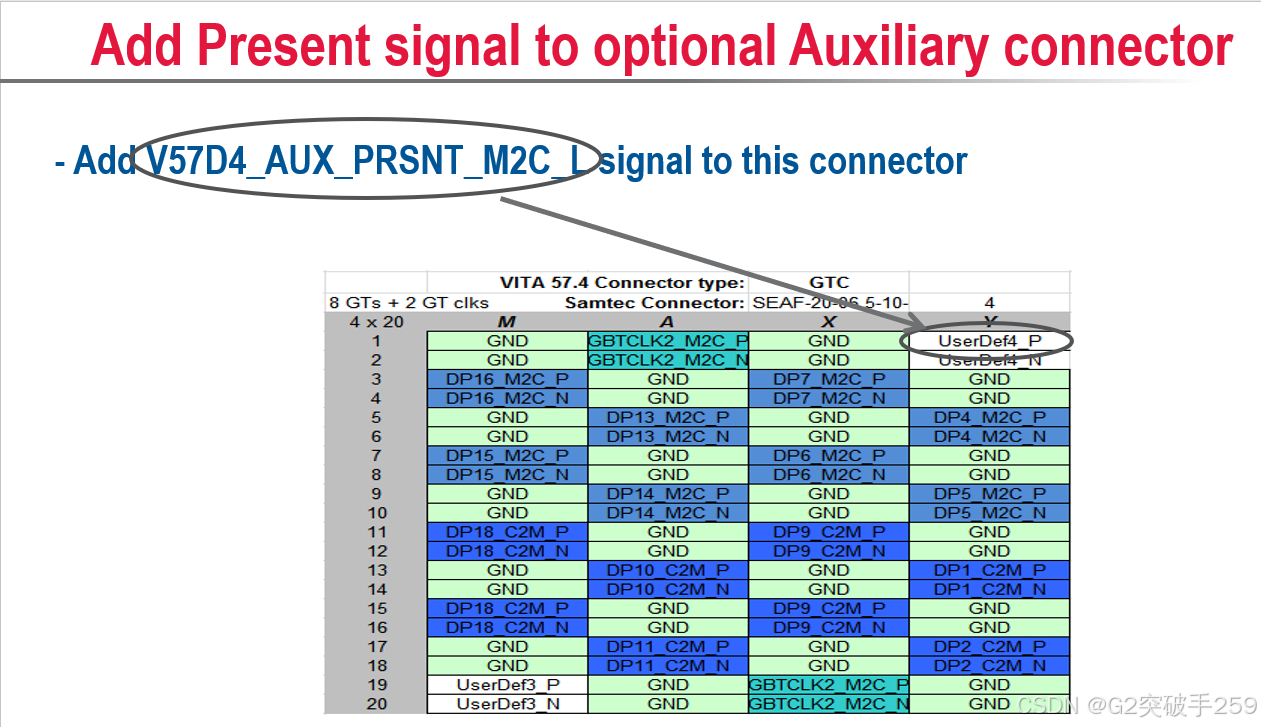

FMC+ 引脚输出定义

Altera 开发板的 FMC 引脚定义

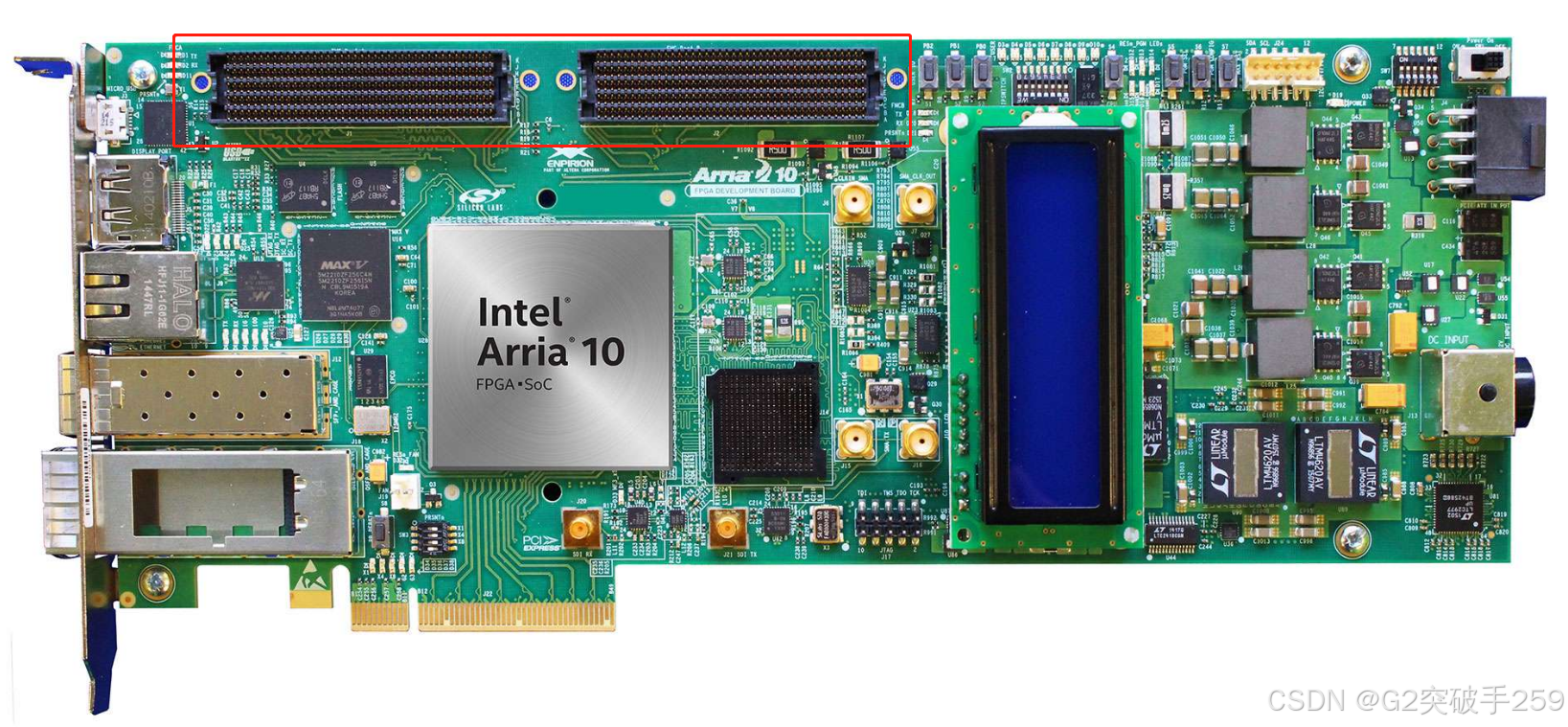

英特尔® Arria® 10 GX FPGA 开发套件

订购代号:DK-DEV-10AX115S-A

https://www.intel.cn/content/www/cn/zh/products/details/fpga/development-kits/arria/10-gx.html

Xilinx 开发板的 FMC 引脚定义

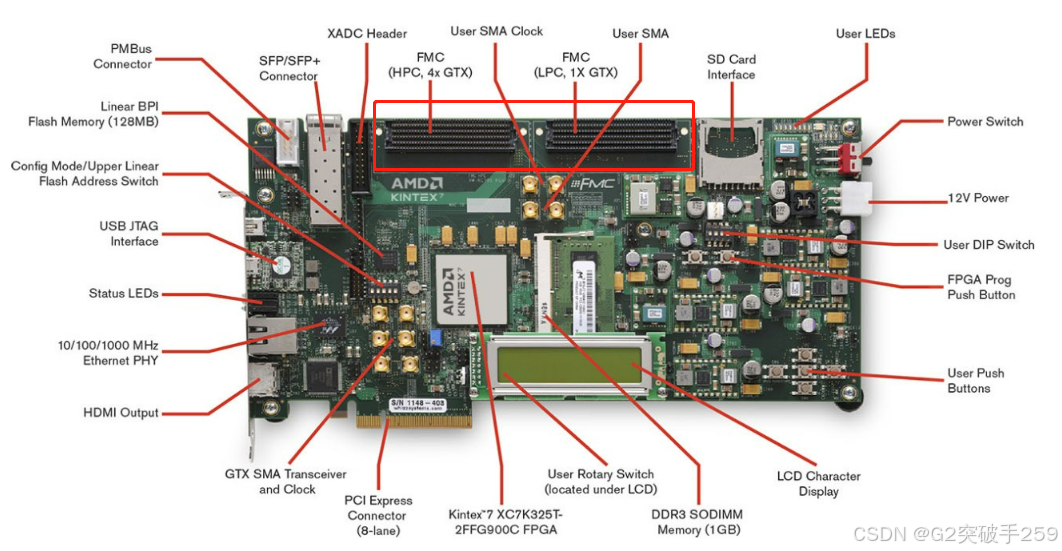

AMD Kintex 7 FPGA KC705 评估套件

https://china.xilinx.com/content/xilinx/zh/products/boards-and-kits/ek-k7-kc705-g.html

主板原理图(需注册 AMD 账号才可下载):

https://china.xilinx.com/member/forms/download/design-license.html?cid=188020&filename=kc705_Schematic_xtp132_rev1_1.pdf

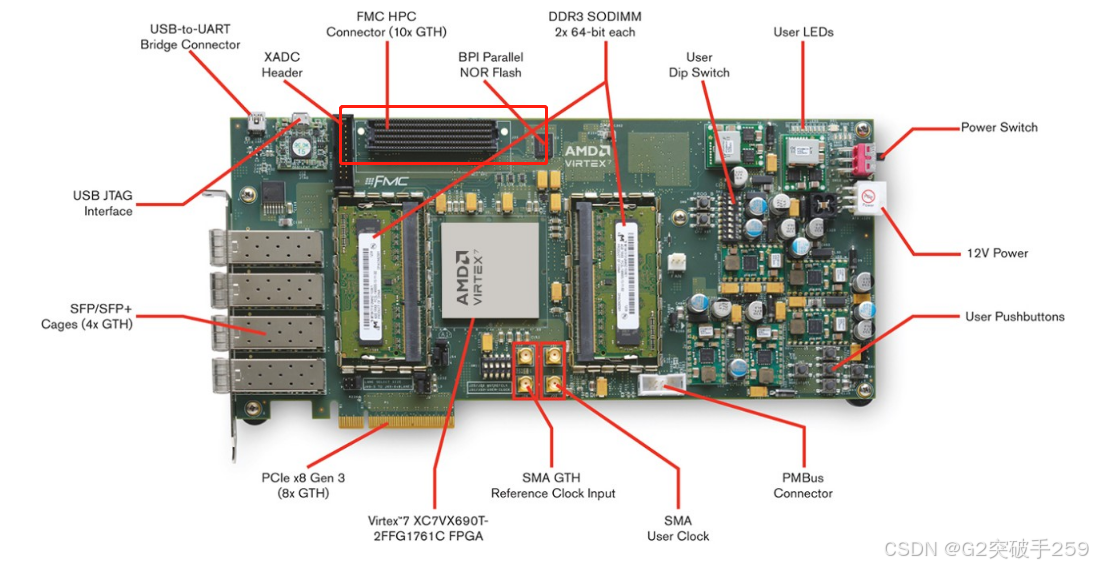

AMD Virtex 7 FPGA VC709 连接功能套件

https://china.xilinx.com/products/boards-and-kits/dk-v7-vc709-g.html

主板原理图(需注册 AMD 账号才可下载):

https://china.xilinx.com/member/forms/download/design-license.html?cid=201032&filename=vc709_Schematic_xtp213_rev1_0.pdf

ALINX 开发板

Xilinx Kintex UltraScale FMC HPC PCIE 光纤 FPGA 开发板 XCKU040 AXKU041

主板原理图:

https://www.alinx.com/public/upload/file/AXKU041_UG.pdf

参考资料:

- https://fmchub.github.io/appendix/VITA57_FMC_HPC_LPC_SIGNALS_AND_PINOUT.html

- ANSI/VITA 57.1-2008

- Overview of VITA57 – FMC, Curtiss Wright, www.vita.com/Resources/Learn/FMC%20Overview.pptx

- I/O Design Flexibility with the FPGA Mezzanine Card (FMC), Xilinx WP315

- FMCHUB - FPGA MEZZANINE CARDs

- Lib_Altium, Altium Designer libraries for ANSI/VITA 57 FPGA Mezzanine Card (FMC) Standard

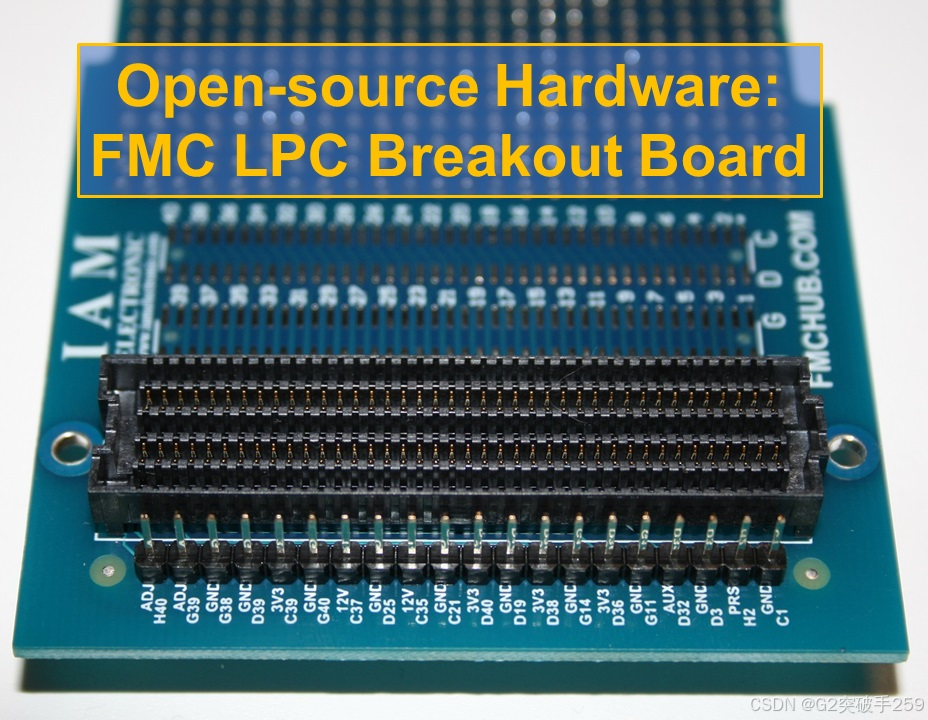

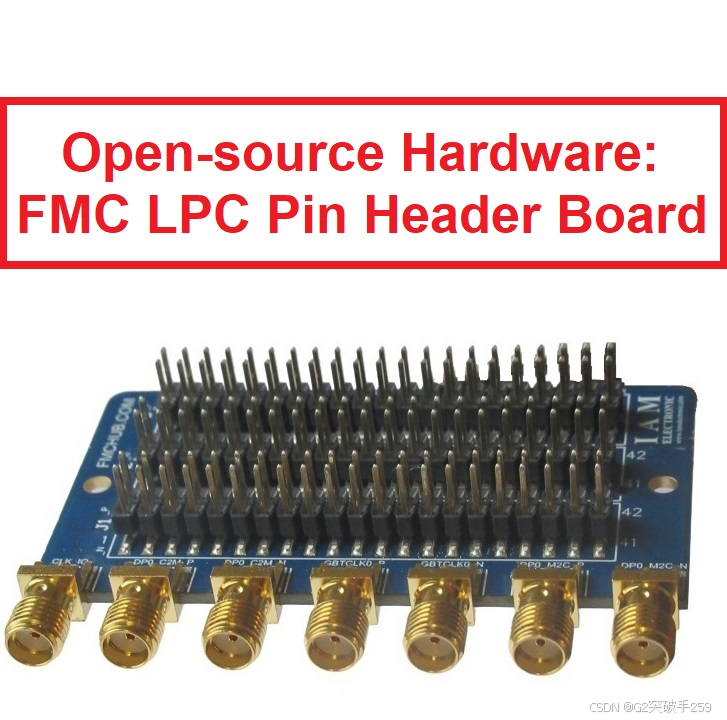

- FMC LPC Breakout board, Datasheet of Open-source hardware FMC module

2322

2322

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?