文章目录

LVDS 简介

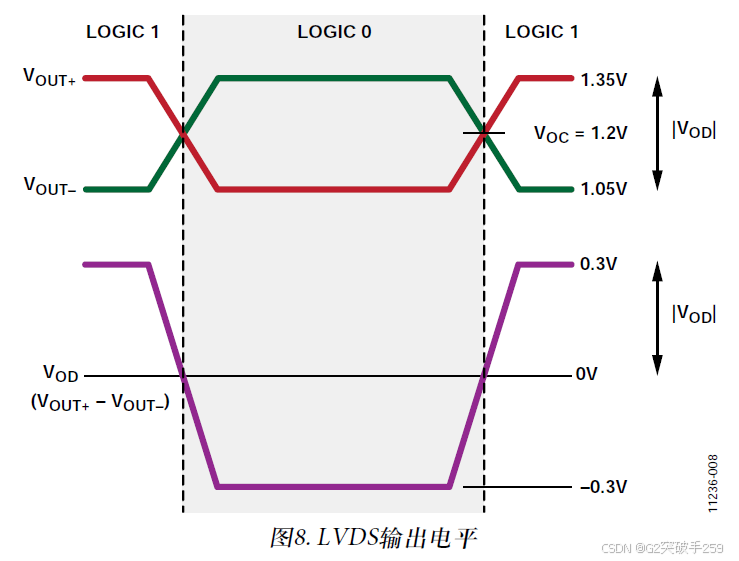

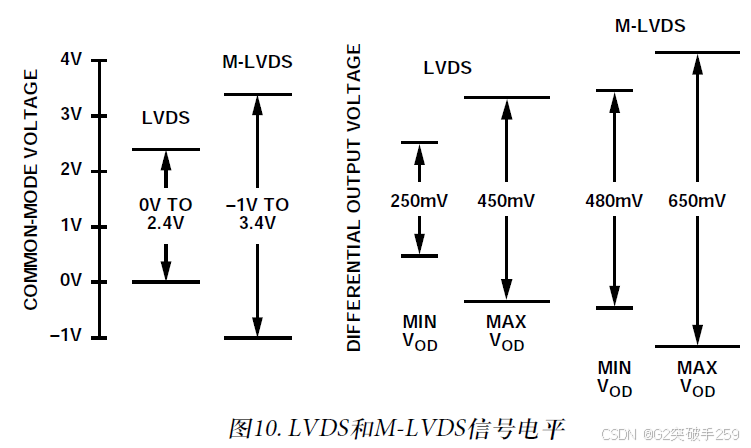

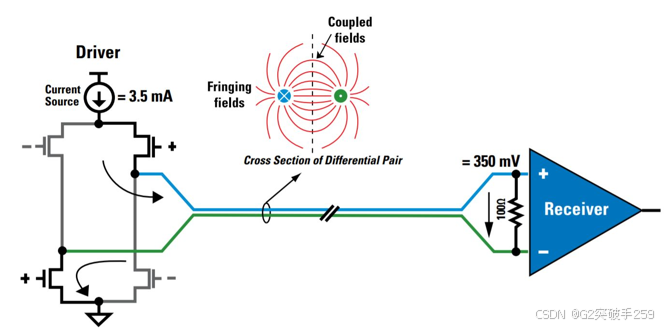

LVDS(Low Voltage Differential Signalin)是一种低摆幅差分信号技术。它使用输出电压摆幅非常低的信号(约 350mV)通过一对差分 PCB 走线或平衡电缆传输数据。它能以高达数千 Mbps 的速度传送串行数据。由于电压信号幅度较低,而且采用恒流源模式驱动,故只产生极低的噪声,消耗非常小的功率,甚至不论频率高低功耗都几乎不变。此外,由于 LVDS 以差分方式传送数据,所以不易受共模噪音影响。

LVDS 的基本工作原理

源端驱动器由一个恒流源(通常约为 3.5mA,最大不超过 4mA)驱动一对差分信号线组成。

接收端的接收器本身为高直流输入阻抗,所以几乎全部的驱动电流都流经 100Ω 的终端匹配电阻,并在接收器输入端产生约 350mV 的电压。

当源端驱动状态反转变化时,流经匹配电阻的电流方向改变,于是在接收端产生高低逻辑状态的变化。

LVDS 特点

LVDS 之所以成为目前高速 I/O 接口的首选信号形式来解决高速数据传输的限制,就是因为它在传输速度、功耗、抗噪声、EMI 等方面具有优势。

- 高速传输能力。在 ANS/TIA-EIA-644 定义中的 LVDS 标准,理论极限速率为 1.923Gbps,恒流源模式、低摆幅输出的工作模式决定着 LVDS 具有高速驱动能力。

- 低功耗特性。LVDS 器件是用 CMOS 工艺实现的,而 CMOS 能够提供较低的静态功耗;当恒流源的驱动电流为 3.5mA,负载(100Ω 终端匹配)的功耗仅为 1.225mW;LVDS 的功耗是恒定的,不像 CMOS 收发器的动态功耗那样相对频率而上升。

- 供电电压低。随着集成电路的发展和对更高数据速率的要求,低压供电成为急需。

- 较强的抗噪声能力。差分信号固有的优点就是噪声以共模的方式在一对差分线上耦合出现,并在接收器中相减,从而可消除噪声,所以 LVDS 具有较强的抗共模噪声能力。

- 有效地抑制电磁干扰。由于差分信号的极性相反,它们对外辐射的电磁场可以相互抵消,耦合得越紧密,泄放到外界的电磁能量就越少,即降低了 EMI。

- 时序定位精确。由于差分信号的开关变化是位于两个信号的交点。而不像普通单端信号依靠高低两个阀值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,有利于高速数字信号的有效传输。

- 适应地平面电压变化范围大。LVDS 接收器可以承受至少 ±1V 的驱动器与接收器之间的地的电压变化。

- 热拔插。恒流式驱动不会对系统造成任何损害,所以 LVDS 驱动器可以带电插拔(即,LVDS 屏线接口若无供电引脚,可以热插拔 LVDS 屏线)。

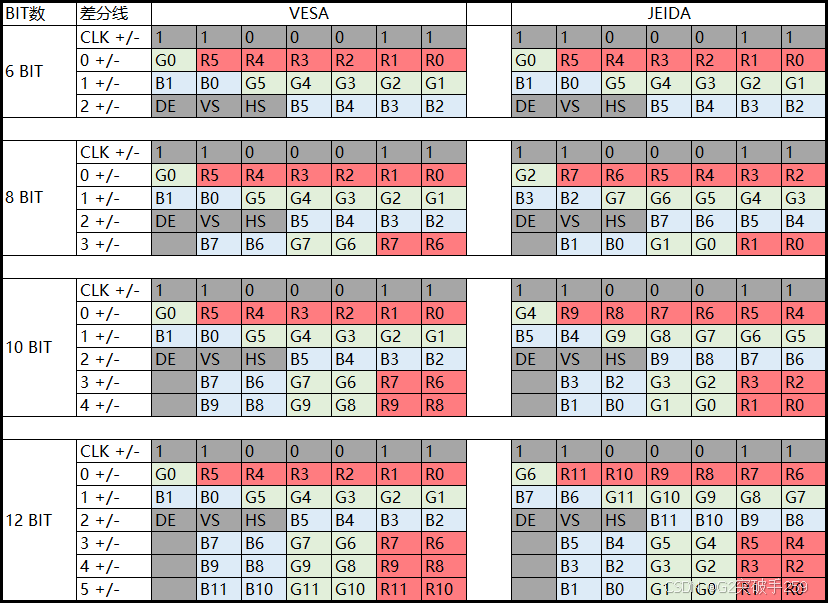

RGB VESA 与 JEIDA 标准

LVDS 信号格式有两种:

一种是 JEIDA 的标准,一种是 VESA 的标准。

| VESA | Video Electronics Standards Association | 视频电子标准协会 |

|---|---|---|

| JEIDA | Japan Electronic Industry Development Association | 日本电子产业发展协会 |

两种标准的区别:

每对低压差分信号上传输的 R、G、B 三色的位数和 HS 、VS、DE 位置不同。

上图中,N 对数据线加 1 对时钟线称为一个 Channel,LVDS 发送器总是将一个像素数据映射到一个 Channel 的一个发送周期(TX CLK)中。

如果是 6BIT 显示屏,则并行数据有 21 位(18 位 RGB 加 3 位控制信号),因此 LVDS 接口每个 Channel 需要 3 对数据线和 1 对时钟线。

如果是 8BIT 显示屏,则并行数据有 27 位(24 位 RGB 加 3 位控制信号),因此 LVDS 接口每个 Channel 需要 4 对数据线和 1 对时钟线。

如果是 10BIT 显示屏,则并行数据有 33 位(30 位 RGB 加 3 位控制信号),因此 LVDS 接口每个 Channel 需要 5 对数据线和 1 对时钟线。

如果是 12BIT 显示屏,则并行数据有 39 位(36 位 RGB 加 3 位控制信号),因此 LVDS 接口每个 Channel 需要 6 对数据线和 1 对时钟线。

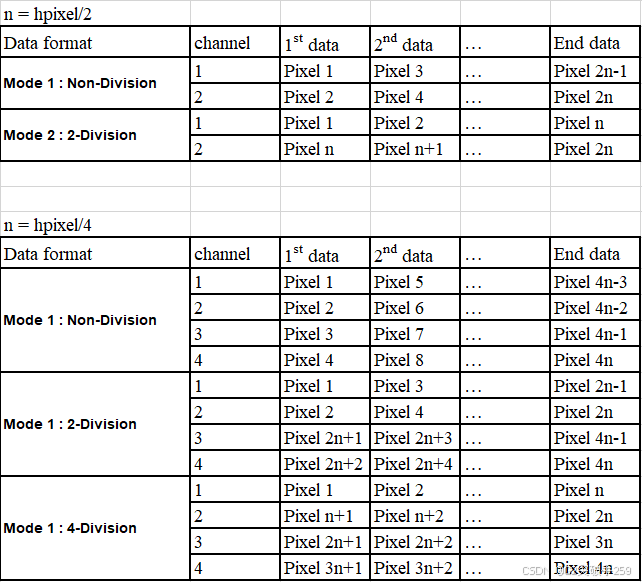

通常,LVDS 接口的时钟为 20MHz 到 85MHz,因此对于输出像素时钟低于 85MHz 的信号,只需 1 个 Channel 就可以;而对于输出像素时钟高于 85MHZ 的信号,比如 1080P/60Hz 的输出,像素显示时钟为 148.5MHz,就不能直接用 1 个 Channel 传输,而是将输出的像素按顺序分为奇像素和偶像素,将所有的奇像素用一组 LVDS 传输,所有的偶像素用另外一组 LVDS 传输。也就是说,需要 2 个 Channel 来传输 1080P/60Hz 的信号。对于像素显示时钟更高的信号,比如 1080P/120Hz 显示,则需要 4 个 Channel 来传输。2Channel、4Channel 的像素分配如下表所示:

SerDes 收发器(Altera/Xilinx)

SerDes 收发器简介

SERDES 是英文 SERializer(串行器)/ DESerializer(解串器)的简称。它是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。

在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。

Serializer 也称为 SerDes 发送端(Tx),把并行信号转化为串行信号。

Deserializer 也称为 SerDes 接收端(Rx),把串行信号转化为并行信号。

以下为本小节讨论的 SerDes 收发器平台信息。

| 平台 | 器件 | 软件版本 |

|---|---|---|

| Altera | Arria 10 | Quartus 22.3 Pro |

| Xilinx | Artix 7 / Kintex 7 | Vivado 2017.4 |

Altera Serdes 收发器

Altera 使用 LVDS SERDES Intel FPGA IP 实现并串转换功能,参考资料 User Guide。

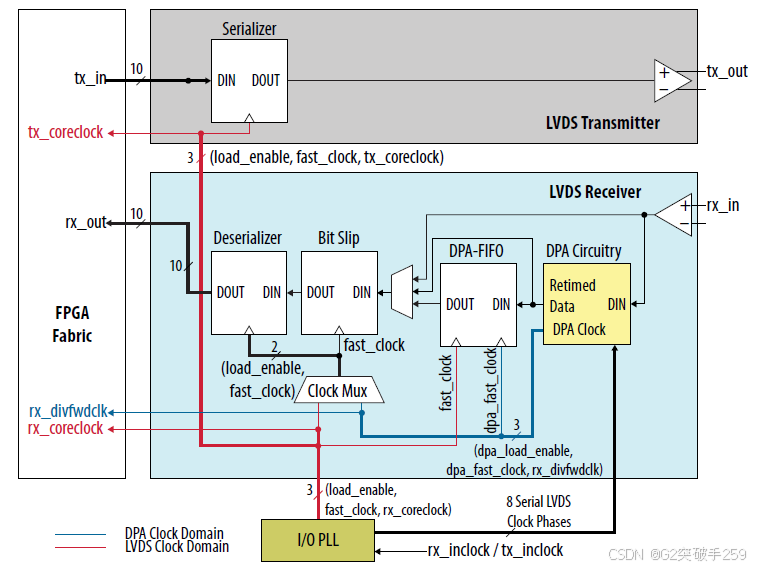

LVDS SERDES 通道图

Serializer

Serializer 由两组寄存器组成。

第一组寄存器使用 LVDS fast clock 从核心捕获并行数据。load_enable clock 与 LVDS fast clock 一起提供,以便在每个 coreclock 周期中启用这些捕获寄存器一次。

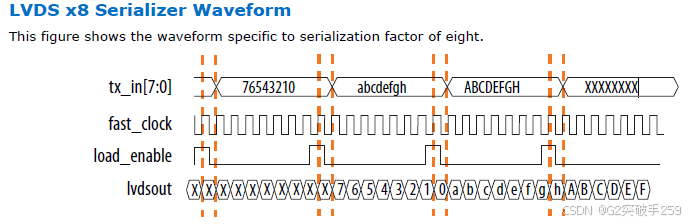

捕获数据后,将其加载到移位寄存器中,移位寄存器以每个 fast clock 时钟周期 1 位的速度将 LSB 移向 MSB。移位寄存器的 MSB 提供 LVDS bit 流。输出缓冲区。因此,高阶位先于低阶位输出。

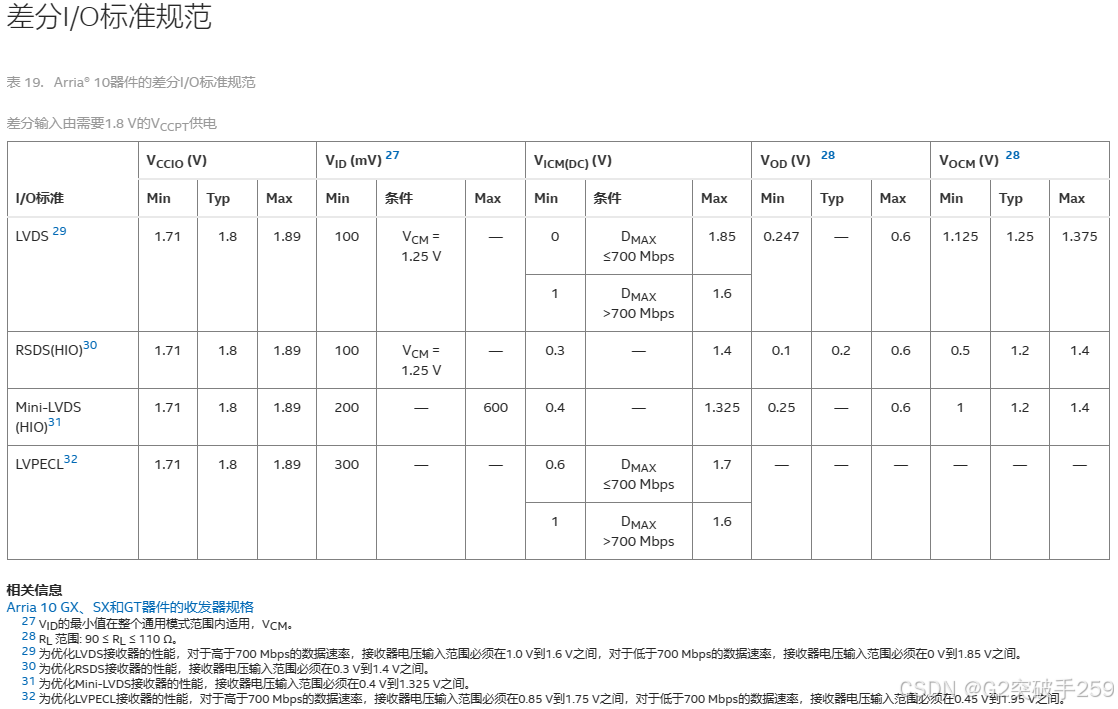

I/O 标准规范

IP 配置

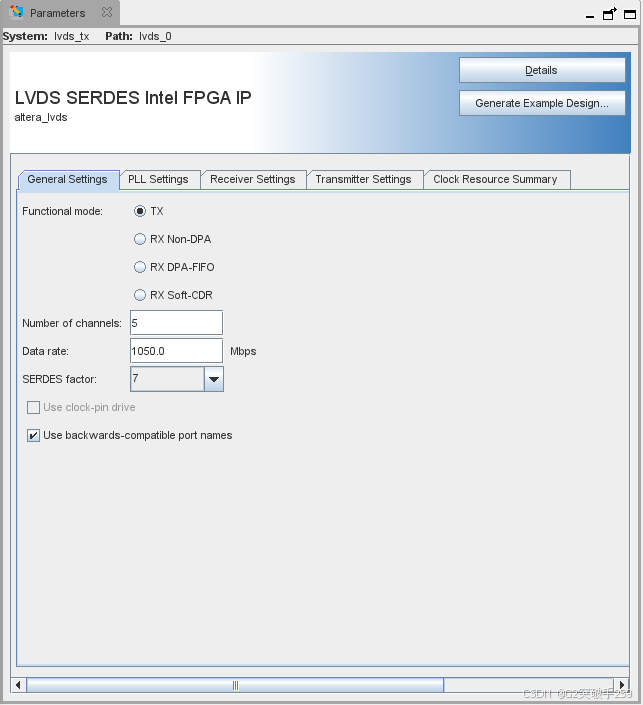

General Settings 配置界面

Functional mode 配置为 TX。

Number of channels 配置为 5。采用 10 BIT 模式输出,有 5 对数据线。

Data rate 配置为 1050.0 Mbps。指定单个串行通道的数据速率,单位为Mbps。根据实际使用需求配置该值。支持范围 150.0 - 1600.0 Mbps(注意,不同速度等级器件的速率上限不一致,详情见文档)。

SERDES factor 配置为 7。指定 LVDS 接口的序列化速率或反序列化速率。根据实际使用需求配置该值。

Use backwardscompatible port names。打开以使用与 ALTLVDS_TX 和 ALTLVDS_RX IP 核兼容的遗留顶级名称。兼容性选项,根据实际使用需求配置。

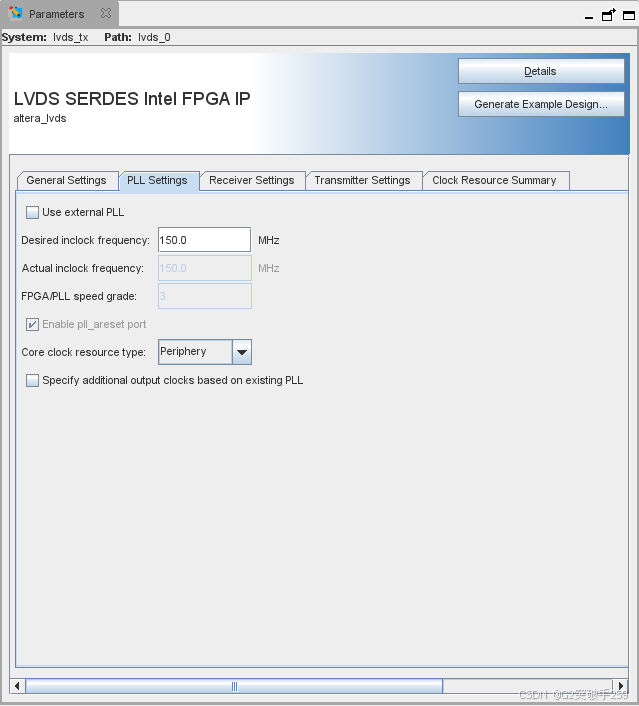

PLL Settings 配置界面

Use external PLL。打开使用外部 PLL: IP 核没有实例化本地 PLL。IP 核创建一系列带有 “ext” 前缀的时钟连接。将这些端口连接到外部生成的锁相环。此选项允许您访问来自锁相环的所有可用时钟,并使用高级锁相环功能,如时钟切换、带宽预置、动态相位步进和动态重新配置。注意:如果您希望将 LVDS 发送器和接收器接口组合在同一个 I/O 组中,则必须打开此选项。 如果不勾选,则使用 SERDES 内部 PLL。inclock:内部 PLL 参考时钟,如果 TX core registers clock 选择 inclock,那么 inclock 的时钟频率必须等于 Data rate/SERDES factor。

Core clock resource type:指定 IP 核将内部生成的 coceclock 导出到哪个时钟网络。可选项:自动、外围时钟网络、全局时钟网络。

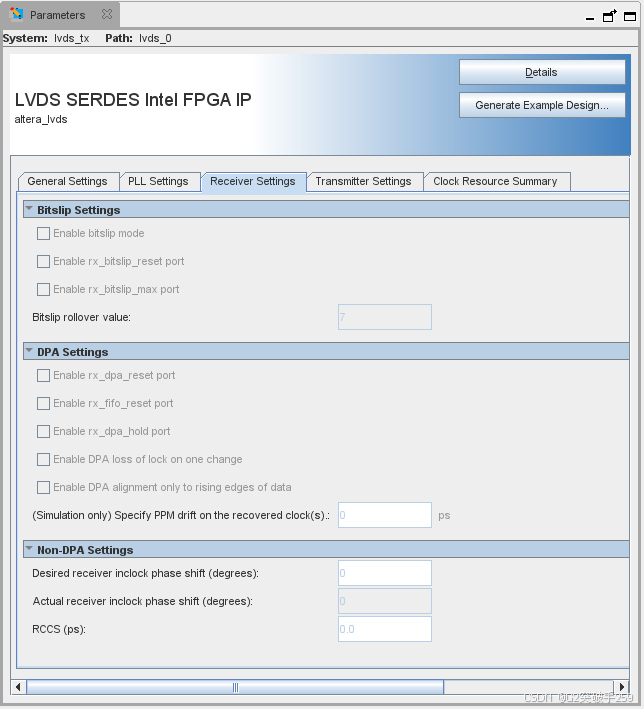

Receiver Settings 配置界面

保持默认配置。

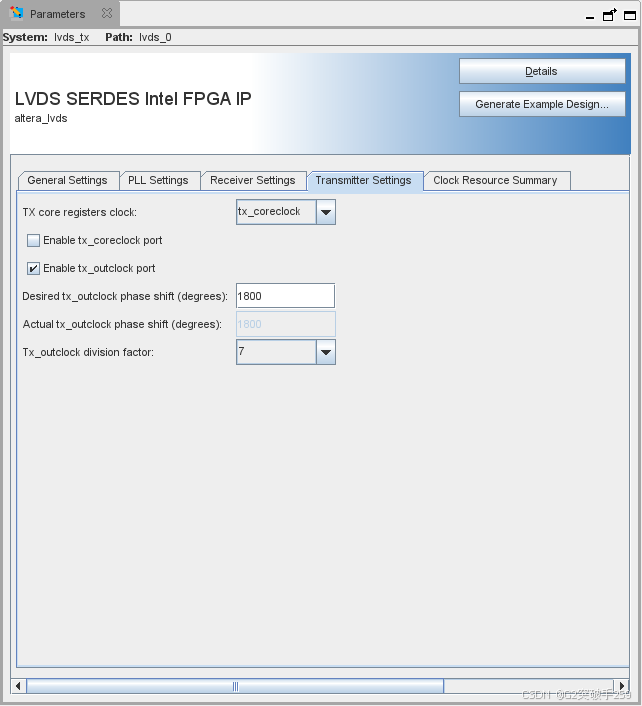

Transmitter Settings 配置界面

TX core registers clock:选择内核寄存器的时钟。可选项:tx_coreclock、inclock。tx_coreclock:选择 tx_coreclock 作为时钟源。inclock:选择内部 PLL 参考时钟 inclock 作为时钟源。选择 inclock,那么 inclock 的时钟频率必须等于 Data rate/SERDES factor。

Enable tx_coreclock port:打开 tx_coreclock 端口以供外部使用。如果需要,英特尔建议使用 tx_coreclock 输出信号。

Enable tx_outclock port:打开 tx_outclock 端口以供外部使用。tx_outclock 的频率取决于 “Tx_outclock division factor” 参数的设置。tx_outclock 的相位取决于 “Desired tx_outclock phase shift (degrees)” 参数的设置。打开此参数将使每个 TX 接口的最大通道数减少一个通道。

勾选 Enable tx_outclock port,此时钟作为 LVDS 接口所需的时钟线。此时钟所需频率为 pixel clock 时钟频率,所以 Tx_outclock division factor 设置为 SERDES factor ,7。此时钟与 LVDS fast clock 的相位差为 5*360 = 1800。

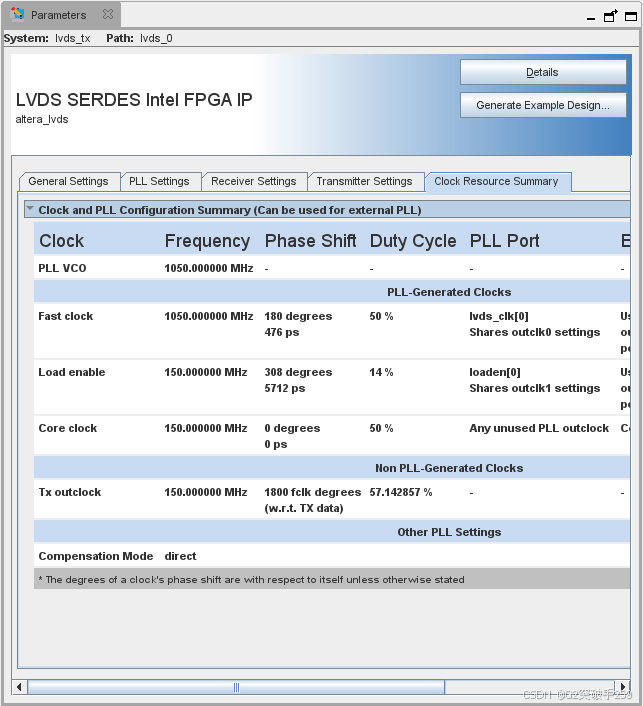

Clock Resource Summary 界面

Clock Resource Summary 选项卡列出所需时钟的所需频率、相移和占空比,以及连接说明。您可以参考此选项卡了解有关配置外部 PLL 的信息并将其连接到 LVDS SERDES IP 核。

Xilinx Serdes 收发器

Xilinx 使用 Output Parallel-to-Serial Logic Resources (OSERDESE2) 实现并串转换功能。参考资料 ug471。

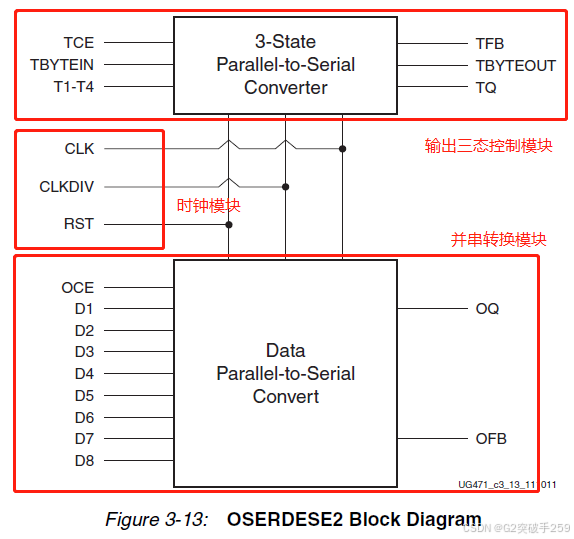

7 系列器件中的 OSERDESE2 是一种专用的并行-串行转换器,具有特定的时钟和逻辑资源,旨在促进高速源同步接口的实现。每个 OSERDESE2 模块都包含一个用于数据和三状态控制的专用序列化器。数据和三状态序列化器都可以配置为 SDR 和 DDR 模式。数据序列化可以达到 8:1(如果使用 OSERDESE2 宽度扩展,则为 10:1 和 14:1)。三状态序列化可以高达 14:1。有一个专用的 DDR3 模式来支持高速内存应用程序。OSERDESE2 的框图如下所示,突出显示了该模块的所有主要组件和特性。

数据并行-串行转换器

一个 OSERDESE2 块中的数据并行到串行转换器从 fabric 接收 2 到 8 位并行数据(如果使用 OSERDESE2 宽度扩展则为 14 位),序列化数据,并通过 OQ 输出给 IOB。并行数据从最低阶数据输入引脚序列化到最高阶(即 D1 输入引脚上的数据是在 OQ 引脚上传输的第一个 bit)。数据并行转串行转换器有两种模式:单数据速率(SDR)和双数据速率(DDR)。

OSERDESE2 使用两个时钟 CLK 和 CLKDIV 进行数据速率转换。CLK 是高速串行时钟,CLKDIV 是分频并行时钟。CLK 和 CLKDIV 必须相位对齐。

在使用之前,必须对 OSERDESE2 应用重置。OSERDESE2 包含一个控制数据流的内部计数器。重置解除与 CLKDIV 同步失败将产生意外输出。

三状态并行-串行转换器

除了并行到串行的数据转换,OSERDESE2 模块还包含一个并行到串行转换器,用于 IOB 的三状态控制。与数据转换不同,三状态转换器最多只能序列化四位并行的三态信号。三状态转换器不能级联。

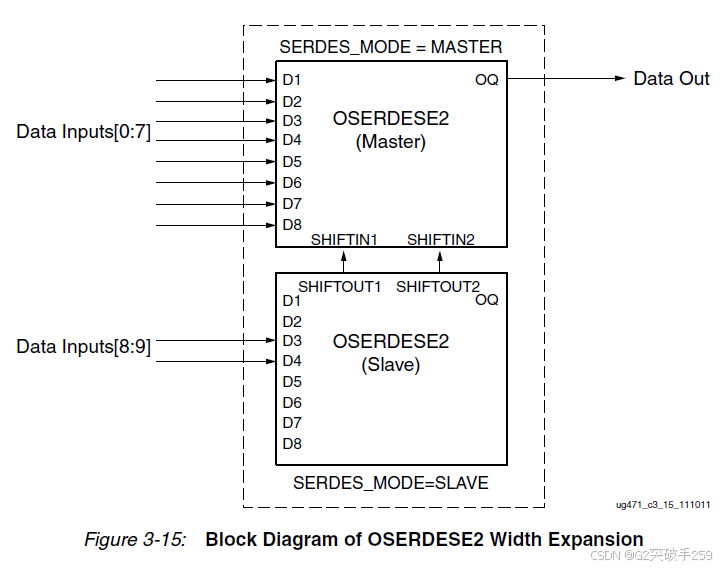

OSERDESE2 宽度扩展(级联模式)

OSERDESE2 模块可用于构建大于 8:1 的并行-串行转换器。在每个 I/O 块中有两个 OSERDESE2 模块;一个主一个从。通过将主 OSERDESE2 的 SHIFTIN 端口连接到从 OSERDESE2 的 SHIFTOUT 端口,并行串行转换器可以扩展到 10:1 和 14:1(仅限DDR模式)。对于差分输出,主 OSERDESE2 必须位于差分输出对的正端(_P引脚)。当输出不是差分时,与从 OSERDESE2 关联的输出缓冲区不可用,并且不能使用宽度扩展。

当使用互补的单端标准(例如 DIFF_HSTL 和 DIFF_SSTL)时,不能使用宽度扩展。这是因为一个 I/O 块中的两个 OLOGICE2/3 块都被互补的单端标准用来传输两个互补的信号,没有 OLOGICE2/3 块可用于宽度扩展。

下图给出了使用主、从 OSERDESE2 模块的 10:1 DDR 并行转串行转换器的框图。在这种情况下,端口 D3-D4 用于连接 OSERDESE2 上并行接口的最后两位。

I/O 标准规范

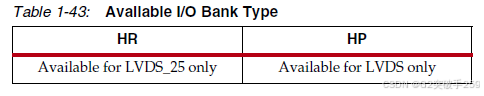

LVDS and LVDS_25 (Low Voltage Differential Signaling)

LVDS I/O 标准仅在 HP I/O 库中可用。当实现可选的内部差分终端(DIFF_TERM = TRUE)时,它需要一个 Vcco 以 1.8V 的电压为输出和输入供电。

LVDS_25 I/O 标准仅在 HR I/O 库中可用。当实现可选的内部差分终端(DIFF_TERM = TRUE)时,它需要一个 Vcco 以 2.5V 的电压为输出和输入供电。

LVDS 发送端

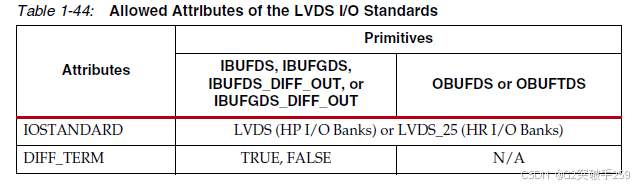

- 7 系列 FPGA LVDS 发送端不需要任何外部终端。7 系列 FPGA LVDS 电流模驱动允许的属性如表 1-44 所示。7 系列 FPGA LVDS 电流模式驱动器是一个真正的电流源,并产生适当的(EIA/TIA 兼容)LVDS 信号。

LVDS 接收端

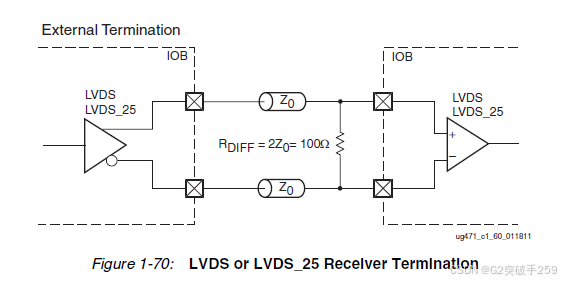

- 图 1-70 为带 50Ω 传输线的单板上 LVDS 或 LVDS_25 接收机的差分端接示例。

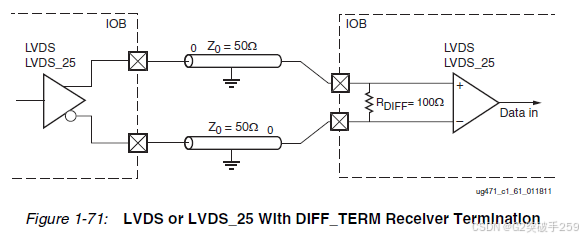

- 图 1-71 为带 50Ω 传输线的单板上 LVDS 或 LVDS_25 接收机的差分端接示例。

在 I/O 组中使用差分输入(如 LVDS 和 LVDS_25),差分输入的电压水平不是这些标准输出所需的标称电压(LVDS 输出 1.8V, LVDS_25 输出 2.5V)是可以接受的。但是,必须满足下列标准:

- 不使用可选的内部差分终止(DIFF_TERM = FALSE,这是默认值)。

- 输入端差分信号满足特定器件系列数据手册 “推荐工作条件” 表中的 VIN 要求。

- 输入端差分信号满足特定器件系列数据表中相应 LVDS 或 LVDS_25 直流规格表中的 VIDIFF (min)要求。

- 对于双向配置的 HR I/O bank,总是使用内部差分终端。

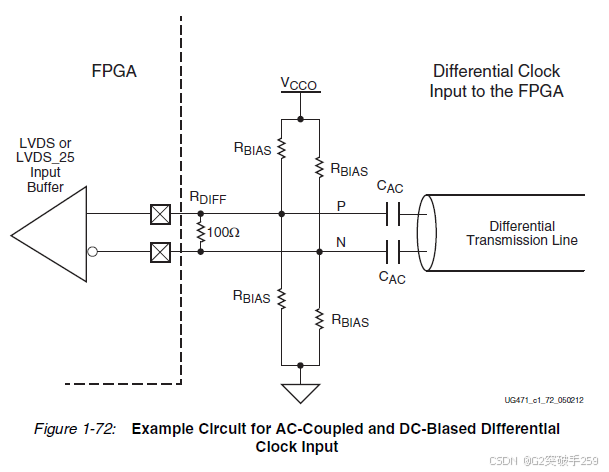

实现上述标准的一种方法是使用外部电路,使交流耦合器和直流偏置输入信号。图 1-72 给出了为差分时钟输入提供交流耦合和直流偏置电路的示例电路。RDIFF 提供 100Ω 差分接收端终端,因为内部 DIFF-TERM = FALSE。为了使输入噪声裕度最大化,所有 RBIAS 电阻应该是相同的值,基本上创建一个 Vcco/2 的 VICM 电平。建议使用 10K-100KΩ 范围内的电阻。交流耦合电容器 CAC 的典型值在 100nF 范围内。所有组件应放置在靠近 FPGA 输入的位置。

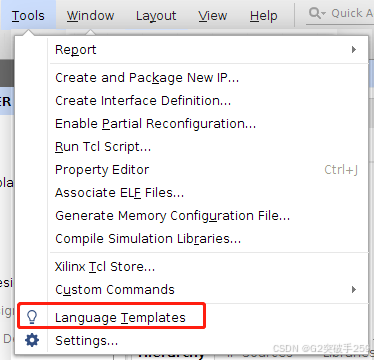

OSERDESE2 源语

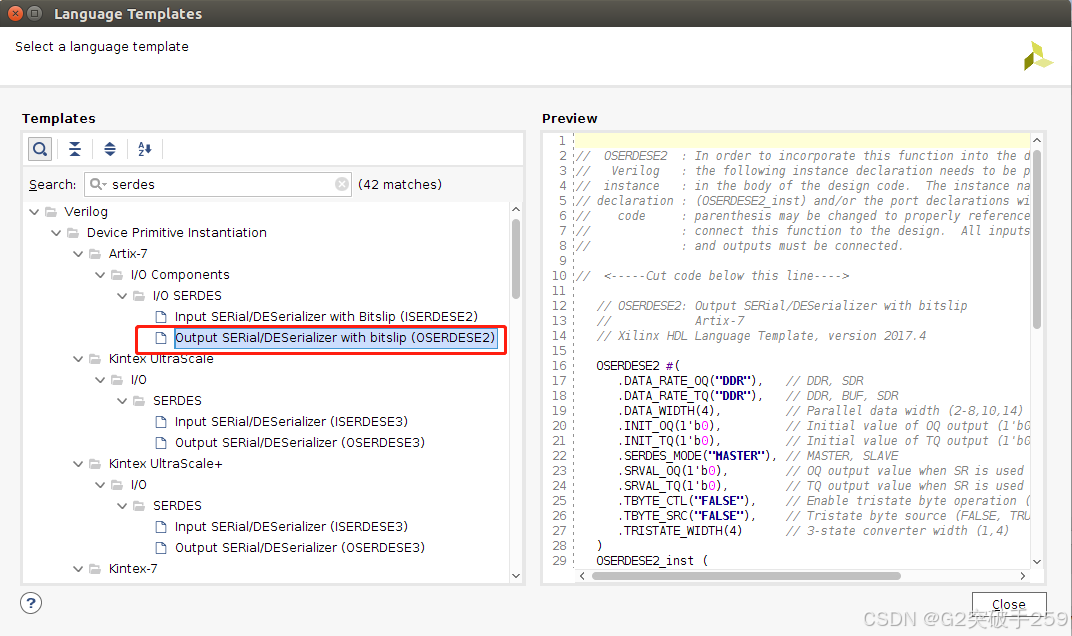

打开 Tools,找到 Language Templates,可以搜索到 OSERDESE2 源语。如下图所示:

源语如下所示:

// OSERDESE2 : In order to incorporate this function into the design,

// Verilog : the following instance declaration needs to be placed

// instance : in the body of the design code. The instance name

// declaration : (OSERDESE2_inst) and/or the port declarations within the

// code : parenthesis may be changed to properly reference and

// : connect this function to the design. All inputs

// : and outputs must be connected.

// <-----Cut code below this line---->

// OSERDESE2: Output SERial/DESerializer with bitslip

// Artix-7

// Xilinx HDL Language Template, version 2017.4

OSERDESE2 #(

.DATA_RATE_OQ("DDR"), // DDR, SDR

.DATA_RATE_TQ("DDR"), // DDR, BUF, SDR

.DATA_WIDTH(4), // Parallel data width (2-8,10,14)

.INIT_OQ(1'b0), // Initial value of OQ output (1'b0,1'b1)

.INIT_TQ(1'b0), // Initial value of TQ output (1'b0,1'b1)

.SERDES_MODE("MASTER"), // MASTER, SLAVE

.SRVAL_OQ(1'b0), // OQ output value when SR is used (1'b0,1'b1)

.SRVAL_TQ(1'b0), // TQ output value when SR is used (1'b0,1'b1)

.TBYTE_CTL("FALSE"), // Enable tristate byte operation (FALSE, TRUE)

.TBYTE_SRC("FALSE"), // Tristate byte source (FALSE, TRUE)

.TRISTATE_WIDTH(4) // 3-state converter width (1,4)

)

OSERDESE2_inst (

.OFB(OFB), // 1-bit output: Feedback path for data

.OQ(OQ), // 1-bit output: Data path output

// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each)

.SHIFTOUT1(SHIFTOUT1),

.SHIFTOUT2(SHIFTOUT2),

.TBYTEOUT(TBYTEOUT), // 1-bit output: Byte group tristate

.TFB(TFB), // 1-bit output: 3-state control

.TQ(TQ), // 1-bit output: 3-state control

.CLK(CLK), // 1-bit input: High speed clock

.CLKDIV(CLKDIV), // 1-bit input: Divided clock

// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each)

.D1(D1),

.D2(D2),

.D3(D3),

.D4(D4),

.D5(D5),

.D6(D6),

.D7(D7),

.D8(D8),

.OCE(OCE), // 1-bit input: Output data clock enable

.RST(RST), // 1-bit input: Reset

// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each)

.SHIFTIN1(SHIFTIN1),

.SHIFTIN2(SHIFTIN2),

// T1 - T4: 1-bit (each) input: Parallel 3-state inputs

.T1(T1),

.T2(T2),

.T3(T3),

.T4(T4),

.TBYTEIN(TBYTEIN), // 1-bit input: Byte group tristate

.TCE(TCE) // 1-bit input: 3-state clock enable

);

// End of OSERDESE2_inst instantiation

DATA_RATE_OQ 属性

DATA_RATE_OQ 属性定义了数据是单数据速率还是双数据速率。该属性允许的值是 SDR 和 DDR。缺省值为 DDR。

DATA_RATE_TQ 属性

DATA_RATE_TQ 属性定义以单数据速率(SDR)还是双数据速率(DDR)处理三状态控制。该属性允许的值是 SDR,DDR 或 BUF。缺省值为 DDR。在 SDR 和 DDR 模式中,使用 4 个 T 输入,它们的行为可以用 TRISTATE WIDTH 属性配置。在 BUF 模式下,绕过 SDR 和 DDR 模式寄存器,因此应使用 T1 输入。应用于 T1 输入的信号与所有其他信号是异步的,因为它只是通过 OSERDESE2。

DATA_WIDTH 属性

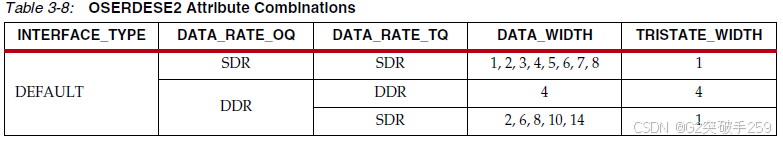

DATA_WIDTH 属性定义并行转串行转换器的并行数据输入宽度。该属性的可能值取决于 DATA_RATE_OQ 属性。当 DATA_RATE_OQ 设置为SDR时,DATA_WIDTH 属性的可能值为 2、3、4、5、6、7 和 8。当 DATA_RATE_OQ 设置为 DDR 时,DATA_WIDTH 属性的可能值为4、6、8、10 和 14。

当 DATA WIDTH 设置为大于 8 的宽度时,必须将一对 OSERDESE2 配置为主从配置。参见 OSERDESE2 宽度扩展。

SERDES_MODE 属性

SERDES_MODE 属性定义在使用宽度扩展时 OSERDESE2 模块是主模块还是从模块。取值为 MASTER 和 SLAVE。默认值为 MASTER。参见 OSERDESE2 宽度扩展。

TRISTATE_WIDTH 属性

TRISTATE_WIDTH 属性定义了 3 状态控制并行转串行转换器的并行 3 状态输入宽度。此属性的可能值取决于 DATA_RATE_TQ 属性。当 DATA_RATE_TQ 设置为 SDR 或 BUF 时,TRISTATE_WIDTH 属性只能设置为 1。当 DATA_RATE_TQ 设置为 DDR 时。TRISTATE WIDTH 属性的可能值是 1 和 4。

TRISTATE_WIDTH 不能设置为大于 4 的宽度。当 DATA_WIDTH 大于 4 时,将 TRISTATE_WIDTH 设置为 1。

表 3-8 显示了使用 OSERDESE2 的有效设置和组合。

OSERDESE2 时钟配置方法

CLK 和 CLKDIV 的相位关系在并行转串行转换过程中非常重要。CLK 和 CLKDIV(理想情况下)在一个公差范围内相位对齐。

FPGA 内有几种时钟配置方法,以帮助设计满足CLK 和 CLKDIV 的相位关系要求。OSERDESE2 唯一有效的时钟配置方法是:

- CLK 由 BUFIO 驱动,CLKDIV 由 BUFR 驱动

- CLK 和 CLKDIV 由相同 MMCM 或 PLL 的 CLKOUT[0:6] 驱动

当使用 MMCM 驱动 OSERDESE2 的 CLK 和 CLKDIV 时,提供 OSERDESE2 的缓冲区类型不能混合。例如,如果 CLK 是由 BUFG 驱动的,那么 CLKDIV 也必须由 BUFG 驱动。

OSERDESE2 时序模型和参数

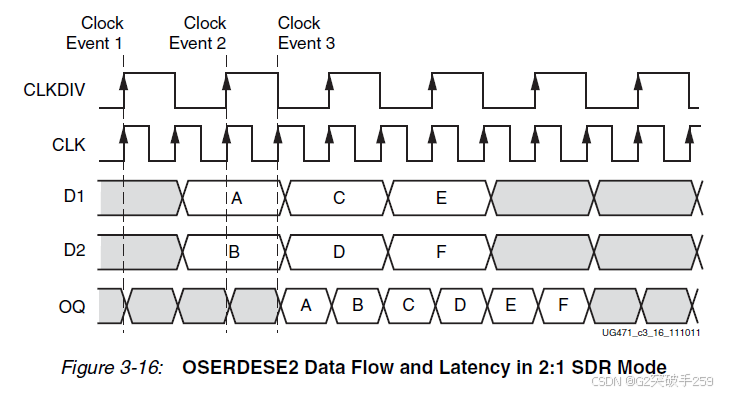

SDR 模式时序

Clock Event 1

在 CLKDIV 的上升沿上,AB 从 FPGA 逻辑驱动到 OSERDESE2 的 D1 和 D2 输入(经过一些传播延迟)。

Clock Event 2

在 CLKDIV 的上升沿上,AB 从 D1 和 D2 输入采样到 OSERDESE2。

Clock Event 3

数据位 A 在 AB 被采样到 OSERDESE2 后的第一个 CLK 周期出现在 OQ。

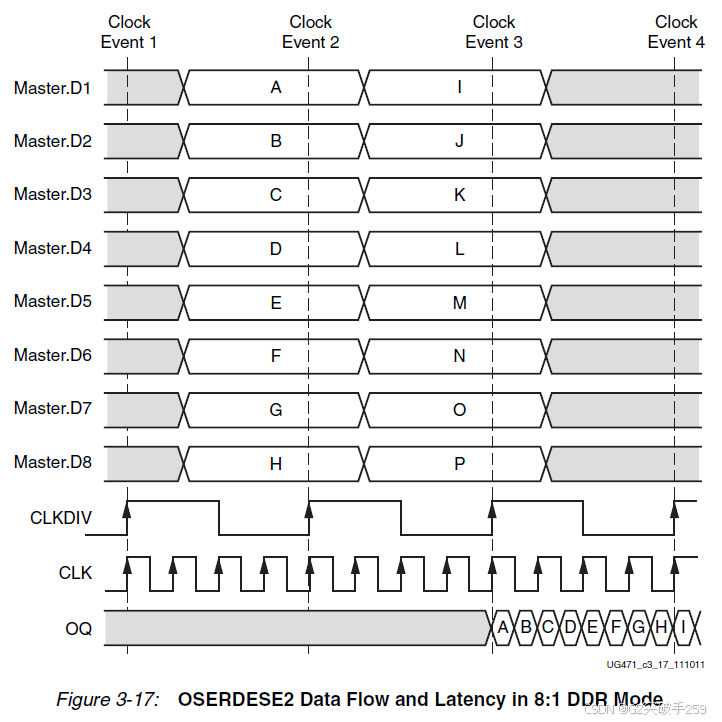

DDR 模式时序

Clock Event 1

在 CLKDIV 的上升沿上,ABCDEFGH 从 FPGA 逻辑驱动到 OSERDESE2 的 D1-D8 输入。

Clock Event 2

在 CLKDIV 的上升沿上,ABCDEFGH 从 D1-D8 输入采样到 OSERDESE2。

Clock Event 3

数据位 A 在 ABCDEFGH 被采样到 OSERDESE2 后的第四个 CLK 周期出现在 OQ。

第二个数据 IJKLMNOP 从 D1-D8 采样到 OSERDESE2。

Clock Event 4

在时钟事件 3 和 4 之间,整个 ABCDEFGH 在 OQ 上串行传输,在一个 CLKDIV 周期中总共传输 8 位。

数据位 I 在 IJKLMNOP 被采样到 OSERDESE2 后的第四个 CLK 周期出现在 OQ。

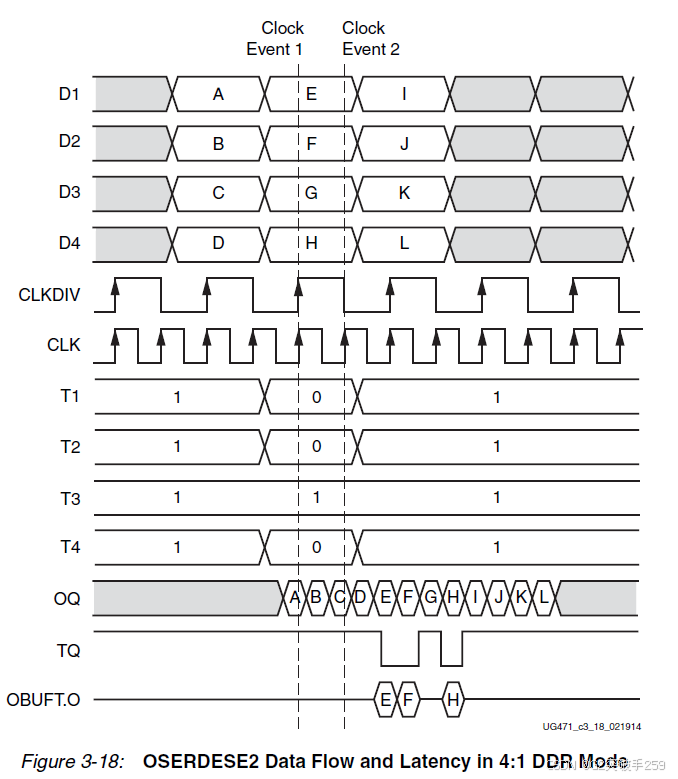

DDR 三状态控制模式时序

Clock Event 1

T1、T2 和 T4 被驱动为 Low 以释放三态条件。OSERDESE2 中 T1-T4 和 D1-D4 的序列化路径是相同的(包括延迟),因此在时钟事件 1 期间,位 EFGH 总是与 T1-T4 引脚上呈现的 0010 对齐。

Clock Event 2

数据位 E 在 EFGH 被采样到 OSERDESE2 后的第一个 CLK 周期出现在 OQ。

时钟事件 1 期间 T1的 3-state bit 0 在0010被采样到 OSERDESE2 3-state block 后的第一个 CLK 周期出现在 TQ。

参考设计

Xilinx 提供了专门用于 LVDS 视频信号的参考设计 XAPP585:LVDS Source Synchronous 7:1 Serialization and Deserialization Using Clock Multiplication。

Xilinx 7 系列 FPGA 包含 ISERDES 和 OSERDES 原语,使得串行器和反串行器电路的设计非常简单。本应用说明描述了如何有效地将 ISERDES 和 OSERDES 与混合模式时钟管理器(MMCM)或锁相环(PLL)结合使用,使用低压差分信号(LVDS)进行 7:1 数据的接收和传输,数据传输速度从 415 Mb/s 到 1200 Mb/s,具体取决于所使用的系列和速度等级。

在 Vivado 平台使用 XAPP585 参考设计时,需要将约束文件 *.ucf 更新为 *.xdc,具体操作方式为:How to use Xapp585 in Vivado。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?