产品特点

1.纯FPGA逻辑实现,物理层使用Xilinx 7系列PCIe核,基于AX7350开发板(ZYNQ7035、PCIe2.0 X4接口、三星970 PCIe SSD)开发并充分验证,该平台下全盘读速率1598 MB/s,全盘写速率1315 MB/s,可根据客户平台移植,平台升级后(如使用PCIe3.0 X4接口和更大容量的PCIe SSD)性能还可以提升;

2.访问接口简单,用户可以将此IP当作一块只增加一些读、写命令握手信号接口的片上DPRAM模块来使用,支持最大队列数16对,最大队列深度16383,可根据用户需求定制;

3.客户可以根据自己需求定制 NVMe IP,还可以在此基础上定制FPGA纯逻辑实现的文件系统 exFAT IP(参网页:CSDN博客 - 基于 NVMe 的 exFAT 文件系统 FPGA IP 简介,视频:B站视频 - 基于 NVMe 的带 exFAT 文件系统的高速数据存储演示),以及需要支持的文件格式(如.txt /.bmp /.avi等);

4.已结合客户需要,成功移植到 K7、PCIe X2等平台,已成功应用于GNSS采集存储项目。

相关图片

1.NVMe 原理

2. NVMe FPGA IP开发平台(AX7350开发板)

3. NVMe FPGA IP 对外接口

4. NVMe FPGA IP 资源消耗报表(ZYNQ 7035)

5.读写测试之连续扇区读写

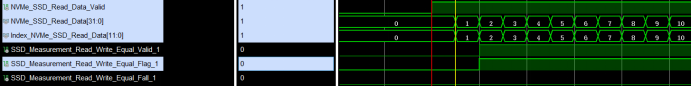

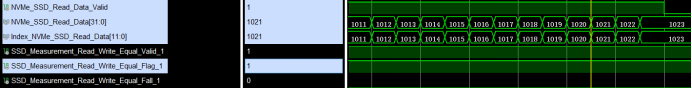

说明:使用8个连续扇区(每个扇区512字节)测试,测试数据从0,1,2…递增至1023,每个测试数据占据4字节,该测试用于片上逻辑比对写、读数据是否一致。

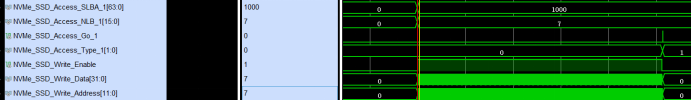

(1)单次8扇区写

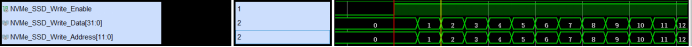

数据波形放大(写数据与写地址相同)

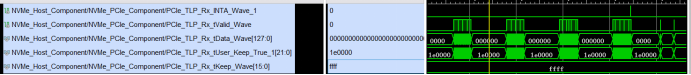

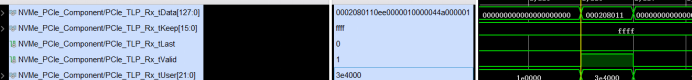

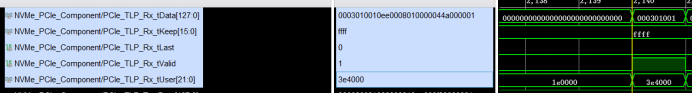

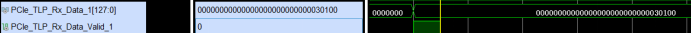

PCIe 底层波形

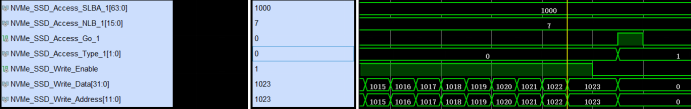

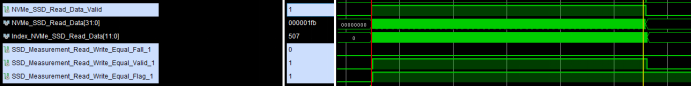

(2)单次8扇区读

数据波形放大(读数据与读地址相同)

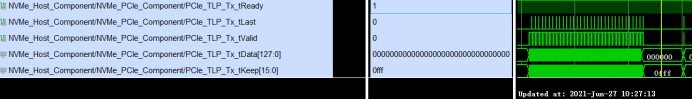

PCIe 底层波形

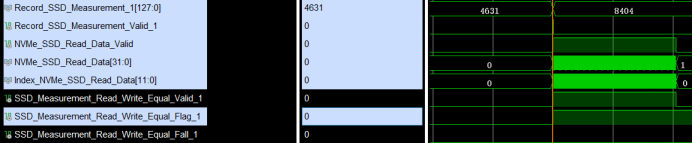

(3)扇区读写对比测试

(4)取下 SSD,连接 PC,使用 WinHex 分析写入数据

第1扇区

…(省略第2-7扇区)

第8扇区

6.读写测试之指定位置读写

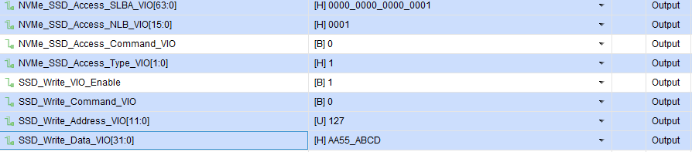

(1)指定第 1 扇区中偏移地址 127 中写入 AA55_ABCD

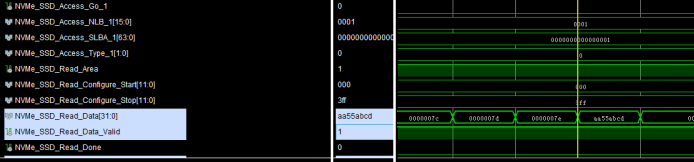

(2)指定第 1 扇区中偏移地址 127 中读出 AA55_ABCD

(3)取下 PCIe SSD,连接 PC ,使用 WinHex 分析写入数据

7.NVMe 协议相关寄存器

(1)PCIe Class Code,NVMe 协议码 0x010802

(2)VS – Version,0x00010300 表示 NVMe 协议版本 1.3

WX:18810831718

520

520

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?