此为一个学习记录文,内容可能从书上《SoC设计方法与实现,郭炜等电子工业出版社》来,也可能从网络来。

目录

软、硬件协同设计:

SoC 通常被称作系统级芯片或者片上系统,作为一个完整的系统,其包含了硬件和软件两部分内容。这里所说的硬件指 SoC芯片部分,软件是指运行在 SoC 芯片上的系统及应用。

软、硬件协同设计指的是软、硬件的设计同步进行,在系统定义的初始阶段两者就紧密相连。近年来,由于电子系统级设计 (ESL, Electronic Sxstern Level Design)工具的发展,软、硬件协同设计已被逐渐采用。

这种方法使软件设计者在硬件设计完成之前就可以获得软件开发的虚拟硬件平台,在虚拟平台上开发应用软件,评估系统架构设计,从而使硬件设计工程师和软件设计工程师联合进行 SoC 系统芯片的开发及验证。

这样并行设计不仅减少了产品开发时间,同时大大提高了芯片一次流片成功的概率。

过程:

系统需求说明:系统设计从确定所需的功能开始,包含系统基本输入和输出,及基本算法需求,以及系统要求的功能、性能、功耗、成本和开发时间等。这一步确定系统的设计流程。

算法建模与仿真:确定流程后,设计者使用EDA工具创建整个系统的高级算法模型 和 仿真模型。有了模型,就可以得到软、硬件协调仿真所需的可执行说明文档。

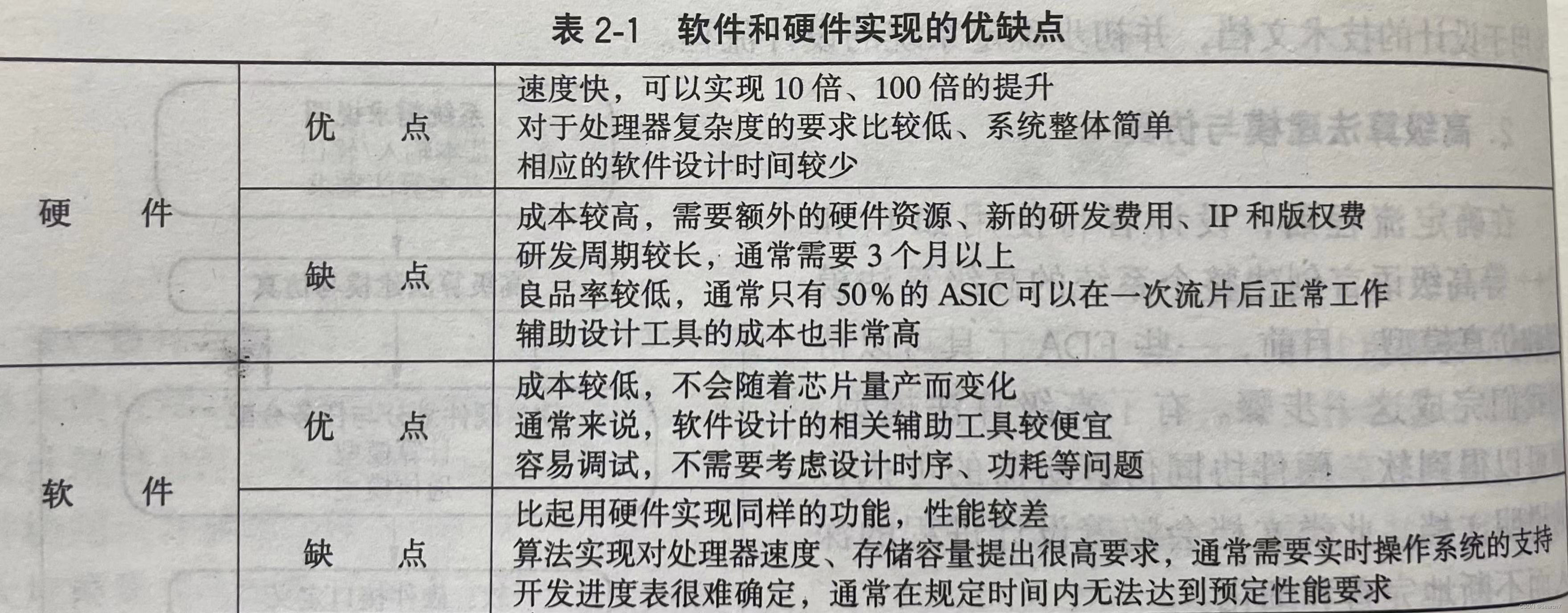

软、硬件划分过程:软、硬件划分和任务分配,划分哪些功能由硬件完成,哪些由软件完成。划分的合理性对系统的实现比较重要。通常,在复杂的系统中,有些功能既可以用软件实现,也可以用硬件实现,这取决于所要达到的性能指标与实现的复杂程度及成本控制等因素。

采用硬件作为解决方案的好处有:由于增加了特定的硬件实现模块,(通常是硬件加速器),因而可使系统的性能提升,仅就速度而言可以提高 10倍,甚至 100 倍;增加的硬件所提供的功能可以分担原先处理器的部分功能,这一点有助于降低处理器的复杂程度,使系统整体显得简单。

硬件解诀方案也存在一些不利的地方:添加新的硬件必然会提高成本,主要花费在购买IP和支付版权费等方面;硬件的研发周期通常都比较长,中等规模的开发团队开发一套复杂程度一般的硬件系统至少需要3个月的时间;要改正硬件设计存在的错误,可能需要再次流片;相比于软件设计工具,硬件设计工具(EDA)要昂贵许多,这也使得设计成本增加。

采用软件实现作为解决方案的好处有:软件产品的开发更灵活,修改软件设计的错误成本低、周期短;受芯片销量的影响很小,即使所开发的软件不用在某一特定芯片上,也可以应用到其他硬件设备上,因而市场的风险比较低。软件解决方案也存在着难以克服的不足之处:软件实现从性能上来说不及硬件实现;采用软件实现对算法的要求更高,这又对处理器的速度、存储器的容量提出了更严格的条件,一般还需要实时操作系统的支持。

软、硬件划分的过程通常是将应用一一在特定的系统架构上映射,搭建系统的虚拟平台,然后在平台上进行性能评估,多次优化系统架构。系统架构的选择需要在成本和性能之间折中。

软、硬件同步设计:

硬件设计包括:RTL设计和集成、综合、布局布线及最后的流片,

软件设计包括:算法优化、应用开发、以及操作系统、接口驱动、和应用软件的开发。

硬件系统测试:协同设计的最后一步是硬件系统的测试。系统测试策略是根据设计的层次结构制定的。首先是测试子模块的正确性,接着验证子模块的接口部分及总线功能,然后在整个搭建好的芯片上运行实际的应用软件或测试平台。这一步通常也称为软、硬件协同仿真验证,软件將作为硬件设计的验证向量,这样不仅可以找出硬件设计中的问题,同时也验证了软件本身的正确性。可以说验证仿真贯穿于整个软、硬件协同设计的流程中,为了降低设计风险,在流程的每一步都会进行不同形式的验证和分析。

总之,协同设计方法的关键是在抽象级的系统建模。目前,对该领城的研究非常活跃,将来可以预见描述语言、结构定义及算法划分工具会被广泛使用。

基于标准单元的SoC设计流程:

soc芯片设计(硬件设计)是以IP核(满足特定规范,能在设计中复用的功能模块)为基础,以分层次的硬件描述语言为系统功能和结构的主要描述手段,并借助于EDA 工具进行芯片设计的过程。

设计周期、进度和人力资源安排是关系到产品成败与否的关键,因为目前电子产品的市场生命周期越来越短,这就需要迅速地推出自己的产品来抢占市场。

1. 硬件设计定义说明(Hardware Design Specification)

硬件设计定义说明描述芯片总体结构、规格参数、模块划分、使用的总线,以及各个模块的详细定义等。

2.模块设计及 IP 复用 (Module Design & IP Reuse)

模块设计及 IP 复用是根据硬件设计所划分出的功能模块,确定需要重新设计的部分及可复用的 IP核。IP 核可自主研发或者购买其他公司的 IP。目前,设计的输人是采用硬件描述语言(HDL),如 Verilog 或 VHDL,所以,数字模块的设计通常称为 RTL代码编写。

3.顶层模块集成 (Top Level Integration)

顶层模块集成将各个不同的功能模块,包括新设计的与复用的整合在一起,形成一个完整的设计。通常采用硬件描述语言对电路进行描述,其中需要考虑系统时钟/复位、I/O 环等问题。

4. 前仿真 (Pre-layout Simulation)

前仿真也叫 RTL级仿真,功能仿真。通过 HDL 放真器验证电路逻辑功能是否有效,即HDL描述是否符合设计所定义的功能期望。在前仿真时,通常与具体的电路实现无关,没有时序信息。

5. 逻辑综合 (Logic Synthesis)

未完,待后期待续,,,,,

659

659

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?