简介

SPI 全称为Serial Peripheral interface(串行外设接口),串行同步通讯。SPI是一种高速的,全双工(同时发送和接收),同步的通信总线,并且在芯片的管脚上只占用四根线,可以节约管脚,节省空间。SPI主要应用在 EEPROM,FLASH,ADC/DAC,还有数字信号处理器和数字信号解码器之间。

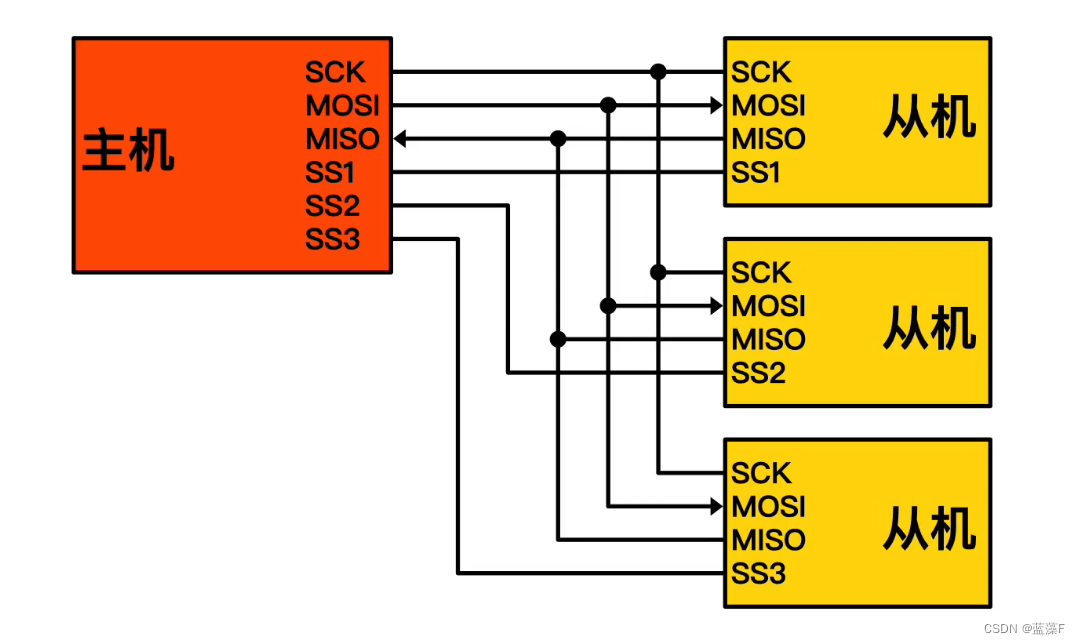

一主多从

一个SPI通讯系统包含一个(且只能是一个)主设备,一个或多个从设备。主设备提供SPI时钟,且都是由主设备发起读写操作。当存在多个从设备时,通过各自的片选信号进行管理。

SPI只有主模式和从模式之分,没有读和写的说法,外设的写操作和读操作是同步完成的。如果只进行写操作,主机只需忽略接收到的字节;反之,若主机要读取从机的一个字节,就必须发送一个空字节来引发从机的传输。也就是说,你发一个数据必然会收到一个数据;你要收一个数据必须也要先发一个数据。

四条信号线

- 片选信号线:CS/SS 大部分都是低电平有效,具体要看连接的芯片手册

- 时钟信号线:SCK 主设备产生

- 发送信号线:MOSI

- 接收信号线:MISO

工作模式

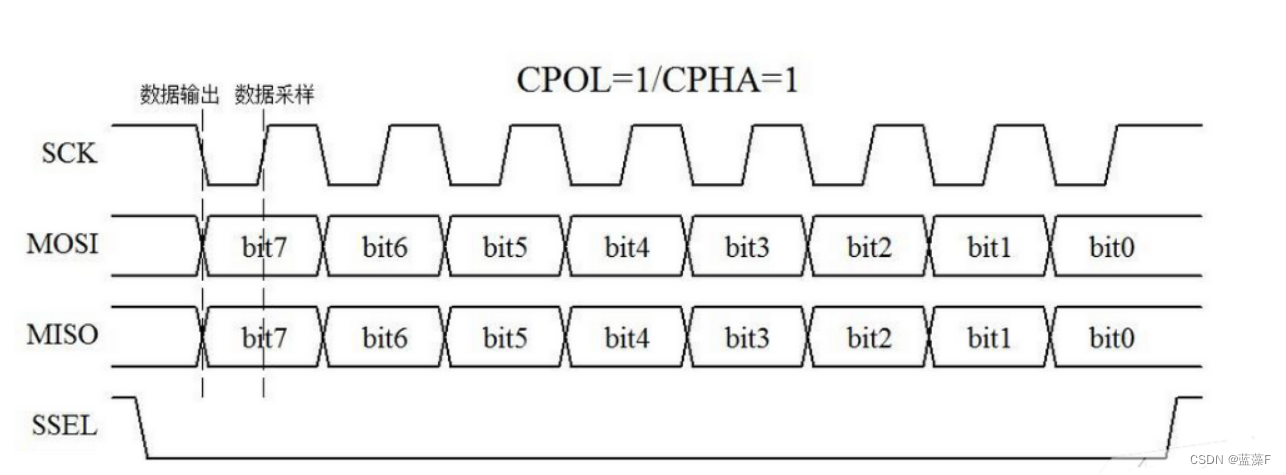

SPI工作模式共有四种,不同点在于时钟空闲时的电平状态和在第几个时钟沿采集数据。

时钟极性(CPOL)定义了时钟空闲状态电平:

- CPOL=0,表示当SCLK=0时处于空闲态,所以有效状态就是SCLK处于高电平时

- CPOL=1,表示当SCLK=1时处于空闲态,所以有效状态就是SCLK处于低电平时

时钟相位(CPHA)定义数据的采集时间。

- CPHA=0,在时钟的第一个跳变沿(上升沿或下降沿)进行数据采样。

- CPHA=1,在时钟的第二个跳变沿(上升沿或下降沿)进行数据采样。

四种工作模式列成表格如下:

| SPI Mode | CPOL | CPHA |

| 0 [00] | 0 | 0 |

| 1 [01] | 0 | 1 |

| 2 [10] | 1 | 0 |

| 3 [11] | 1 | 1 |

以工作模式3为例,时序图如下:

优缺点

主从设备必须使用相同的工作模式才能正常工作。如果有多个从设备,并且它们使用了不同的工作模式,那么主设备必须在读写不同从设备时重新修改对应从设备的模式。

SPI没有规定最大传输速率,没有地址方案,也没规定通信应答机制,没有规定流控制规则。只要四根信号线连接正确,SPI模式相同,将CS/SS信号线拉低,即可以直接通信。

SPI优点在于:

- 全双工串行通信;

- 高速数据传输速率;

- 简单的软件配置;

- 数据位宽灵活,可以是任意大小的字;

SPI缺点在于:

- 没有硬件从机应答信号;

- 只允许一个主设备;

- 使用四根信号线(I2C和UART使用两根信号线)

- 没有定义错误检查协议;

- 与RS-232和CAN总线相比,只能支持非常短的距离;

verilog代码实现

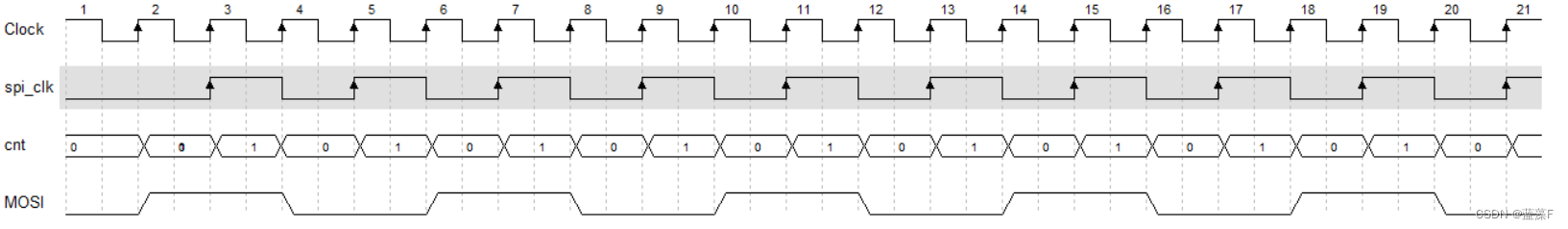

实现思路是用一个1bit计数器,假设spi_clk是系统时钟二分频,计数器每个时钟周期加1,然后发送数据线MOSI检测到计数器为1或者0时改变数据,这样就能实现数据在spi_clk时钟上升或者下降沿改变,在spi_clk时钟上升或者下降沿采样。

这个代码只简易实现了主机向从机写数据,通过MOSI口输出。如果需要地址,只需要先发送一个要写入的地址,然后再发送要写的数据。也可以加一个判断是写指令还是读指令,如果是读,就执行读操作,反之执行写操作。

`timescale 1ns / 1ps

module spi

#(

parameter P_DATA_WIDTH = 8 ,

parameter P_CPOL = 0 ,

parameter P_CPHA = 0

)(

input i_clk ,

input i_rst ,

output o_spi_clk ,

output o_spi_cs ,

output o_spi_mosi ,

input i_spi_miso ,

input i_user_op_valid ,//操作握手信号

output o_user_op_ready ,//操作握手信号

input [P_DATA_WIDTH - 1 : 0] i_user_write_data //写数据

);

reg ro_spi_clk ;

reg ro_spi_cs ;

reg ro_spi_mosi ;

reg r_run ;

reg r_run_d1 ;

reg r_spi_cnt ;

reg [P_DATA_WIDTH - 1 : 0] r_user_write_data ;

reg ro_user_op_ready ;

wire w_user_active;

assign w_user_active = i_user_op_valid & o_user_op_ready ;

assign o_spi_clk = ro_spi_clk ;

assign o_spi_cs = ro_spi_cs ;

assign o_spi_mosi = ro_spi_mosi ;

assign o_user_op_ready = ro_user_op_ready ;

assign w_run_negedge = !r_run & r_run_d1 ;

//总线运行标志

always @(posedge i_clk or posedge i_rst) begin

if(i_rst)

r_run <= 'd0;

else if(w_user_active)

r_run <= 'd1;

else

r_run <= r_run;

end

always @(posedge i_clk or posedge i_rst) begin

if(i_rst)

r_run_d1 <= 'd0;

else

r_run_d1 <= r_run;

end

//准备信号

always @(posedge i_clk or posedge i_rst) begin

if(i_rst)

ro_user_op_ready <= 'd1;

else if(w_user_active)

ro_user_op_ready <= 'd0;

else if(w_run_negedge) //run下降沿

ro_user_op_ready <= 'd1;

else

ro_user_op_ready <= ro_user_op_ready;

end

//时钟计数器

always @(posedge i_clk or posedge i_rst) begin

if(i_rst)

r_spi_cnt <= 'd0;

else if(r_run)

r_spi_cnt <= r_spi_cnt + 1;

else

r_spi_cnt <= 0;

end

//spi时钟

always @(posedge i_clk or posedge i_rst) begin

if(i_rst)

ro_spi_clk <= P_CPOL;

else if(r_run)

ro_spi_clk <= ~ro_spi_clk;

else

ro_spi_clk <= P_CPOL;

end

//片选

always @(posedge i_clk or posedge i_rst) begin

if(i_rst)

ro_spi_cs <= 'd1;

else if(w_user_active)

ro_spi_cs <= 'd0;

else if(~r_run)

ro_spi_cs <= 'd1;

else

ro_spi_cs <= ro_spi_cs;

end

//写数据

always @(posedge i_clk or posedge i_rst) begin

if(i_rst)

r_user_write_data <= 'd0;

else if(w_user_active)

r_user_write_data <= i_user_write_data;

else if( r_spi_cnt)

r_user_write_data <= r_user_write_data << 1;

else

r_user_write_data <= r_user_write_data;

end

//spi输出引脚

always @(posedge i_clk or posedge i_rst) begin

if(i_rst)

ro_spi_mosi <= 'd0;

else if(w_user_active)

ro_spi_mosi <= r_user_write_data[P_DATA_WIDTH - 1];

else if(r_spi_cnt)

ro_spi_mosi <= r_user_write_data[P_DATA_WIDTH - 1]; //串行输出数据

else

ro_spi_mosi <= ro_spi_mosi;

end

endmodule

可以看到输入数据为01010101时数据可以在第一个上升沿采样。

1613

1613

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?