输入

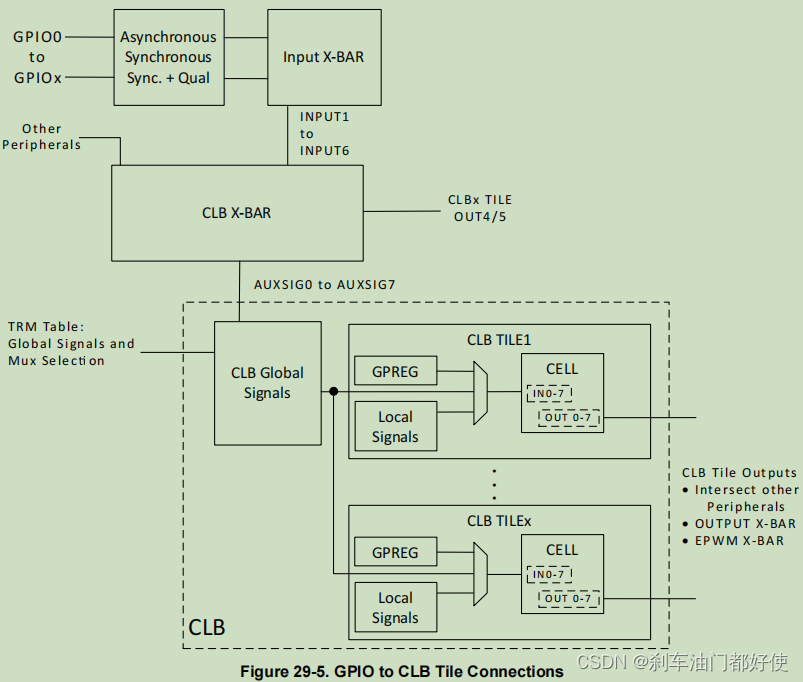

下图是CLB外部输入框图,可以经其他外设或GPIO给到CLB X-BAR,然后给到CLB模块内部。

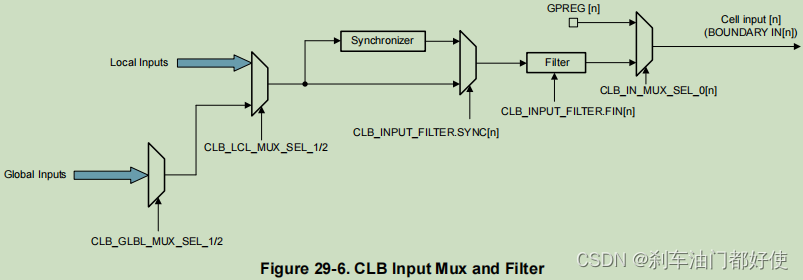

下面是CLB内部输入框图。可以看到CLB内部边界输入有3个来源:全局输入/本地输入/寄存器输入。

另外还可以选择同步/滤波等功能。

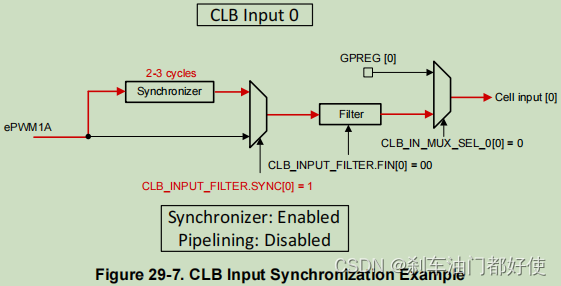

下图是信号选择的实例。

输出

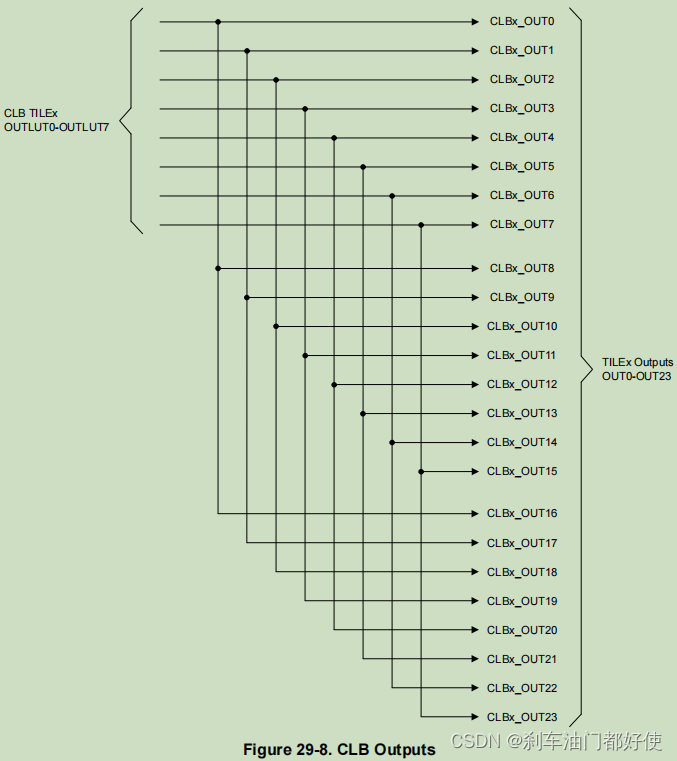

下图是CLB的输出,可以看到CLB有8个输出,然后复制3份后向外输出,共24个对外输出。

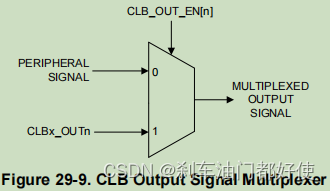

输出信号多选器

下图是多选器的示意图。默认是输出外设信号,当CLB要输出时需要使能CLB_OUT_EN[n]。

文档中有全局输入/局部输入/输出信号多选器信号3个表格,由于表格较长,就不再截图。如果需要详细了解,可以查看参考文档。

参考文档:

TMS320F28004x Real-Time Microcontrollers Technical Reference Manual (Rev. G)

520

520

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?