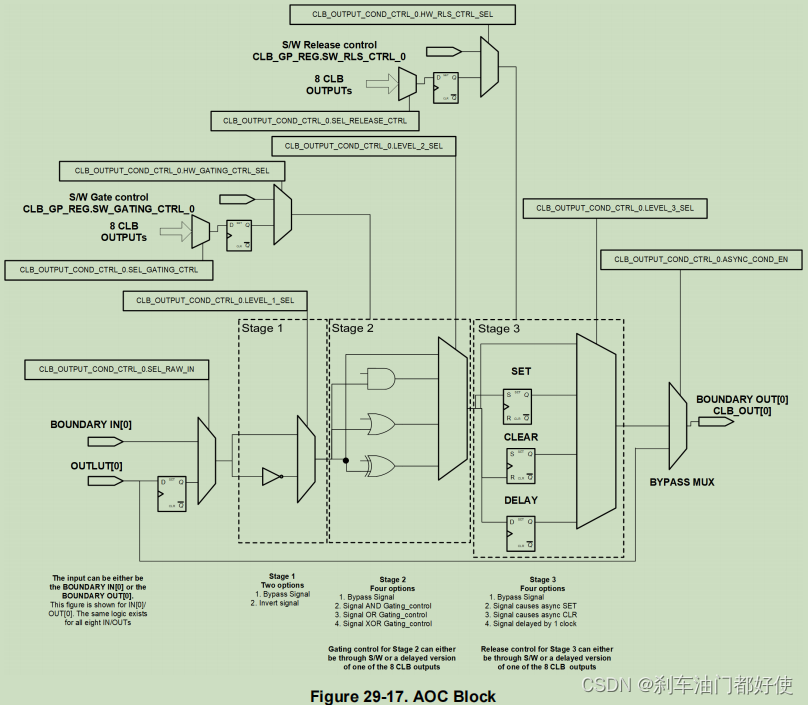

功能框图

内部功能框图如下:

aoc功能可以被bypass,它主要有3个stage。

stage1可选:

直通、取反;

stage2可选:

直通、相与、相或、异或。

逻辑操作的一个输入是stage1的输出,另一个输入是sw gating或 CLB的OUTPUT。

stage3可选:

直通、SET / CLEAR / DELAY。

delay是对stage2的输出延迟1拍。

set和clear是在stage2的输出上升沿时输出高或低。set和clear的输出可以被重置,重置信号为高时set输出低,clear输出高。重置信号可以选择sw release或CLB的OUTPUT。

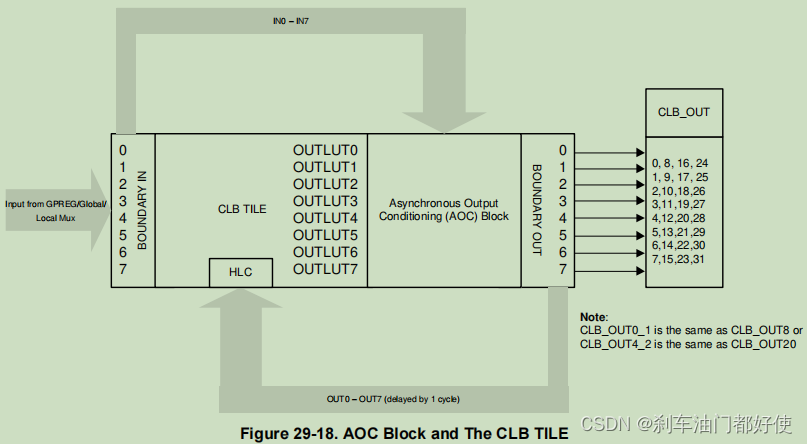

在clb中前后连接关系:

可以看到aoc模块的输入有2个:boundary in和outlut。

aoc的输出就是boundary out,可以送到CLB_OUT,也可以送到HLC子模块。

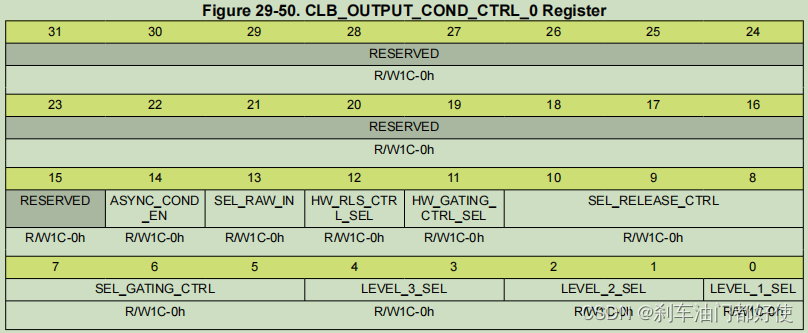

寄存器

参考文档:

TMS320F28004x Real-Time Microcontrollers Technical Reference Manual (Rev. G)

183

183

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?