做为数字后端工程师的你,一定知道整个项目的schedule是比较紧急的。有时候前端设计可能还会碰到design有bug(无法通过ECO解决),需要重新改design的情况,实际留给后端工程师的时间就更少了。因此,做为一名合格的数字后端工程师应该将整个实现流程规范化和自动化,也只有这样才能够不慌不忙高效率地完成自己所负责模块的后端实现。你是否经历过当前端release final netlist时,你还在调整floorplan,还在修改powerplan等方面的问题?

今天小编要介绍的是final netlist来之前,我们应该做好哪些工作?

1.Library检查

一般情况下,final release时不会更改design的reference library,如标准单元,memory,ip的参考库。所以,此时我们需要将所有的参考库指定为最终或者最新的library。需要特别注意的是Memory和IP的参考库,体现在ICC/ICC2中为对应的Fram view和NDM。因为Fram view 或者NDM决定了对应memory,ip的形状和出pin的位置信息。如果形状都没用对,结果只有一种情况:竹篮打水,一场空,白忙活。

ICC中查看设计参考库的命令如下:

report_mw_lib -mw_reference_library

ICC2中查看设计参考库的命令如下:

report_ref_libs

重置参考库的命令:

set_mw_lib_reference -mw_reference_library $reference_lib $design_lib_name (ICC对应命令)

set_ref_libs -ref_libs $reference_lib -library $design_lib_name(ICC2对应命令)

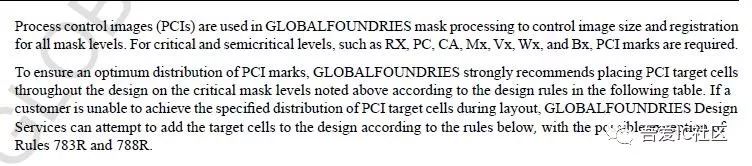

2.DRC检查

这里的DRC检查是指floorplan方面的DRC。在final netlist release前,我们很有必要再次检查final floorplan的DRC。主要是检查memory,std和ip poly 方向问题,这点在之前推送的文章“”介绍过。另外,对于还需要检查考虑ESD泄电所添加的CLAMP cell是否添加充足和fab要求添加的process校正的cell(比如TCD)是否充足。

图1 DRC检查规则

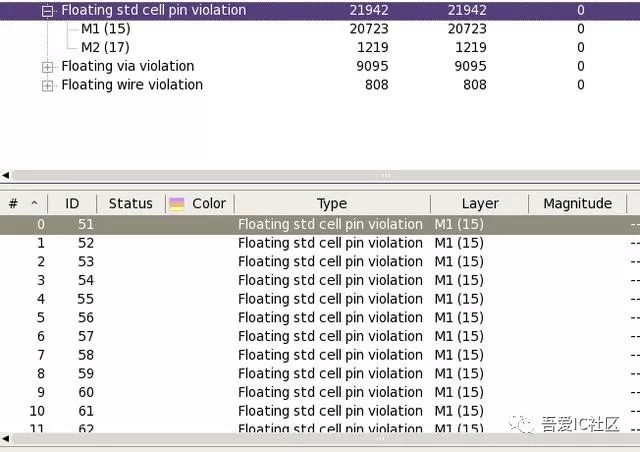

3.Powerplan检查

power strap的VIA检查。主要检查由于画power strap时脚本的不完善导致某些std cell rail 出现floating的情况,特别是memory直接小channel比较容易出现这种问题。

图2 verify_pg_nets结果

4.IR Drop检查

主要检查静态IR Drop和动态IR Drop结果是否符合signoff要求。对于wire bond的封装形式,静态IR Drop一般控制在5%以内,flip chip的封装则控制在3%以内。动态IR Drop业界一般建议压降控制在16%左右。当然IR Drop的百分比是越低越好(需要付出对应的代价,如面积)。如果发现基于当前powerplan的版本压降不符合要求,则需要尽快制定优化方案并再次分析IR drop,避免影响项目进度。

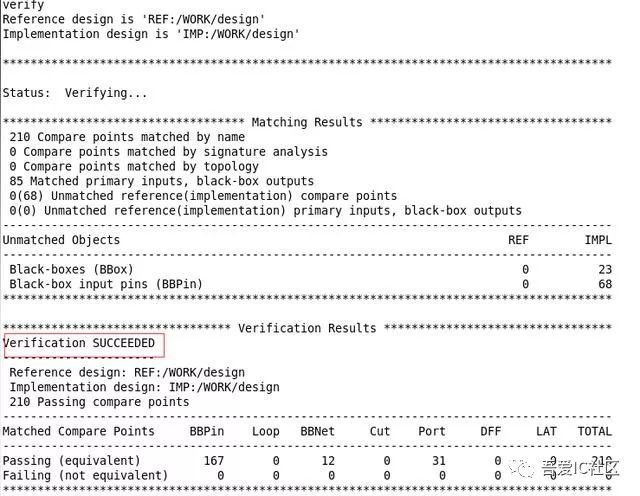

5.Formality检查

Formality的检查始终要贯穿整个实现设计实现过程。负责逻辑综合的工程师需要将自己综合后的netlist和RTL进行FM的check。对于数字后端工程师则需要将后端实现(APR自动布局布线)后post-layout netlist和综合的netlist进行FM check。如果是综合的netlist和RTL比不过,则可以从综合的参数设置和优化的选项着手debug。如果是post-layout netlist与pre-layout的netlist比不过,则可以从数字后端实现过程中检查。因为这类FM比不过,大都很难通过ECO的方式来解决,所以需要在final netlist进入PR前就应该解决FM问题。

图3 formality一致性检查结果

3221

3221

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?