题目:

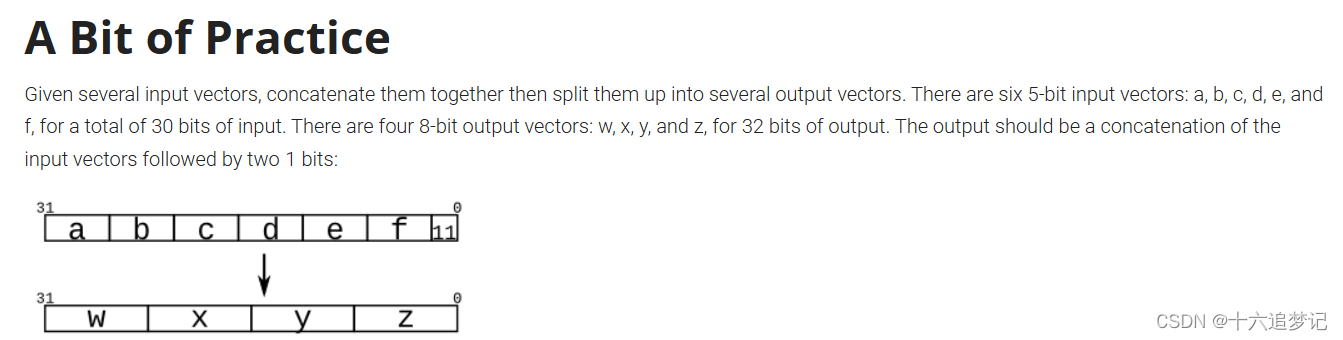

A Bit of Practice Given several input vectors, concatenate them

together then split them up into several output vectors. There are six

5-bit input vectors: a, b, c, d, e, and f, for a total of 30 bits of

input. There are four 8-bit output vectors: w, x, y, and z, for 32

bits of output. The output should be a concatenation of the input

vectors followed by two 1 bits:

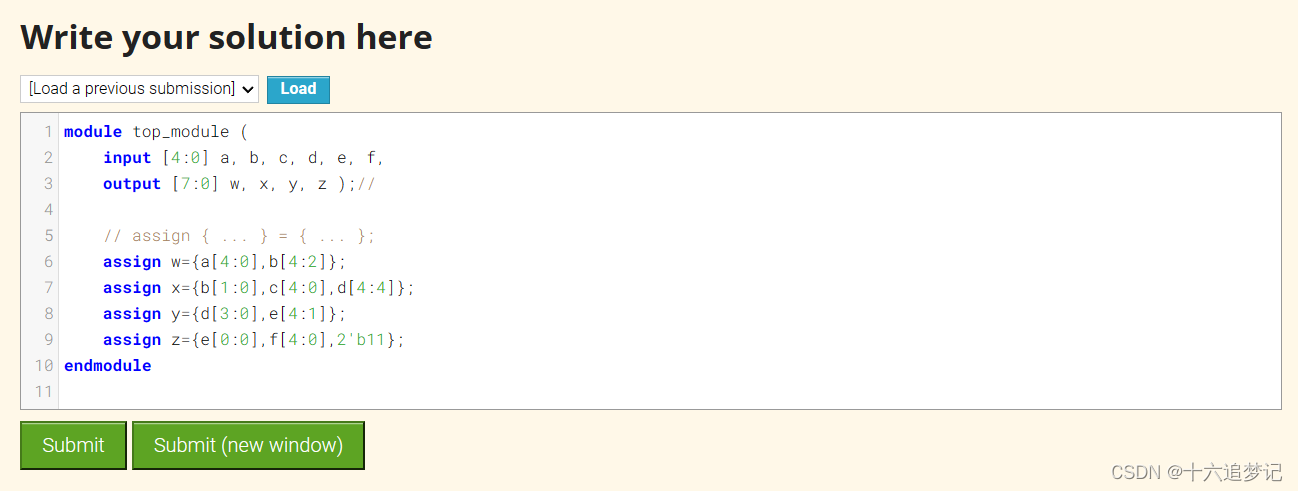

我的解法:

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );//

// assign { ... } = { ... };

assign w={a[4:0],b[4:2]};

assign x={b[1:0],c[4:0],d[4:4]};

assign y={d[3:0],e[4:1]};

assign z={e[0:0],f[4:0],2'b11};

endmodule

当后面加上11时,要写成z={e[0:0],f[4:0],2’b11}

这里也可以改成z={e[0],f,2’b11}

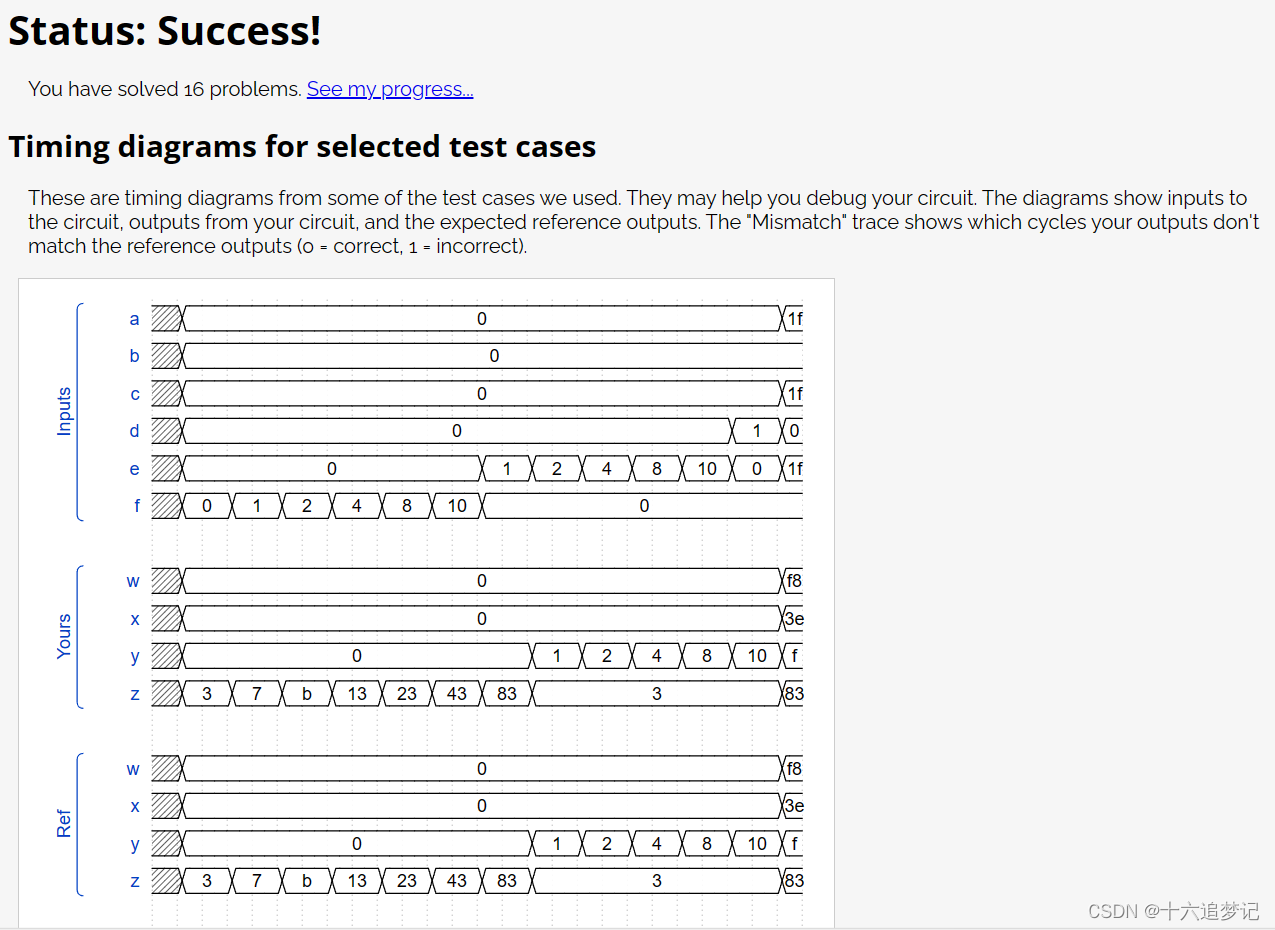

结果正确:

353

353

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?